JPEG2000中中53离散小波多层变换离散小波多层变换FPGA实现研究实现研究

本文提出了一种快速、有效的JPEG 2000 5/3小波变换的VLSI设计结构,该结构将数据的奇偶分裂、边界延拓

嵌入到地址产生单元对双端口RAM的操作中,不需要额外的计算单元,采用移位-相加操作代替卷积操作,通过

Verilog编写RTL级代码并进行功能仿真,最后完成了在FPGA上的验证,最高时钟频率达到156 MHz,整体性能

优越。

关键字:关键字:

摘要:基于新一代图像压缩国际标准JPEG 2000,介绍一种快速、有效的多层5/3小渡变换的VLSI设计结构,该方法使用两

组一维变换实现,用移位-相加代替乘法操作,整体设计采用了流水线设计。利用双端口RAM和地址生成模块的调度完成小波

变换的分裂、边界延拓工作,不需另外增加模块。二维离散小波变换滤波器结构的设计采用

关键词:JPEG 2000标准;离散小波变换;FPGA;RAM

0 引言

随着多媒体应用领域的快速发展,新一代静止图像压缩标准JPEG 2000己在2000年11月完成了标准的制定。与原有的

JPEG标准相比,JPEG 2000具有许多优势。例如更高的压缩性能,支持单分量或者多分量的有损和无损压缩,可以提供质量

和分辨率渐进传输,以及感兴趣区域编码等。典型的JPEG 2000编码中的传统的离散小波变换由卷积完成,因此在实现中需

要巨大的计算和存储量。I.Daubechies和W.Sweldens等人提出的提升算法解决了这些问题,该算法采用采用移位-相加操

作代替卷积操作,大大降低了DWT运算硬件实现的难度,因此JPEG 2000采用基于提升的DWT作为图像压缩的第一步。

JPEG 2000推荐5/3及9/7小波分别用于无损和有损压缩,本文针对5/3滤波器,提出了一种高效高速的二维三层小波变换

的硬件平台,整体结构采用流水操作。

1 离散小波提升算法

离散小波提升算法主要有三个步骤:分裂(Split)、预测(Predict)和更新(Update)。分裂是把输入信号x(n)分成奇偶两个子信

号集,即由其采样后的偶序列子信号组成xe=x(2n),奇序列子信号组成x0=x(2n+1)。预测是偶序列信号乘上一个预测参数P,

来预测奇信号,原来的奇序列信号与预测值的差即为高频系数d(n)。更新是高频系数乘以更新系数Q与偶序列信号的和,获得

低频系数s(n)。

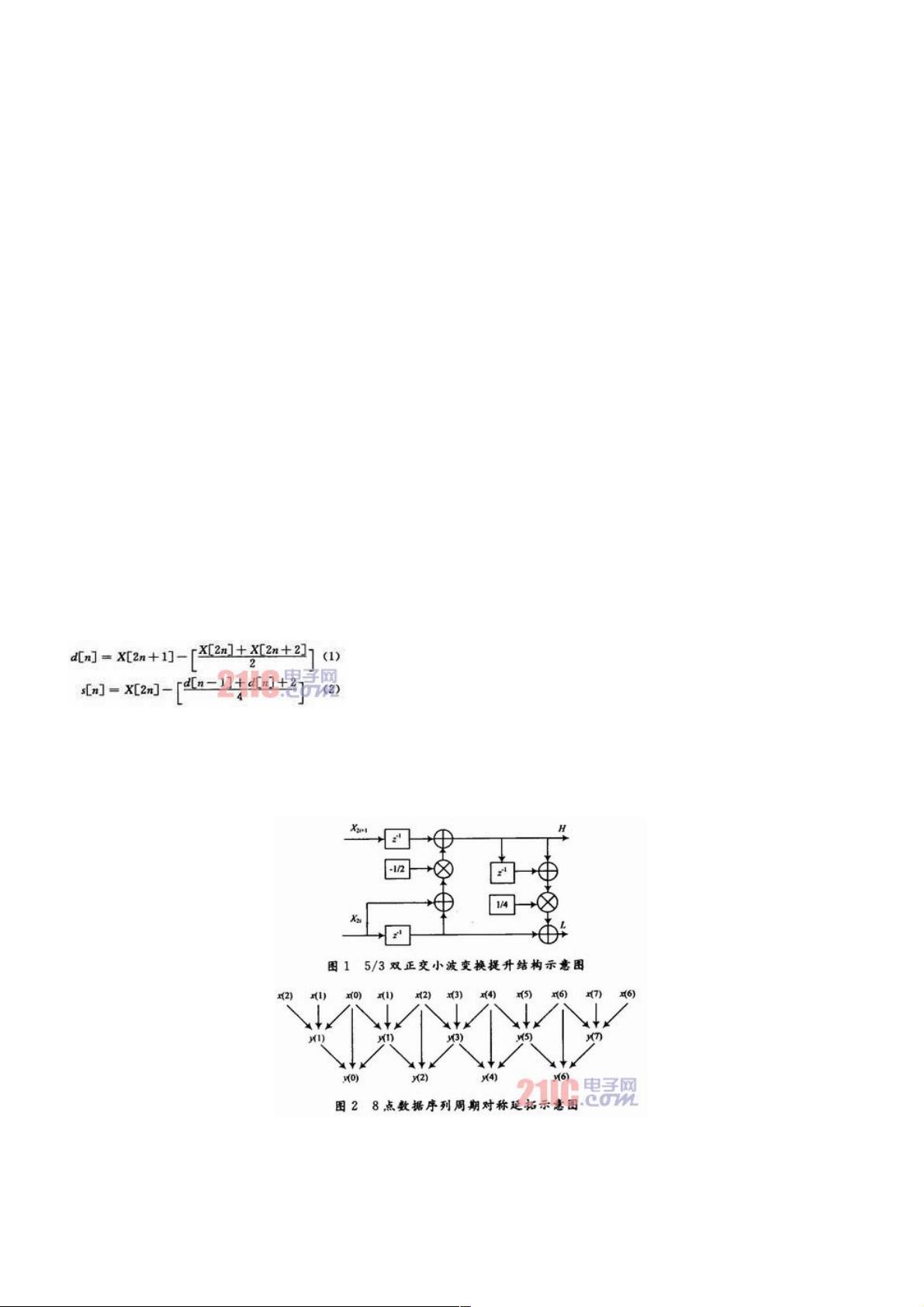

5/3双正交小波对应的提升方法如图1所示,用于JPEG 2000中的无损压缩过程,硬件实现可分为两步,如式(1),式(2)所

示:

2 5/3小波内嵌延拓提升算法

由式(1)和式(2)可以看出,在图像边界处进行小波变换时需要进行延拓处理,否则无法正确进行小波变换,对原始图像边界

数据的处理通常使用对称周期延拓方式,5/3小波变换的延拓需要在序列前延拓两个数据,在序列后延拓一个数据,图2为5

/3小波变换时8点数据序列周期对称延拓示意图。

本文是通过双端口RAM的读/写实现分裂过程,在小波变换过程中通过对读地址的操作实现对称周期性数据延拓:用对计

数器的计算操作实现边界数据延拓和生成读取地址与写入地址,从原图像中读取,经变换后写入相应的地址,以8×8图像为

例,行方向上延拓后的读取地址顺序应该是2,1,0,1,2,3,4,5,6,7,6,10,9,8,9,10,…;列方向上延拓后读

取地址顺序是16,8,0,8,16,24,32,40,48,56,48,17,9,…。

3 硬件设计