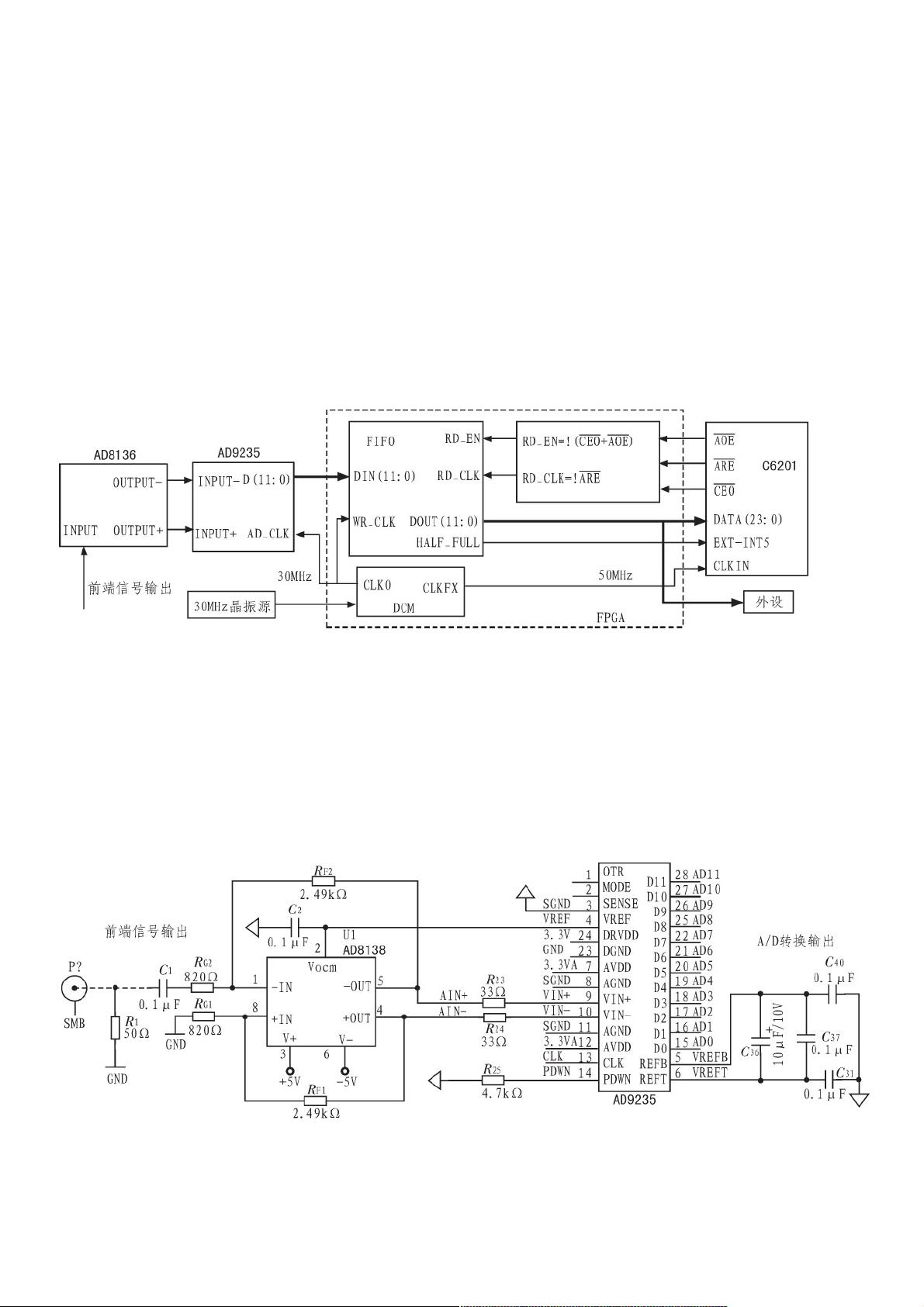

激光雷达的发射波及回波信号经光电器件转换形成的电信号具有脉宽窄,幅度低,背景噪声大等特点,对其进行低速数据采集存在数据精度不高等问题。同时,A/D转换器与数字信号处理器直接连接会导致数据传输不及时,影响系统可靠性、实时性。针对激光雷达回拨信号,提出基于FPGA与DSP的高速数据采集系统,利用FPGA内部的异步FIFO和DCM实现A/D转换器与DSP的高速外部存储接口(EMIF)之间的数据传输。介绍了ADC外围电路、工作时序以及DSP的EMIF的设置参数,并对异步FIFO数据读写进行仿真,结合硬件结构详细地分析设计应注意的问题。系统采样率为30 MHz,采样精度为12位。 【基于FPGA+DSP的雷达高速数据采集系统实现】针对激光雷达回波信号的特性,传统的低速数据采集系统存在精度不足的问题。由于激光雷达信号的脉宽窄、幅度低和高背景噪声,直接采用A/D转换器与数字信号处理器(DSP)连接,可能导致数据传输延迟,影响系统可靠性和实时性。因此,设计了一个基于FPGA(Field-Programmable Gate Array)和DSP的高速数据采集系统,以解决这些问题。 该系统的核心在于利用FPGA内部的异步FIFO(First-In-First-Out)和时钟管理器(DCM)来实现A/D转换器与DSP之间的高速数据传输。A/D转换器将接收到的模拟信号转换为数字信号,然后通过FPGA的异步FIFO将这些数据暂存,以匹配不同速度的DSP EMIF(External Memory Interface)。FIFO作为数据缓冲区,确保数据在不同时钟域之间的无缝传输,防止数据丢失。 在硬件设计中,选择了AD9235作为A/D转换器,它具备40 Mb/s的采样率和12位的分辨率,适合处理高带宽、低噪声的信号。为适应AD9235的差分输入,采用了AD8138作为A/D驱动芯片,将单端信号转换为差分信号并进行适当的放大。 FPGA内部的DCM用于生成不同频率的时钟,以满足不同部件的需求。例如,为AD9235提供30 MHz的采样时钟,同时为TMS320C6201 DSP生成50 MHz的时钟,通过4倍频使DSP的系统时钟达到200 MHz,以支持高速数据处理。 在FPGA接口设计中,时序控制是关键。A/D转换器的采样时钟与FIFO的写时钟同步,确保数据能及时写入FIFO。而DSP则以更快的FIFO读时钟读取数据,以满足实时性要求。FIFO的读写时序经过精心设计,确保在不同时钟域下稳定运行,同时考虑到建立时间和保持时间的要求。 这个基于FPGA+DSP的高速数据采集系统能够有效地处理激光雷达信号,提高数据采集的精度和实时性,降低数据丢失的风险。通过优化硬件设计和时序控制,实现了30 MHz的采样率和12位的采样精度,满足了雷达数据处理的高速需求。这一方案在电子竞赛和数据采集与处理类项目中具有很高的应用价值。

- 粉丝: 3

- 资源: 945

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功