没有合适的资源?快使用搜索试试~ 我知道了~

Intel至强处理器MP是基于Intel NetBurst微体系结构的。在Intel至强处理器MP商标名下现有两个处理器家族:第一个处理器家族的现有速度从1.40GHz到1.60GHz,并且有256KB二级高速缓存和512KB或1MB三级高速缓存,这一至强处理器MP家族使用0.18微米制程制造。Intel至强处理器MP的第二个处理器家族的速度高达3GHz,该处理器家族拥有512KB二级高速缓存和1MB、2MB或4MB的三级高速缓存,使用0.13微米制程制造。

资源推荐

资源详情

资源评论

Voltage Regulator Module (VRM)

and Enterprise Voltage

Regulator-Down (EVRD) 10.1

Design Guidelines

March 2005

Document Number: 302732-003

2 Voltage Regulator Module (VRM) and Enterprise Voltage

Regulator-Down (EVRD) 10.1 Design Guidelines

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or

in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel

®

Xeon™ processor and 64-bit Intel

®

Xeon™ processor MP may contain design defects or errors known as errata that may cause the product to

deviate from published specifications. Current characterized errata are available on request.

Intel, Intel Xeon, Pentium and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and

other countries.

∆

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across

different processor families. See www.intel.com/products/processor_number

for details.

* Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation.

Voltage Regulator Module (VRM) and Enterprise Voltage 3

Regulator-Down (EVRD) 10.1 Design Guidelines

Contents

1 Applications........................................................................................................................7

1.1 Introduction and Terminology ..............................................................................................7

2 Output Voltage Requirements............................................................................................9

2.1 Voltage and Current - REQUIRED.......................................................................................9

2.2 Load Line Definitions - REQUIRED ...................................................................................10

2.3 Voltage Tolerance - REQUIRED........................................................................................11

2.4 Processor Vcc Overshoot - REQUIRED............................................................................12

2.5 Stability - REQUIRED ........................................................................................................12

2.6 Processor Power Sequencing - REQUIRED .....................................................................12

2.7 Dynamic Voltage Identification (VID) - REQUIRED ...........................................................14

2.8 Overshoot at Turn-On or Turn-Off - REQUIRED ...............................................................15

2.9 Output Filter Capacitance - REQUIRED ............................................................................15

2.10 Shut-Down Response - REQUIRED..................................................................................17

3 Control Signals.................................................................................................................19

3.1 Output Enable (OUTEN) - REQUIRED..............................................................................19

3.2 Voltage Identification (VID [5:0]) - REQUIRED ..................................................................19

3.3 Differential Remote Sense (VO_SEN±) - REQUIRED.......................................................21

3.4 Load Line Select (LL0, LL1) - REQUIRED.........................................................................21

4 Input Voltage and Current ................................................................................................23

4.1 Input Voltages - EXPECTED .............................................................................................23

4.2 Load Transient Effects on Input Current - EXPECTED .....................................................23

5 Processor Voltage Output Protection...............................................................................25

5.1 Over-Voltage Protection (OVP) - PROPOSED..................................................................25

5.2 Over-Current Protection (OCP) - PROPOSED ..................................................................25

6 Output Indicators..............................................................................................................27

6.1 Power Good (Vcc_PWRGD) - PROPOSED ......................................................................27

6.2 Voltage Regulator Hot (VR_hot#) - PROPOSED...............................................................27

6.3 Load Indicator Output (Load Current) - PROPOSED ........................................................28

6.4 VRM Present (VRM_pres#) - EXPECTED.........................................................................28

7 VRM – Mechanical Guidelines .........................................................................................29

7.1 VRM Connector - EXPECTED...........................................................................................29

7.2 VRM Connector Keying .....................................................................................................29

7.2.1 Connector Keying................................................................................................29

7.2.2 Connector Pin 1 Orientation ................................................................................29

7.3 Pin Descriptions and Assignments ....................................................................................30

7.4 Mechanical Dimensions - PROPOSED .............................................................................32

7.4.1 Gold Finger Specification ....................................................................................32

8 VRM – Environmental Conditions ....................................................................................35

8.1 Operating Temperature - PROPOSED ..............................................................................35

8.2 VRM Board Temperature - REQUIRED.............................................................................35

8.3 Non-Operating Temperature - PROPOSED ......................................................................35

8.4 Humidity - PROPOSED .....................................................................................................35

4 Voltage Regulator Module (VRM) and Enterprise Voltage

Regulator-Down (EVRD) 10.1 Design Guidelines

8.5 Altitude - PROPOSED....................................................................................................... 35

8.6 Electrostatic Discharge - PROPOSED.............................................................................. 36

8.7 Shock and Vibration - PROPOSED .................................................................................. 36

8.8 Electromagnetic Compatibility - PROPOSED ................................................................... 36

8.9 Reliability - PROPOSED ................................................................................................... 36

8.10 Safety - PROPOSED ........................................................................................................ 36

9 Manufacturing Considerations .........................................................................................37

9.1 Lead Free (Pb Free)..........................................................................................................37

Figures

2-1 VRM/EVRD 10.1 Load Current vs. Time............................................................................. 9

2-2 VRM/EVRD 10.1 Processor Die Load Line....................................................................... 10

2-3 Processor Vcc Overshoot Example Waveform ................................................................. 12

2-4 Power-On Sequence Block Diagram ................................................................................ 13

2-5 Power-On Sequence Timing Diagram .............................................................................. 13

2-6 Processor Transition States.............................................................................................. 14

2-7 Dynamic VID Transition States Illustration........................................................................ 15

2-8 Model of Processor Load .................................................................................................. 16

7-1 VRM 10.1 Module and Connector..................................................................................... 33

Tables

2-1 LL0, LL1 Codes................................................................................................................. 11

2-2 Recommended Decoupling and Other Specifications....................................................... 16

2-3 VRM 10.1 Decoupling Capacitor Recommendations........................................................ 17

3-1 OUTEN Specifications ...................................................................................................... 19

3-2 VID [5:0] Specifications.....................................................................................................19

3-3 Voltage Identification (VID) ............................................................................................... 20

3-4 LL0, LL1 Specifications ..................................................................................................... 21

6-1 Vcc_PWRGD Specifications ............................................................................................. 27

6-2 VR_hot# Specifications ..................................................................................................... 27

6-3 VRM_pres Specifications .................................................................................................. 28

7-1 VRM10.1 Connector Part Number and Vendor Name ...................................................... 29

7-2 VRM 10.1 Connector Pin Descriptions.............................................................................. 30

7-3 VRM 10.1 Pin Assignments .............................................................................................. 31

Voltage Regulator Module (VRM) and Enterprise Voltage 5

Regulator-Down (EVRD) 10.1 Design Guidelines

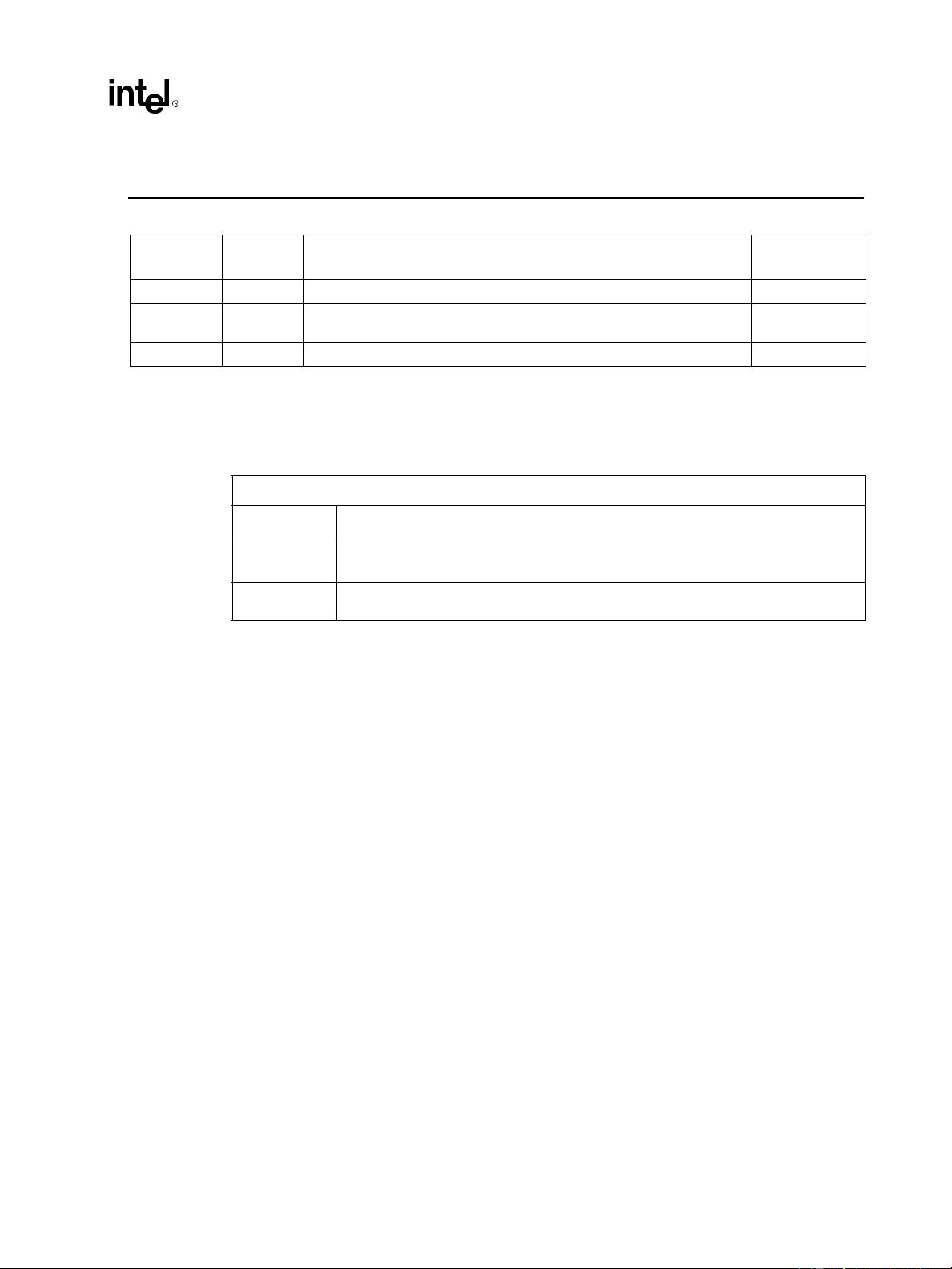

Revision History

NOTE: Not all revisions may be published.

§

Document

Number

Revision

Number

Description Date

302732 001 • Initial release June 2004

302732 002 • Updated release to include 64-bit Intel

®

Xeon™ processor with 2 MB L2

cache launch

February 2005

302732 003 • Incorporated 64-bit Intel

®

Xeon™ processor MP March 2005

Guideline Categories

REQUIRED:

An essential part of the design – necessary to meet processor voltage and current

specifications and follow processor layout guidelines.

EXPECTED:

Part of Intel’s processor power definitions; necessary for consistency among the designs of

many systems and power devices. May be specified or expanded by system OEMs.

PROPOSED:

Normally met by this type of DC-to-DC converter and, therefore, included as a design

target. May be specified or expanded by system OEMs.

剩余37页未读,继续阅读

资源评论

weixin_38705723

- 粉丝: 5

- 资源: 917

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功