没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

Product-level Reliability of GaN Devices

Sandeep R. Bahl, Daniel Ruiz and Dong Seup Lee*

Texas Instruments

2900 Semiconductor Dr. Santa Clara, CA 95052

*13121 TI Blvd, Dallas, TX 75243

Abstract—To enable the widespread adoption of GaN products,

the industry needs to be convinced of product-level reliability.

The difficulty with product-level reliability lies with the diverse

range of products and use conditions, a limited ability for

system-level acceleration, and the complication from non-GaN

system failures. For power management applications, however,

it is possible to identify fundamental switching transitions. This

allows the device to be qualified in an application-relevant

manner. In this paper, we explain how hard-switching can form

a fundamental switching transition for power management

products. We further show that the familiar double-pulse tester

is a good hard-switching qualification test vehicle. The

methodology is explained in the context of the existing

qualification framework for silicon transistors.

Index Terms—Gallium nitride, life testing, power conversion,

power transistors, semiconductor device reliability

I. INTRODUCTION

The industry now takes the reliability of silicon transistors

for granted, as evidenced by their widespread use in products.

This is a result, not only of longstanding experience, but also

of the development of credible reliability and qualification

methodology. Technology is qualified by running

standardized stress tests [1]-[3], and by validating lifetime

requirements [4]. This methodology originated from detailed

work on the understanding of failure modes, their acceleration

and modeling, and a statistical framework to assure a

minimum level of quality.

The stress tests, however, were developed more than

twenty years ago, with the Joint Electron Device Engineering

Council (JEDEC) JESD47 document released in 1995 and the

Automotive Electronics Council (AEC) founded in 1994. The

qualification procedure has remained essentially unchanged

over the years, whereas technology and its uses have changed.

For example, power conversion circuitry using hard-switched

transistors is now much more widespread. There is also

tremendous interest in emerging materials like GaN and SiC

for power management applications.

Transistors from emerging materials are being judged as

“passing qual” when run through the standardized stress tests

described in [1]-[3]. While the standard silicon-based

qualification recipe is a worthy manufacturing, quality and

reliability milestone, it is not clear what it means for emerging

transistors in terms of device lifetime, failure rates and

application-relevance. This is because the failure modes,

activation energies, and acceleration factors are likely to be

different than those used for Si. In addition, the reliability test

conditions may not be representative of the product use-case

so may not accelerate valid failure mechanisms.

For successful technology adoption, it is important to

develop credible reliability and qualification methodology. A

successful methodology allows the industry to gain confidence

that parts will last for the desired lifetime in the end-use

application without many customer returns. It also allows

users to easily benchmark components and suppliers.

II. WHAT DOES QUALIFICATION MEAN?

Traditional qualification testing [1]-[3] or “qual” involves

many tests, which may be classified into three categories:

device, package, and electrostatic discharge (ESD). In this

paper, we focus on device-relevant testing. In order for the

industry to develop GaN-specific methodology, it is important

to understand the fundamentals and assumptions behind

traditional qualification. It is also important to know what

“passing qual” means. The knowledge may be summarized in

the form of the three questions below:

A. How long is the device qualified for?

This is typically perceived to be 10 years

*

. The calculation

arises by running a 1000h test at a junction temperature of

125°C and extrapolating to a use-temperature of 55°C with an

activation energy of 0.7 eV. Additionally, discrete FETs are

commonly qualified at 80% of the minimum breakdown

voltage, e.g. a 600V FET is qualified at 480V. The 80% value

is common practice and not specified by present standards

†

.

The ten-year assumption falls apart for power FETs, even

those made from Si. Several scenarios are calculated in [6].

The typical use-temperature of power FETs is about 100-

110°C. If qualification is run at 150°C, then the non-

accelerated time for use at 105°C is only 1.1 yrs, far short of a

ten year lifetime. Further, thermal acceleration for silicon

assumes an activation energy of 0.7 eV, whereas activation

energies for GaN are likely to be different. Recent power GaN

literature shows a wide range [7]-[13], from 0.1 eV to 1.84

eV. Voltage acceleration is also used [11],[14]. The variation

is expected, due to different failure modes and architectures.

Indeed, power GaN transistors comprise both depletion and

enhancement mode (d- and e-mode) FETs. Further, d-mode

FETs are Schottky [9] or Insulated-gate [12] and are either

cascoded with a low-voltage Si FET [12] or an IC [15] for

*

The traditional calculation results in nine years [1].

†

The current documentation [3] specifies qualification at the maximum rated

DC reverse voltage. An 80% criteria exists in historical documentation [5]

© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including

reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any

copyrighted component of this work in other works.

Presented at the IEEE International Reliability Physics Symposium (IRPS), Apr. 2016. (Invited paper)

failsafe reasons. E-mode architectures are either junction-gate

[11],[16],[17] or recessed insulated-gate [18].

B. Is the stress-testing representative of actual usage?

Traditional qualification testing does not consider the

switching conditions of power management. High-

Temperature Reverse Bias (HTRB) and High Temperature

Gate Bias (HTGB) are static tests. High Temperature

Operating Life (HTOL) is configured to bias operating nodes

and is typically applied on logic and memory devices [19].

Confidence has been built in the qualification methodology for

Si devices over the years. This is because the long-standing

experience has resulted in a detailed understanding of failure

modes, the device design knowledge to avoid them, and the

development of proxy tests e.g. substrate current monitoring

for Hot-Carrier Injection (HCI) robustness [20]. For emerging

technologies, however, switching robustness needs to be

proven by running the device under actual-use conditions.

C. Will there be many field-failures?

Passing qualification with silicon assumptions means that the

lot-tolerant percent defective (LTPD) value is one [1] and

failure in time (FIT) rate is established to be less than about 50

(60% confidence level) [21]. The LTPD calculation arises

from the statistics of zero fails out of 231 (3 lots x 77) parts.

LTPD=1 means that one can state with 90 percent confidence

that less than one percent of the parts in a lot will fail when

run for the non-accelerated time. The FIT rate calculation

arises from the total number of non-accelerated device hours.

In practice, for mature processes, the pooling of multiple

qualification runs increases the total number of parts and

device hours, allowing lower FIT rate and LTPD projections.

In order to get accurate statistics, the acceleration factor needs

to be determined for GaN, and the testing needs to be

predictive of actual-use conditions. The acceleration factor is

also used in early failure testing (ELFR) [1],[22], which is

used to assess the infant mortality rate.

III. APPLICATION-RELEVANT QUALIFICATION

Both JEDEC and AEC standards are based on sound

fundamentals, but lag technology introduction. For example,

the discrete power metal-oxide semiconductor field-effect

transistor (MOSFET) was developed in the late 1970s [23],

but it was not until the early 1990s that JEDEC developed a

qualification standard. A standard is not needed to make

technology reliable. It is a deep understanding of the

technology; its failure modes; and knowledge of testing,

qualification and product operation.

The qualification standards [1]-[3] are stress-based,

consisting of documented, standardized procedures that

prescribe accelerated test conditions. New technology

qualification adds a knowledge-based approach, summarized

in Fig. 1. This builds upon the existing framework by adding

testing and lifetime modeling for GaN specific failure modes,

e.g. dynamic on-resistance (dRon) degradation. It also adds

new stress tests, to represent application-use.

GaN has shown great promise in many power conversion

topologies, e.g. buck and boost converters, bridgeless PFC

circuits, inverters, LLC converters etc. The question arises as

to how GaN would be qualified for all these end applications.

Although JEDEC specifies the need for dynamic testing, it

does not prescribe conditions, citing the ever-evolving

applications and material sets in our industry [24]. It is not

straightforward to assure product-level reliability in a broad

sense. In addition to application diversity, products contain

many non-GaN parts and the system is not typically designed

for accelerated testing, or for running in an oven at 150°C.

Running product reliability under accelerated conditions

would cause many non-GaN failures, making it difficult to

extract useful information. Another difficulty is the energy

requirement. In order to run many power converters, one

would need to dissipate tens of thousands of watts.

One approach to this problem is to identify an application

stress condition common to a class of devices. For example,

JESD226 [25] takes such an approach for power amplifier

modules (PAMs). The documentation states “This method is

intended to refine and focus the myriad of biasing options

down to a standard that can be applied industry-wide so that

users of PAMs can gain confidence that devices successfully

completing this test method will exhibit adequate reliability

for the anticipated use conditions”.

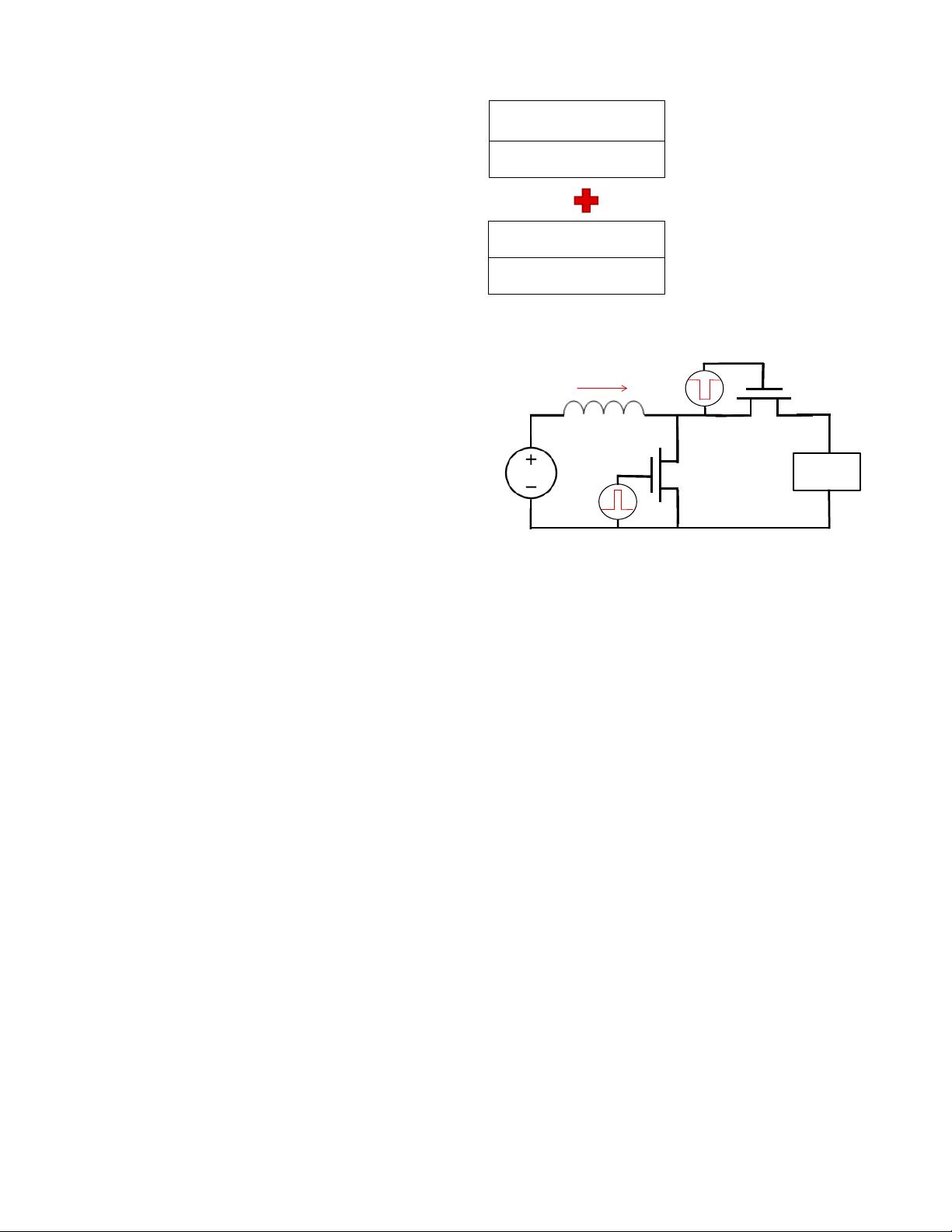

There is a large class of power management products that

place similar stresses on the power transistor. To illustrate,

consider the hard-switched boost converter schematic in Fig.

2. Teaching waveforms for both the high and low side FETs

are shown in Fig. 3, and the different operating regions are

described in Table 1. Table 1 also lists the bias stress on each

FET. As can be seen, the devices need to withstand the

following five types of stresses:

Established framework for Si

qualification and reliability

Extension for GaN – Failure

modes, lifetime extrapolation

Actual-use condition for

power management

JESD94B: Application-specific

qualification using knowledge-based

test methodology

JESD 226: An application relevant

example: RF bias life stress (RFBL)

for power amplifier modules

e.g. JESD47, AEC-Q100, Q101

Based upon methodology in e.g.

JESD22-A108D and JEP122G

Failure modes, lifetime

extrapolation

Figure 1: Qualification framework for GaN, built upon JEDEC

documentation. The silicon framework is extended for GaN-specific failure

modes and application-relevant testing is added.

Ga

GaN

FET1

Load

Ga

GaN

FET2

V

IN

I

L

Figure 2: Boost-converter schematic

剩余6页未读,继续阅读

资源评论

weixin_38689551

- 粉丝: 9

- 资源: 918

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 微控制器固件包_STM32CubeG0_1741142084.zip

- 《ARM9嵌入式系统设计基础教程》第13章图形用户接口(GUI).ppt

- 《机械设计基础》课后习题答案

- C#调用Ni板卡进行实现采集任务(模拟量输入输出)示例2

- 《实验一 Java开发环境&语法基础》

- 2016级河南大学计算机与信息工程学院创新实践计划-消防机器人.zip

- Java课程设计-学生成绩管理系统-Swing+MySQL.zip

- 《AE影视后期特效制作实例教程》8-3++空中气流写字字帖.ppt

- Unwrap Pro是一个3ds Max插件,可以在产生低失真,无重叠,加权密度的UVs的同时展开网格,而不像3ds Max Peel命令,它产生具有高面积失真的重叠UV,UnwrapPro是非常快的

- 大二下SQL实验学生信息系统.zip

- macd指标算法 php语言编写 大智慧/同花顺 数据一致

- 2025修复版绿色全自适应php核心制作的邮编查询网整站源码带百万数据+定时触发更新

- 人工智能&深度学习:PyTorch 图像识别实战 - 卷积神经网络与模块应用资源(源码+数据集+说明资料)

- 《Java语言编程基础立体化实用教程》2-6+成绩增加和成绩修改窗体的实现.ppt

- ITECH艾德克斯交直流程控源使用手册

- 实时操作系统_FreeRTOS_内核组件_通用与特定_1741145229.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功