没有合适的资源?快使用搜索试试~ 我知道了~

单片机与DSP中的用AD9850激励的锁相环频率合成器

2 下载量 47 浏览量

2020-12-08

23:58:31

上传

评论 1

收藏 170KB PDF 举报

温馨提示

试读

3页

摘 要: 提出了一种DDS和PLL相结合的频率合成方案,介绍了DDS芯片AD9850的基本工作原理、性能特点及引脚功能,给出了以AD9850作为参考信号源的锁相环频率合成器实例,并对该频率合成器的硬件电路和软件编程进行了简要说明。关键词: DDS 锁相环 频率合成器 数据寄存器 以DDS(直接数字合成)激励的PLL(锁相环)频率合成器,是用DDS作为参考信号源,将DDS和PLL组合在一起的一种独特的频率合成器方案。它综合了DDS和PLL频率合成器的优点,具有极高的频率分辨率、极短的换频时间和较好的噪声性能,而且频率范围宽、控制灵活,是应用于雷达、通信等领域中的一种较为先进的频率合成

资源推荐

资源详情

资源评论

单片机与单片机与DSP中的用中的用AD9850激励的锁相环频率合成器激励的锁相环频率合成器

摘 要: 提出了一种DDS和PLL相结合的频率合成方案,介绍了DDS芯片AD9850的基本工作原理、性能特点及

引脚功能,给出了以AD9850作为参考信号源的锁相环频率合成器实例,并对该频率合成器的硬件电路和软件编

程进行了简要说明。关键词: DDS 锁相环 频率合成器 数据寄存器 以DDS(直接数字合成)激励的PLL(锁相环)

频率合成器,是用DDS作为参考信号源,将DDS和PLL组合在一起的一种独特的频率合成器方案。它综合了

DDS和PLL频率合成器的优点,具有极高的频率分辨率、极短的换频时间和较好的噪声性能,而且频率范围宽、

控制灵活,是应用于雷达、通信等领域中的一种较为先进的频率合成

摘 要: 提出了一种DDS和PLL相结合的频率合成方案,介绍了DDS芯片AD9850的基本

工作原理、性能特点及引脚功能,给出了以AD9850作为参考信号源的锁相环频率合成器

实例,并对该频率合成器的硬件电路和软件编程进行了简要说明。

关键词: DDS 锁相环 频率合成器 数据寄存器

以DDS(直接数字合成)激励的PLL(锁相环)频率合成器,是用DDS作为参考信号源,将

DDS和PLL组合在一起的一种独特的频率合成器方案。它综合了DDS和PLL频率合成器的

优点,具有极高的频率分辨率、极短的换频时间和较好的噪声性能,而且频率范围宽、

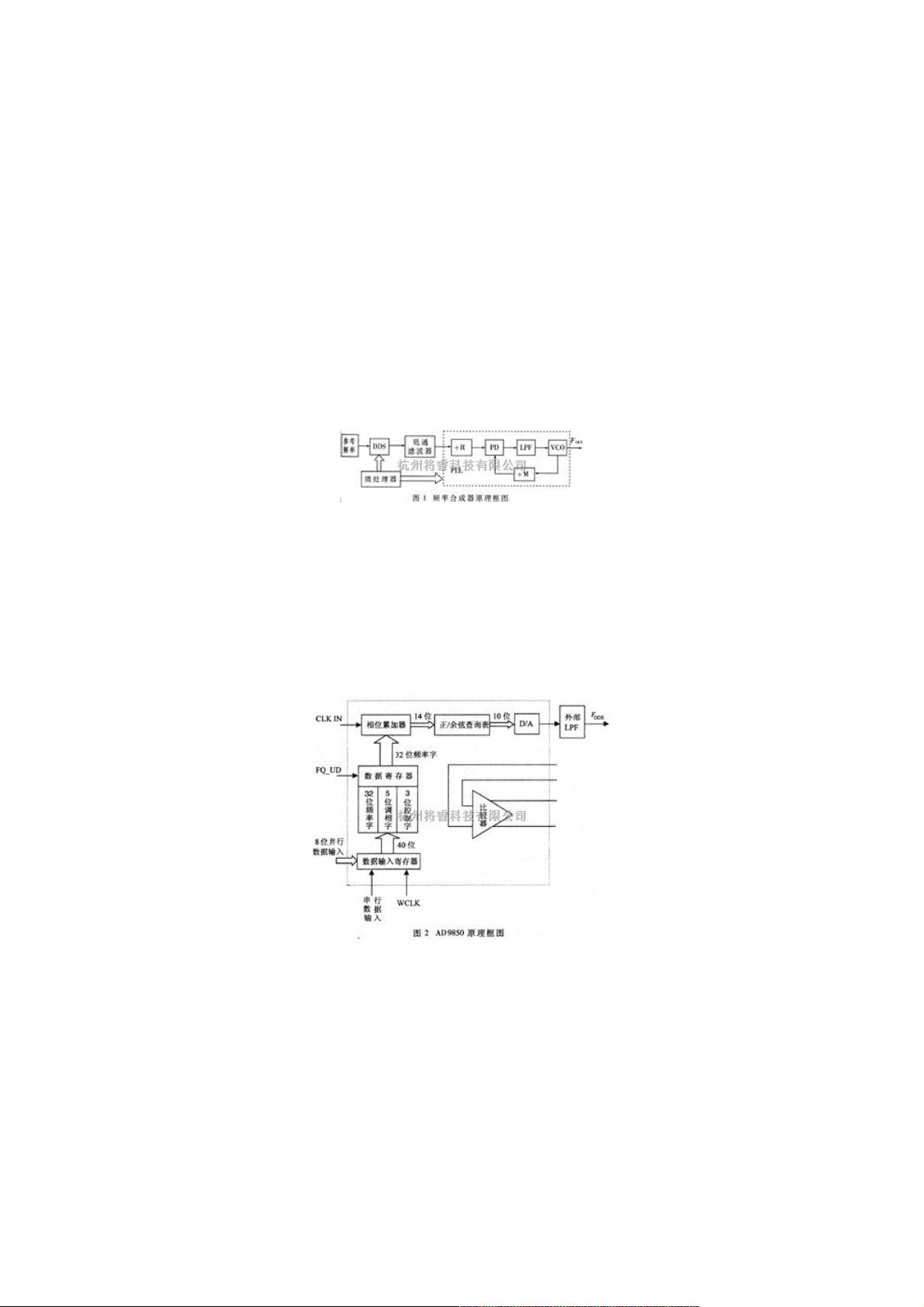

控制灵活,是应用于雷达、通信等领域中的一种较为先进的频率合成方案。其电路原理

框图如图1所示。

我们在实际工作中,以美国AD公司生产的DDS芯片AD9850和MITEL公司的PLL芯片

SP8858为核心,完成了一款高性能的DDS+PLL的频率合成器的设计与试验,并将其应

用于一无线测量接收机中,收到了极好的效果。下面介绍AD9850的基本工作原理和引脚

功能等,并给出频率合成器实例的方案组成。

1 AD9850的工作原理与引脚功能

1.1 基本工作原理

AD9850采用先进的DDS技术,在内部集成了32位相位累加器、14 位正/余弦查询表和高

性能的10位D/A转换器以及一个高速比较器,其原理框图见图2。

它通过并口或串口写入的频率控制字来设定相位累加器的步长大小,相位累加器输出的

数字相位通过查找正/余弦查询表得到所需频率信号的采样值,然后通过D/A变换,输出

所需频率的正弦波信号。还可以通过高速比较器将该正弦波信号转换成方波,作为时钟

信号输出。

输出信号的频率FDDS由下式确定:

FDDS=△f·FCLK/232(1)

式中,△f为32位频率控制字的值,FCLK为工作时钟。

1.2 控制方式

AD9850内部的5个8位寄存器构成一个40位的数据寄存器,储存来自外部数据总线的数

据和控制字,其中32位为频率控制字、5位为相位调制字、1位是电源休眠(power down)

功能控制,另2位储存工厂保留码(用户编程时,应将其设定为"00")。寄存器可通过并行

或串行方式装载。

并行方式是在使能信号FQ_UD和写脉冲WCLK的控制下,通过8位数据总线D0~D7分五

次来完成全部40位数据的输入,其工作时序图见图3。

资源评论

weixin_38660295

- 粉丝: 6

- 资源: 911

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功