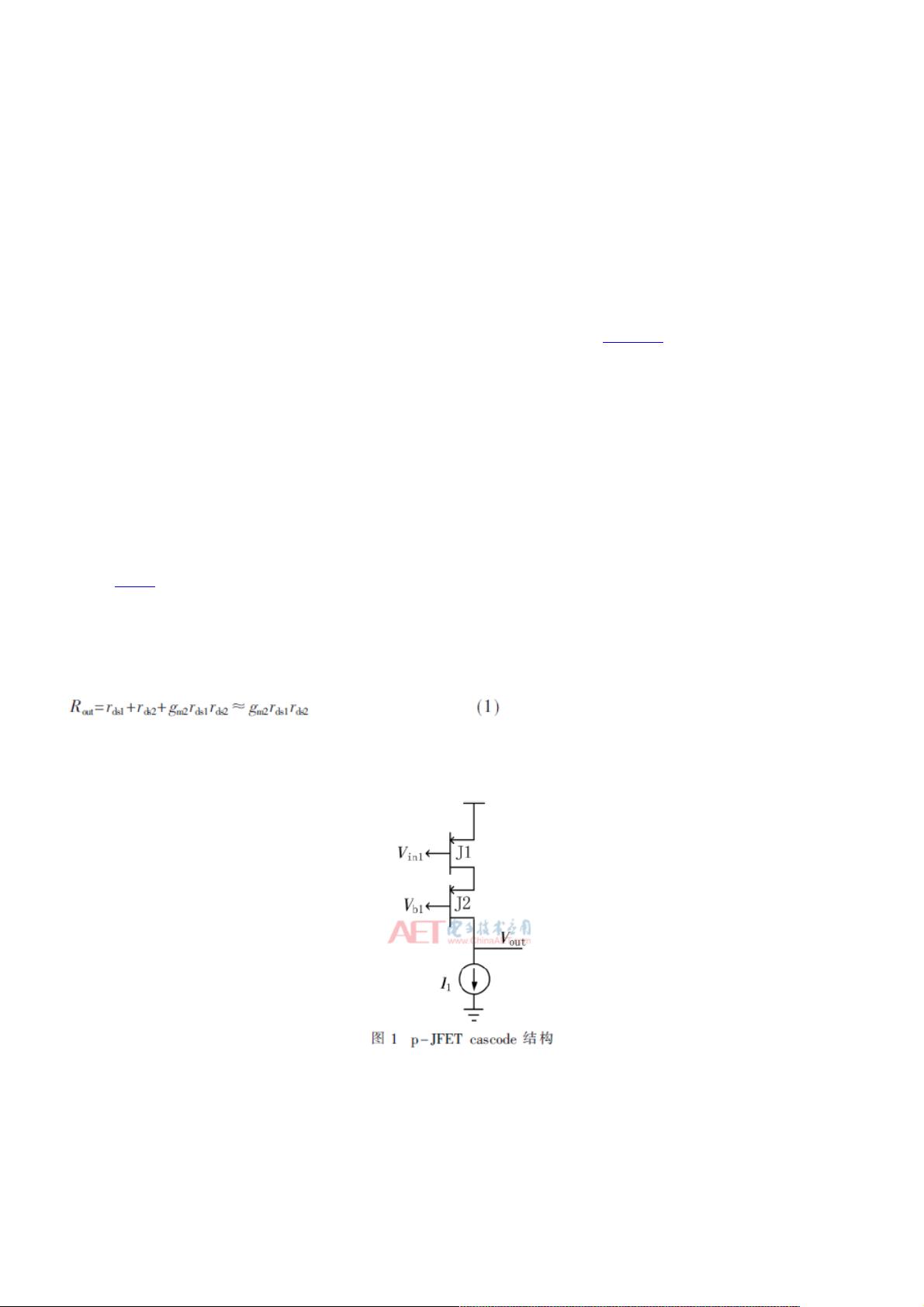

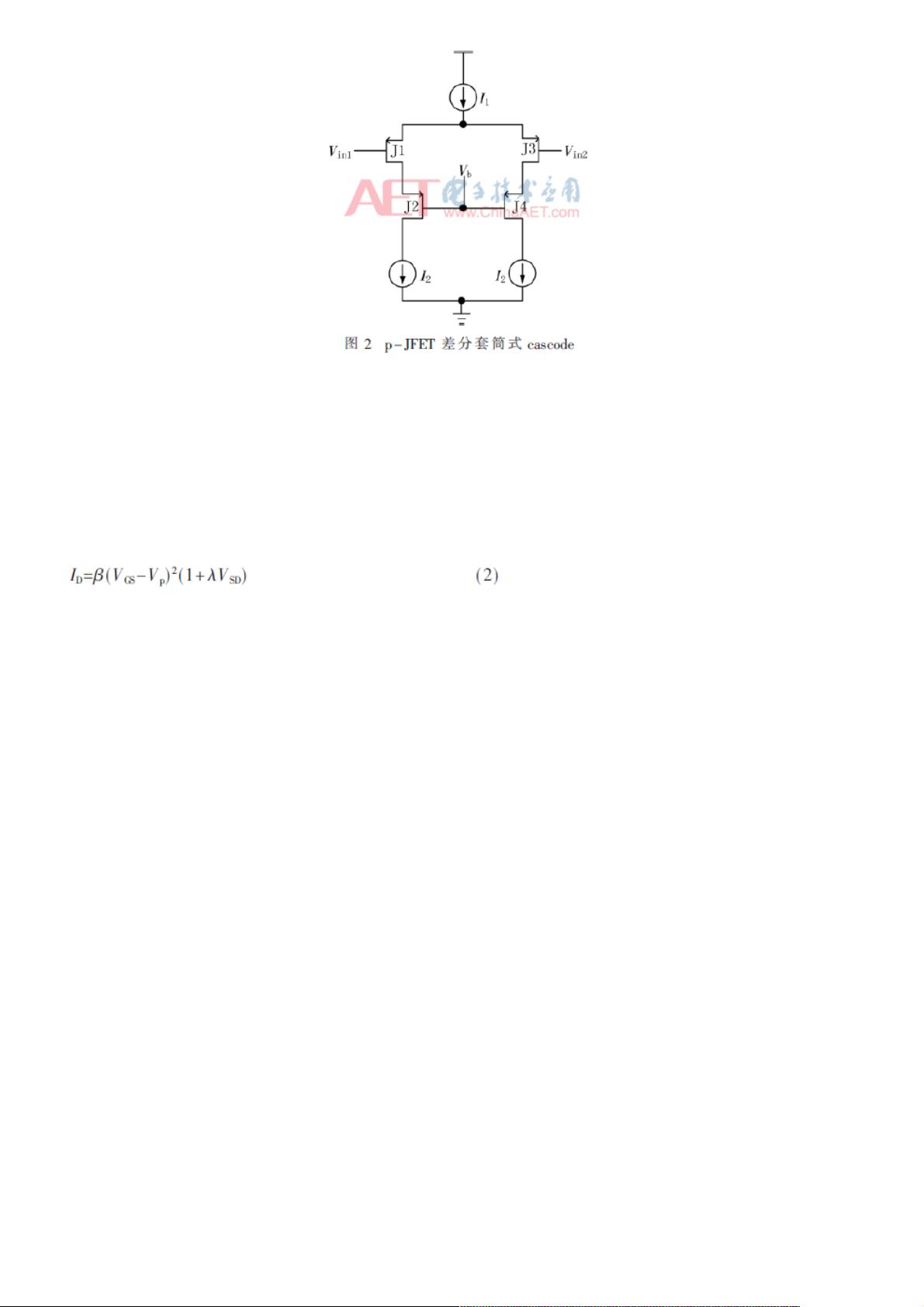

基于70 V高压双极型工艺,设计了一种适用于单片高压功率运算放大器的输入级电路。该电路采用p沟道结型场效应晶体管(JFET)组成的差分对套筒式共源共栅(differential telescopic cascode)结构,具有低偏置电流、低失调电压、低失调电流、高共模抑制比的特点。以共集-共射(CC-CE)的放大电路结构作为该输入级电路的负载,减小对输入级影响的同时能够提高电压增益。Spectre仿真结果表明,输入偏置电流仅为20 pA,失调电压为0.11 mV,失调电流为0.57 fA,连接负载后的增益可以达到89 dB,单位增益带宽达到8.13 MHz。 【功率运算放大器输入级电路设计】 在设计适用于高压功率运算放大器的输入级电路时,需要考虑的关键因素包括低偏置电流、低失调电压、低失调电流以及高共模抑制比。这样的要求是为了确保运算放大器在处理微弱信号时能够提供高精度的放大效果。传统的共极-共射(CC-CE)结构虽然常用于此类电路,但由于引入额外的电流源,可能导致较高的功耗。 一种创新的解决方案是采用p沟道结型场效应晶体管(JFET)组成的差分对套筒式共源共栅(differential telescopic cascode)结构。这种设计利用了JFET的特性,如低输入偏置电流和高输入阻抗,以实现更好的性能。JFET的差分对套筒式cascode结构由J1到J4四个JFET组成,它们的组合提高了电路的增益并降低了对输入级的影响。 共集-共射(CC-CE)结构作为输入级的负载,起到缓冲作用,能够减少负载对输入级的影响,同时提供主要的电压增益。输入偏置电流通过优化JFET的栅源电压(VGS)来控制,使其工作在恒流区,以减少1/f噪声。栅漏电压(VGD)需大于等于夹断电压(Vp),以确保JFET工作在恒流模式下,从而降低偏置电流。 仿真结果显示,该输入级电路的输入偏置电流仅为20 pA,失调电压为0.11 mV,失调电流为0.57 fA,这证明了设计的高效性。连接负载后的增益高达89 dB,单位增益带宽达到了8.13 MHz,这表明电路不仅有良好的线性特性,还能应对高速信号处理需求。 这种基于高压双极型工艺的输入级设计,克服了传统CC-CE结构的局限,实现了低功耗和高性能的平衡。它适用于高电压环境,如工业控制、汽车电子、轨道交通等领域的应用,这些领域通常需要将小信号放大为大功率输出,而高压大功率运算放大器正是实现这一目标的关键组件。 总结来说,该设计通过采用p沟道JFET的差分对套筒式共源共栅结构,成功地实现了高压运算放大器输入级的优化,具备低偏置电流、低失调和高共模抑制比等优点,为高压大功率运算放大器的性能提升提供了新的设计思路。这种技术的创新之处在于将CMOS技术中的设计理念引入到高压双极型工艺中,为未来高压运算放大器的进一步发展奠定了基础。

剩余6页未读,继续阅读

- 粉丝: 9

- 资源: 955

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功