具有具有PCI和并行接口的数据采集系统设计和并行接口的数据采集系统设计

1 引言 随着计算机技术的飞速发展和普及,数据采集系统也迅速地得到应用。在生产过程中,应用这一系

统可对生产现场的工艺参数进行采集、监视和记录,为提高产品质量、降低成本提供信息和手段。典型数据采

集系统的构成是由A/D+DSP+FPGA(CPLD)+D/A。本文通过利用模数转换芯片AD6644,以及FPGA实现了可用

于两种接口(PCI、并行接口)传输模式下的高精度数据采集系统。 2 硬件电路设计 2.1 系统设计方案

本数据采集系统主要由模拟部分,数字部分和接口部分三大板块组成,如下图1所示。其中模拟部分主要包含

模拟中频信号预处理模块和模数转换模块;数字部分除时钟产生电路外

1 引言

随着计算机技术的飞速发展和普及,数据采集系统也迅速地得到应用。在生产过程中,应用这一系统可对生产现场的工艺

参数进行采集、监视和记录,为提高产品质量、降低成本提供信息和手段。典型数据采集系统的构成是由

A/D+DSP+FPGA(CPLD)+D/A。本文通过利用模数转换芯片AD6644,以及FPGA实现了可用于两种接口(PCI、并行接口)传输

模式下的高精度数据采集系统。

2 硬件电路设计

2.1 系统设计方案

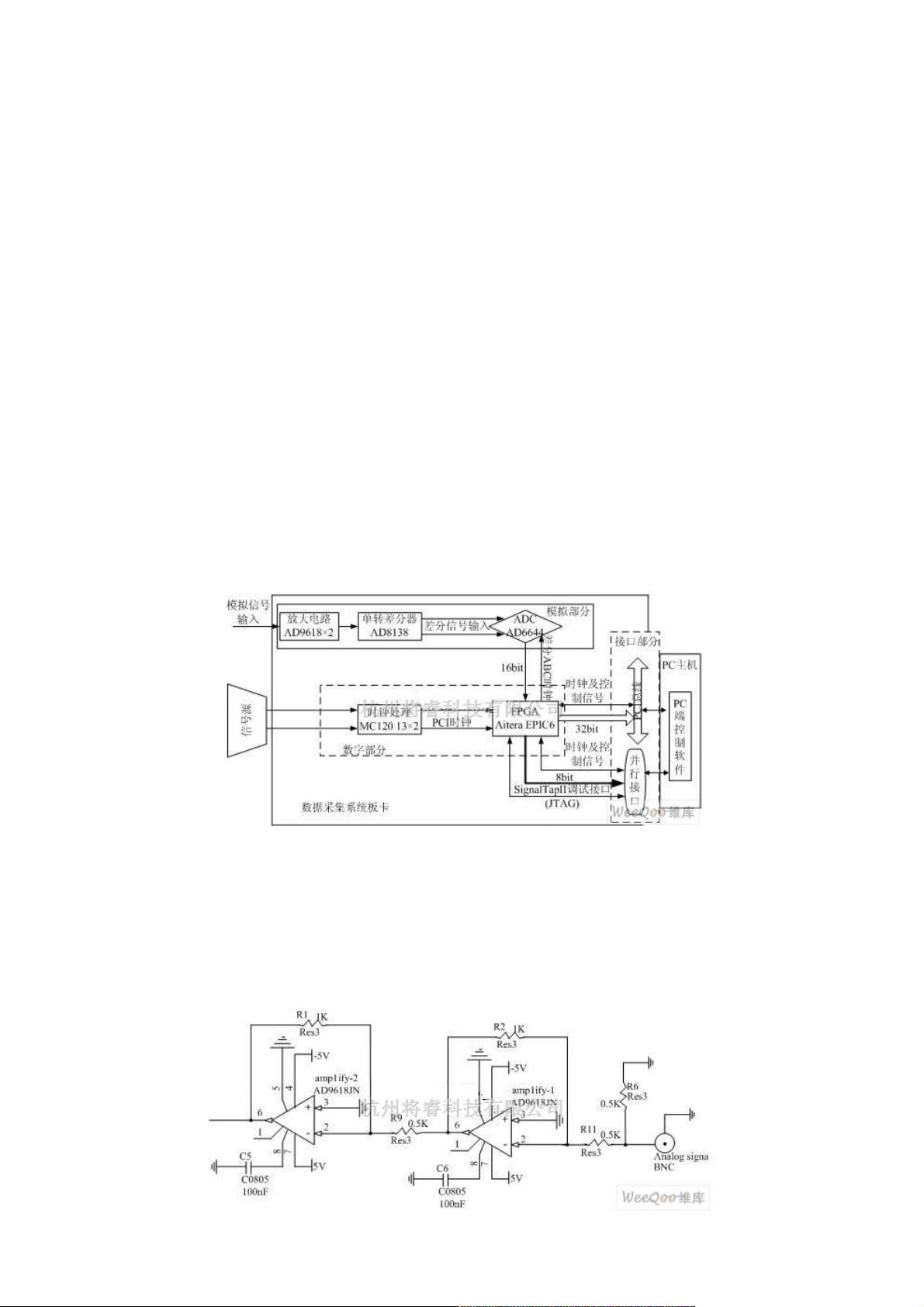

本数据采集系统主要由模拟部分,数字部分和接口部分三大板块组成,如下图1所示。其中模拟部分主要包含模拟中频信

号预处理模块和模数转换模块;数字部分除时钟产生电路外,其余部分完全在FPGA中设计完成;接口部分包含PCI总线接

口、DB25并行接口以及SignalTapII逻辑分析仪调试接口。

本系统的设计思路就是:首先通过模拟中频信号预处理模块,将调整后的模拟信号输入给A/D转换器,然后经模数转换之

后将16bit数字信号(AD6644输出14bit,再加上2个校验位)直接输出给FPGA进行存储。在FPGA中设计了高速缓冲器DCFIFO

和高速存储器DPRAM以及一系列时序控制逻辑,以保证在预定容量下能够实时的存储由ADC发送过来的数据。同时,在

FPGA中还设计了2种数据传输接口,从而使得系统可以在我们选择的模式下进行数据传输,或通过并行接口,或通过PCI总线

接口。

图1 系统总体框图

2.2 模拟中频信号预处理模块

首先,将该输入信号通过两级放大器,目的是为了使模拟输入信号幅度达到AD6644输入幅度的要求和对模拟输入信号进

行很好的隔离。这里选用AD9618来实现对模拟信号的放大功能。AD9618的单位增益带宽和压摆率的指标均较高,能起到对

模拟输入信号放大和改善性能的作用。电路图如图2所示。

评论0