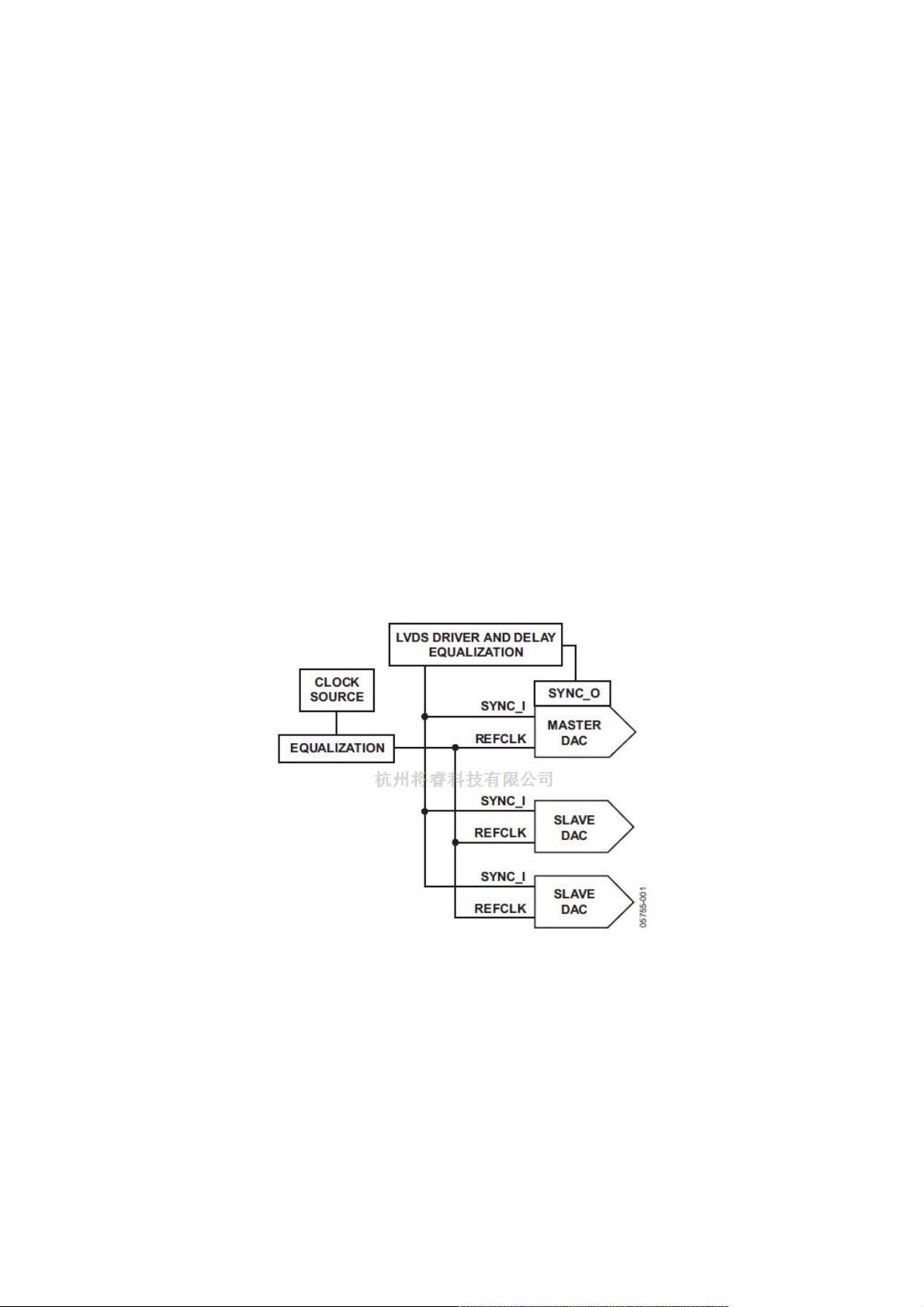

简介 AD9779 TxDAC的DAC输出采样速率最高可达1 GSPS.在某些应用中,例如需要波束导引的应用,用户可以同步多个AD9779.因此,当AD9779以接近最高速度工作时,TxDAC时序特性变得至关重要。 本应用笔记不讨论AD9779运作涉及到的全部细节。若要全面了解其内部数字引擎,用户应参阅AD9779数据手册。本应用笔记扩展了SYNC_I的使用,使多个AD9779器件实现相同的REFCLK/DATACLK同步。 在传统的插值TxDAC中,当DAC采用DAC输出采样速率时钟驱动时,会产生两个问题。第一,可能难以确定输入数据在哪一个DACCLK沿锁存。多数DAC解决 【模拟技术中的多个AD9779 TxDAC器件的同步】 AD9779 TxDAC是一款高速数字模拟转换器,其最高输出采样速率可达1 GigaSamples Per Second (GSPS)。在一些高级应用中,比如波束导引系统,需要同步多个AD9779以实现精确的信号生成。在高速运行条件下,TxDAC的时序特性成为关键因素,因为它直接影响到系统的性能和信号质量。 本文主要关注如何通过扩展SYNC_I信号的使用,实现多个AD9779器件的REFCLK(参考时钟)和DATACLK(数据时钟)同步。在传统的插值TxDAC中,由于DAC使用输出采样速率时钟驱动,可能会遇到两个问题:确定输入数据在哪个DACCLK边缘被锁存可能困难;多个TxDAC的DATACLK输出无法保证完全同步,尤其是在上电或不同温度条件下。 为了解决这些问题,AD9779提供了一个名为SYNC_I的输入时钟,它能够同步多个器件的数据输入锁存。多数DAC会通过DATACLK信号指示输入寄存器的锁存沿位置,但AD9779的SYNC_I进一步增强了这种同步能力,允许用户通过外部控制实现多个器件的精确同步。 同步方案通常有两种:主/从模式和全从模式。在主/从模式中,一个AD9779作为主器件,其他为从器件,主器件的SYNC_O+和SYNC_O?信号驱动从器件的SYNC_I输入。而在全从模式下,所有器件均依赖外部的SYNC_I信号进行同步。无论哪种模式,都需要确保所有器件的REFCLK输入同步,并且使用相同的SYNC_I信号。 为了实现同步,REFCLK输入需采用高增益差分放大器,确保足够的共模输入电平和信号摆幅。主器件的SYNC_O信号可以通过寄存器配置选择上升沿或下降沿触发,并带有可编程延迟。此延迟可以通过寄存器0x04和0x05的部分位设置。SYNC_O信号的速度可以是REFCLK的整数倍,由寄存器0x04的其他位控制。 同步输入(SYNC_I)也有可编程延迟,通过寄存器0x05的相应位设置,用于补偿不理想的信号路径或电路延迟。同时,数据总线的均衡也至关重要,AD9779提供了DATA_CLOCK_DELAY寄存器来调整各器件的锁存时间,以应对总线不均衡问题。 为了确保时序正确,必须满足AD9779的建立保持关系,这些关系在数据手册的“时序信息”部分有详细说明。SYNC_O_DELAY常用于平衡SYNC_I和REFCLK的时序,确保同步的有效性。 总结来说,同步多个AD9779 TxDAC器件的关键在于正确配置和使用SYNC_I信号,以及精细调整REFCLK、DATACLK和数据总线的时序关系。这需要深入理解AD9779的内部机制,以及如何通过寄存器编程来优化同步性能。通过适当的同步策略,可以确保在高采样速率下,多个AD9779器件生成的模拟信号保持一致,从而在复杂系统中实现精确的信号处理。

- 粉丝: 5

- 资源: 942

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功