一种基于以太网的嵌入式数据传输速率优化方法研究一种基于以太网的嵌入式数据传输速率优化方法研究

基于以太网的嵌入式数据传输系统在许多领域被普遍采用,系统的传输效率需要提高。基于ARM Cortex-M4内

核和常用的嵌入式网络协议栈LwIP,针对点对点数据传输的特点,采用了零数据拷贝技术并对UDP协议加以优

化改进,大大提高了传输性能。测试结果表明,数据传输的速率从未优化的2.03 MB/s提升到9.80 MB/s,已接

近百兆以太网的极限。同时引入ACK回应机制保障了UDP数据传输的可靠性。

摘摘 要要: 基于以太网的嵌入式数据传输系统在许多领域被普遍采用,系统的传输效率需要提高。基于ARM Cortex-M4内核

和常用的嵌入式网络协议栈LwIP,针对点对点数据传输的特点,采用了

关键词 关键词:

0 引言引言

基于以太网的嵌入式数据传输系统由于其结构灵活、通用性强、传输速度快、传输距离远等特点,在许多应用领域都发挥

着重要的作用[1]。但由于嵌入式系统本身的结构[1]以及网络协议栈的限制[2],网络数据传输的效率不高,远远达不到以太网

传输的理论带宽。一方面通过改进嵌入式系统的硬件结构,如利用FPGA并行处理的优势[2],可以大大提高数据传输的效率;

另一方面,通过分析并改进嵌入式网络协议栈,也可以提高网络数据传输的速度[3]。

嵌入式网络传输系统由于成本资源的限制,往往采用简化的网络传输协议TCP/IP协议。LwIP协议栈是TCP/IP协议的一种

简化版本,专门针对嵌入式系统开发,专注于减少资源消耗,对性能优化却比较少,效率不是很高[4]。

本文通过研究、分析常用的嵌入式网络协议栈LwIP的结构[4],针对简单的点对点传输网络环境,提出一种简单、灵活、

高效的基于UDP协议的嵌入式数据传输效率的优化方法。

1 系统结构和协议栈分析及改进系统结构和协议栈分析及改进

系统以嵌入式微处理器STM32F407为核心,使用轻型网络传输协议栈LwIP实现百兆以太网传输数据。考虑到嵌入式系统

的处理速度和资源限制,为保证高效的数据传输,选择更高效的UDP协议[5]。对于数据传输的可靠性,提出基于ACK回应的

机制来改善。

1.1 系统硬件结构系统硬件结构

选择意法半导体的微处理器STM32F407作为系统的核心。它采用专为要求高性能、低成本、低功耗的嵌入式应用专门设

计的ARMCortex-M4内核,时钟频率达到168 MHz,具有专门的网络MAC层接口和专用于网络的DMA通道,外加PHY芯片和

网络接口,通过网线就可以实现网络传输。

1.2 LwIP协议栈结构协议栈结构

LwIP协议栈是基于分层的方式设计的,包括应用层、IP层、传输层等,每一层的协议都代表一个独立的模块,但是为了

最小限度地使用系统资源,模块间使用松散的通信机制,通过共享内存来实现通信[6]。

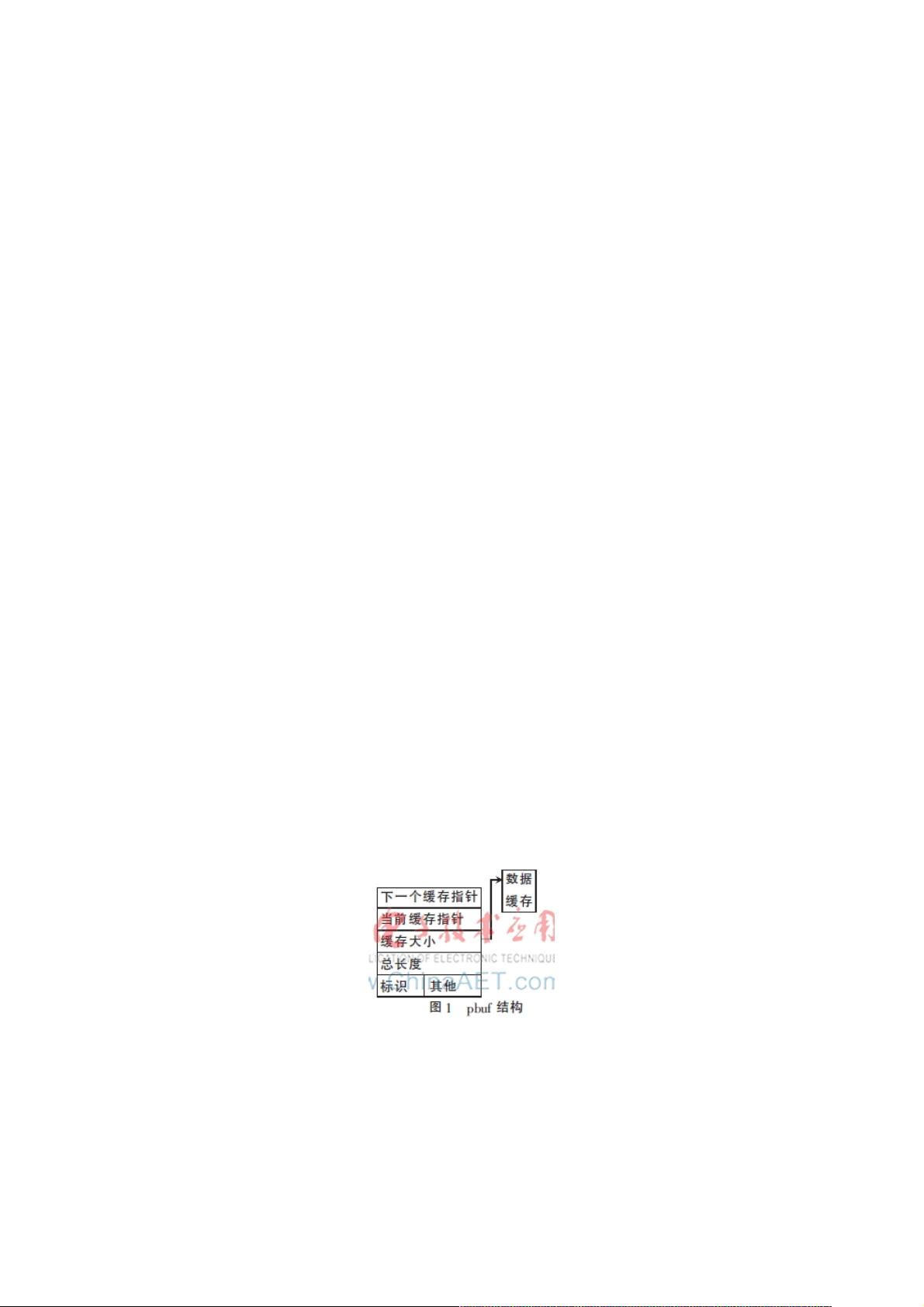

LwIP协议栈设置了一个各层共享的内存空间——网络数据包缓冲区,数据分组存在一个确定的缓冲区Data buff中,在层

与层之间打包与解包的过程中传递的只是这个缓冲区的地址payload,只有当数据要被发送至PHY或被应用程序取走时才会通

过数据拷贝来实现。LwIP协议栈使用pbuf来管理这个包缓冲区,从而实现在协议栈各层之间数据包的零拷贝。pbuf结构如图1

所示,包括包的信息、标志、地址等,payload指针指向包缓冲区Data buff。

1.3 系统网络传输过程分析系统网络传输过程分析

整个数据通路如图2所示。