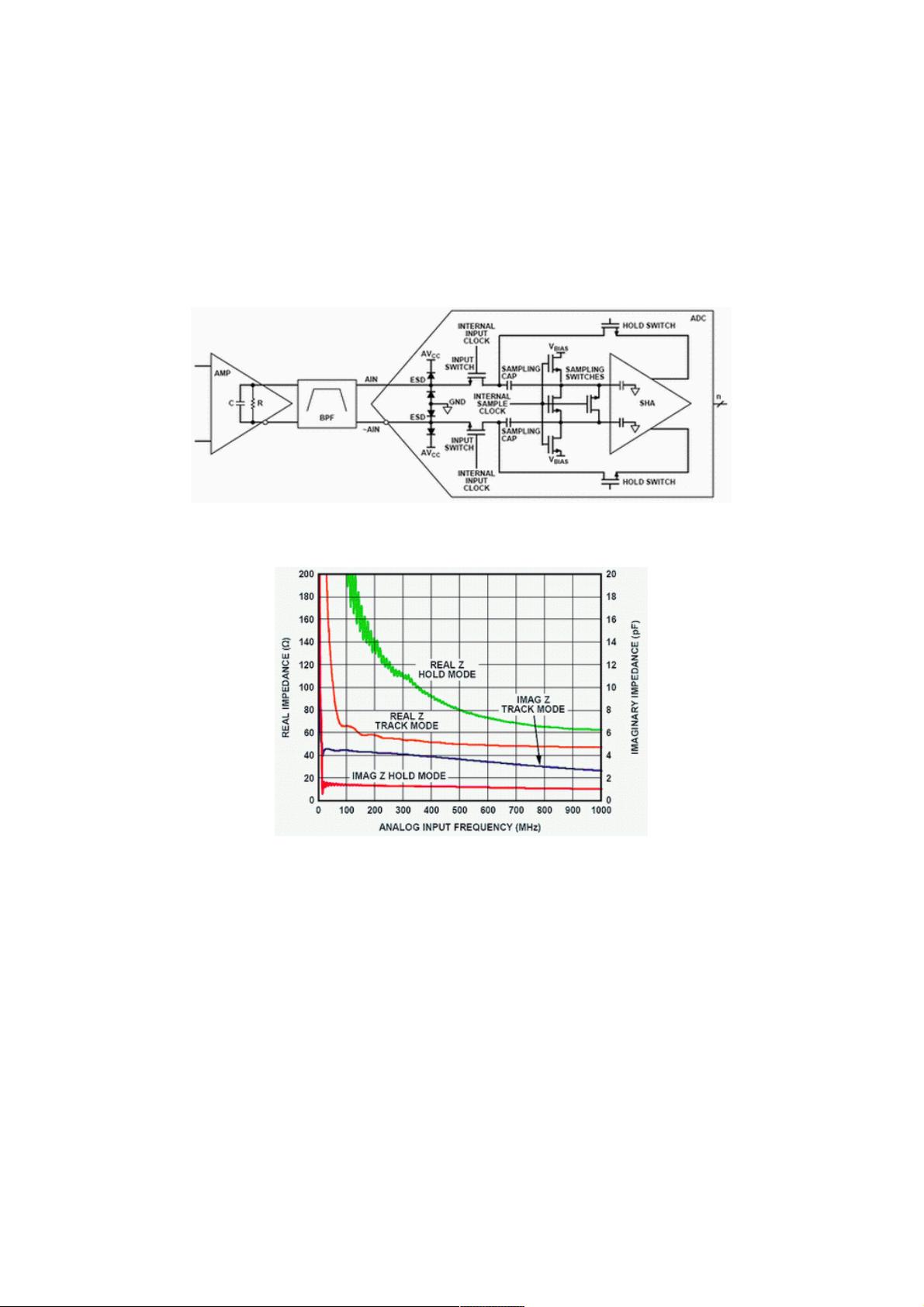

开关电容ADC(Analog-to-Digital Converter)是一种常见的数字信号转换器,它利用开关电容网络进行采样和量化。在高采样速率的开关电容ADC中,为了降低功耗,通常不配备缓冲器。这样的ADC由跟踪和保持放大器(SHA)组成,包括输入开关、采样电容器、采样开关以及放大器。在跟踪模式下,输入开关闭合,驱动器向采样电容器提供信号;而在保持模式下,输入开关断开,电容器保持采样状态。 由于开关电容ADC在跟踪和保持模式下的输入阻抗不同,这使得匹配ADC与驱动电路的阻抗变得困难。尤其是在跟踪模式期间,输入阻抗需与驱动电路匹配,以确保信号的准确采样。输入阻抗随频率的变化主要由采样电容和信号路径中的寄生电容决定。了解这种关系对于精确匹配至关重要,尤其是在高频应用中。 例如,AD9236这款ADC在跟踪模式下的输入阻抗远低于保持模式。在输入频率小于100 MHz时,跟踪模式下的输入阻抗虚部大于4pF,而保持模式下则减小到1pF。输入阻抗的数据可以帮助设计阻抗变换网络,这种网络可以捕获有用的信号,并抑制不必要的频率成分。 为了实现有效的信号传输,可以设计一个电抗匹配网络,将输入阻抗转化为易于处理的等效负载,例如一个并联的RC网络。通过复数运算(如导纳的转换)可以计算出这个等效网络,许多数学软件如Matlab、MathCad或Excel都可以完成这些计算。 在采样理论中,奈奎斯特准则规定,采样频率至少是信号最高频率的两倍,以避免信号失真。然而,有些ADC采用IF(Intermediate Frequency)采样,即在高于第一奈奎斯特区的频率上采样,这被称为欠采样或IF采样。IF采样能够简化信号链,减少噪声,提高信噪比(SNR)和无杂散动态范围(SFDR),并允许在不增加额外混频级的情况下进行高频处理。 在IF采样中,抗锯齿滤波器(Anti-Aliasing Filter, AAF)的设计显得尤为重要,因为滤波器必须能够有效地抑制高于采样频率的信号,以防止信号混叠到第一奈奎斯特区,造成干扰。正确设计的滤波器可以确保信号在进入ADC之前被适当地限制在奈奎斯特区之内,从而满足采样定理的要求。 开关电容ADC的阻抗谐振匹配方法是信号调理的关键,它涉及到精确的输入阻抗计算、匹配网络设计以及采样策略。理解和掌握这些技术细节对于实现高性能、低功耗的ADC系统至关重要。

- 粉丝: 7

- 资源: 882

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 5G模组升级刷模块救砖以及5G模组资料路由器固件

- C183579-123578-c1235789.jpg

- Qt5.14 绘画板 Qt Creator C++项目

- python实现Excel表格合并

- Java实现读取Excel批量发送邮件.zip

- 【java毕业设计】商城后台管理系统源码(springboot+vue+mysql+说明文档).zip

- 【java毕业设计】开发停车位管理系统(调用百度地图API)源码(springboot+vue+mysql+说明文档).zip

- 星耀软件库(升级版).apk.1

- 基于Django后端和Vue前端的多语言购物车项目设计源码

- 基于Python与Vue的浮光在线教育平台源码设计

信息提交成功

信息提交成功