没有合适的资源?快使用搜索试试~ 我知道了~

Yet more image computations for SMV, the symbolic model verifier

需积分: 5 0 下载量 134 浏览量

2021-06-29

19:44:31

上传

评论

收藏 128KB PDF 举报

温馨提示

Yet more image computations for SMV, the symbolic model verifier Yet More Image Computations for SMV, the Symbolic Model Verifier Hiromi Hiraishi Faculty of Engineering, Kyoto Sangyo University, Kyoto, Japan 603-8555 SUMMARY This paper describes a collection of techniques to improve the efficiency of the pre- and postimage computa- tions that are the core of the Symbolic Model Verifier (SMV), which is used for formal logic design verification. The proposed techniques aim mostly at imp

资源推荐

资源详情

资源评论

Yet More Image Computations for SMV, the Symbolic Model

Ve rifier

Hiromi Hiraishi

Faculty of Engineering, Kyoto Sangyo University, Kyoto, Japan 603-8555

SUMMARY

This paper describes a collection of techniques to

improve the efficiency of the pre- and postimage computa-

tions that are the core of the Symbolic Model Verifier

(SMV), which is used for formal logic design verification.

The proposed techniques aim mostly at improving the

efficiency of the verification of asynchronous processes.

The improvements are mainly made by (1) the early elimi-

nation of process variables in the postimage computations,

(2) the application of the conjunctive partitioning technique

to the verification of asynchronous processes, (3) the early

substitution of the stable state variables, and (4) the nonde-

terministic substitution method for the preimage computa-

tions. The experimental measurements show that the

proposed techniques are very effective and result in a

speedup of up to 50 times compared to the original SMV.

© 2000 Scripta Technica, Syst Comp Jpn, 31(9): 19,

2000

Key words: Formal design verification; symbolic

model checking; image computation; asynchronous proc-

ess; SMV.

1. Introduction

As the logic systems to be designed become larger

and more complex, the designers are more apt to make

design errors. Logic simulations have been widely used to

find design errors. However, it is hard to guarantee the

correctness of the logic design by simulations because the

simulations cannot cover all cases. Therefore, formal de-

sign verification is important to guarantee that the designs

meet their specifications.

The symbolic model checking [2, 3] of Computation

Tree Logic (CTL) [1] is one of the most practical ap-

proaches to formal logic design verification. In this ap-

proach, logic systems to be designed are modeled as finite

state transition systems. Their specifications are described

in CTL. Then, symbolic model checking examines if the

designs satisfy the specifications. The Symbolic Model

Verifier (SMV) [6, 14] based on this approach has been

developed at Carnegie-Mellon University, which suc-

ceeded in verifying large logic systems whose state space

exceeds 10

20

.

In symbolic model checking, a set of states and a

transition relation are represented by Boolean expressions.

The verification algorithm is based on the manipulations of

these Boolean expressions. Furthermore, a Binary Decision

Diagram (BDD) [4, 5] is used to manipulate Boolean ex-

pressions. There have been proposed various methods to

improve the efficiency of symbolic model checking [712],

which enable us to verify large practical logic designs.

The size of the BDD is, however, apt to explode in

verification of large logic systems. We often have to con-

struct an abstract model in order to verify more complex

© 2000 Scripta Technica

Systems and Computers in Japan, Vol. 31, No. 9, 2000

Translated from Denshi Joho Tsushin Gakkai Ronbunshi, Vol. J82-D-I, No. 7, July 1999, pp. 791798

The author would like to express his appreciation to Professor E.M. Clarke

of Carnegie-Mellon University for valuable suggestions. The major part

of this research was done during his stay at CMU supported by the foreign

research study program of Kyoto Sangyo University. Part of this research

was supported by a grant of scientific research from the Ministry of

Education of Japan.

1

and larger logic designs. In such an abstract model, a system

is often represented as a set of asynchronous processes

(modules).

In the verification of asynchronous processes, a cou-

ple of methods based on partial orders over events have

been proposed [15, 16] to improve the efficiency by de-

creasing the reachable state space. However, as far as the

author knows, no approaches have been proposed to im-

prove the efficiency of symbolic model checking directly

by considering the characteristics of asynchronous proc-

esses. Accordingly, we tried to improve the symbolic model

checking algorithm of SMV in order to improve the effi-

ciency of the verification of asynchronous processes. The

major techniques used for the improvement include:

x Early smoothing of the process selection vari-

ables, which accelerates the postimage computa-

tions that are used for computing the reachable

states.

x Provision for application of the conjunctive parti-

tioning technique to each asynchronous process.

x Early substitution of the corresponding next state

variables to the stable state variables in the

postimage computation for each process based on

the conjunctive partitioning technique.

x Preimage computation based on nondeterministic

substitution. This is an extension of the efficient

deterministic substitution method for preimage

computation.

The experimental measurements for these techniques have

shown that they are effective and can enhance efficiency

greatly.

Section 2 presents the notations and the basic opera-

tions of symbolic model checking. The transition relations

generated by SMV are also explained. In Section 3 a

postimage computation algorithm based on early smooth-

ing of the process selection variables is proposed. Section

4 shows how to apply the conjunctive partitioning tech-

nique to the image computations of asynchronous proc-

esses. A postimage computation algorithm based on early

substitution to the stable state variables is proposed in

section 5, and a preimage computation algorithm based on

nondeterministic substitution is proposed in Section 6. Sec-

tions 3, 5, and 6 also present the results of the experimental

measurements, all of which were measured on a Sparc Ultra

II 250 MHz clock.

*

2. Preliminaries

This section presents the basic notations and the

definitions related to symbolic model checking. The transi-

tion relations generated by SMV are also explained.

2.1. Symbolic model checking

In SMV the logic systems under verification are

represented by the finite state transition systems called

Kripke structures. The specifications that the logic sys-

tems should satisfy are described in CTL temporal logic

formulas.

Definition 1 Kripke structure is defined by a 4-tuple

K

S, R

,

I, S

0

, where S is a finite set of states, R S u S

is a total binary relation on the states. It is assumed that

every state has at least one next state. Let AP be a set of

atomic propositions. I : S o 2

AP

gives a set of atomic

propositions true at the state. S

0

S is a set of initial states.

Whether the designed system meets its specifications

is verified by symbolic model checking. In symbolic model

checking, the set of states where the specification holds is

calculated by postimage computations and/or preimage

computations. Postimage computation gives a set of the

next states of the given set of current states, whereas the

preimage computation gives a set of the previous states of

the given current states. These image computations are done

by Boolean formula manipulations based on BDD.

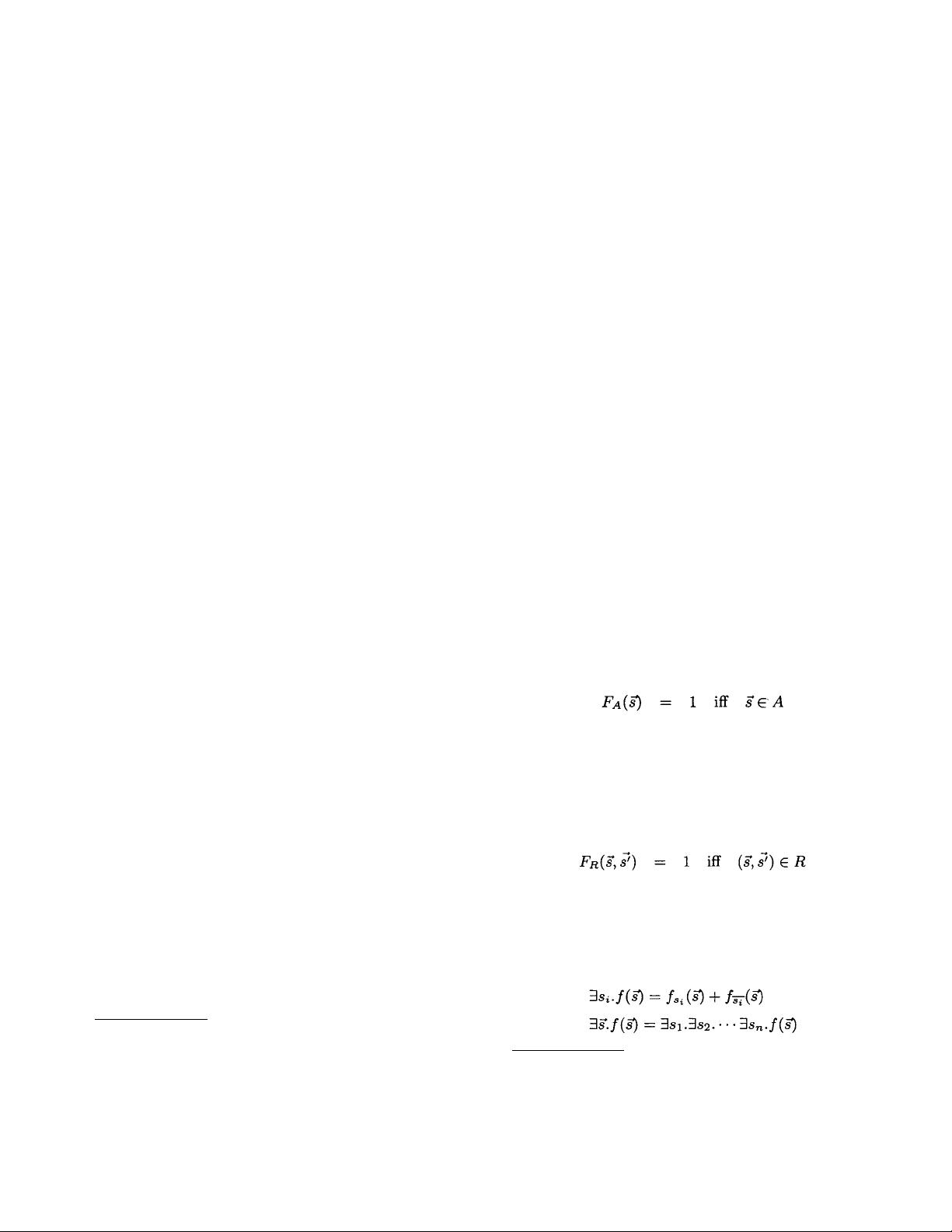

Let B = {0, 1} be a set of Boolean values. Let s

i

be a

variable over B. s

s

1

, s

2

, . . . , s

n

denotes a vector of

state variables. Then a subset A of the state space

*

S

B

n

can be represented by the n-variable Boolean func-

tion F

A

s : S o B that satisfies the following equation:

F

A

is called a characteristic function of A.

Let s

i

g

be a next state variable over B.

sc

s

1

g

,

s

2

g

, . . .

,

s

n

g

denotes a vector of next state variables.

Then the transition relation can be given by the 2n-variable

Boolean function F

R

s, sc : S u S o

B

that satisfies the

following equation:

F

R

is called a transition relation function.

If there are no possibilities of confusions, we will use

A and R instead of F

A

and F

R

hereafter.

Let fs be a Boolean function of n variables. Smooth-

ing operations, s

i

. and s., are defined as follows:

*

The machine used for the measurements was an Ultra Enterprise 6000

(20 CPU, 8 GB memory). Up to 18 measurements were done in parallel.

The maximum memory required for each measurement was at most 200

MB.

*

In the case of S

B

n

, we can regard B

n

as the state space by appropriately

adding the states unreachable from the initial states.

2

剩余8页未读,继续阅读

资源评论

weixin_38576811

- 粉丝: 6

- 资源: 890

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (GUI框架)Matlab设计_的答题纸答题卡识别.zip

- (GUI框架)Matlab设计_的路牌交通牌照识别.zip

- 计算机物联网专业毕业设计的研究成果与实践过程报告模板

- MATLAB:考虑齿面接触变形量,基于石川算法求解齿轮时变啮合刚度,齿轮动力学时域图、相图、分岔图、庞加莱图,可用于参考学习齿轮动力学复现学习,程序内注释解答清晰,便于学习 附赠齿轮系统的非线性动力

- 数据库课程设计《SQL Server图书馆管理系统》(完整版)

- Spark 执行流程.xmind

- (GUI框架)Matlab设计_的车道线标定.zip

- (GUI框架)Matlab设计_的人脸+指纹融合系统.zip

- (GUI框架)Matlab设计_的人脸识别设计.zip

- Linux命令行核心命令详解与应用场景

- (GUI框架)Matlab设计_的人脸门禁预警.zip

- (GUI框架)Matlab设计_的手写汉字识别.zip

- (GUI框架)Matlab设计_的手写字符识别.zip

- MATLAB Simukink基于下垂控制的光储直流微电网离网运行控制 关键字:离网;直流下垂;交流负载;V f

- (GUI框架)Matlab设计_的视频图像去雾.zip

- (GUI框架)Matlab设计_的小波变换dwt数字水印.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功