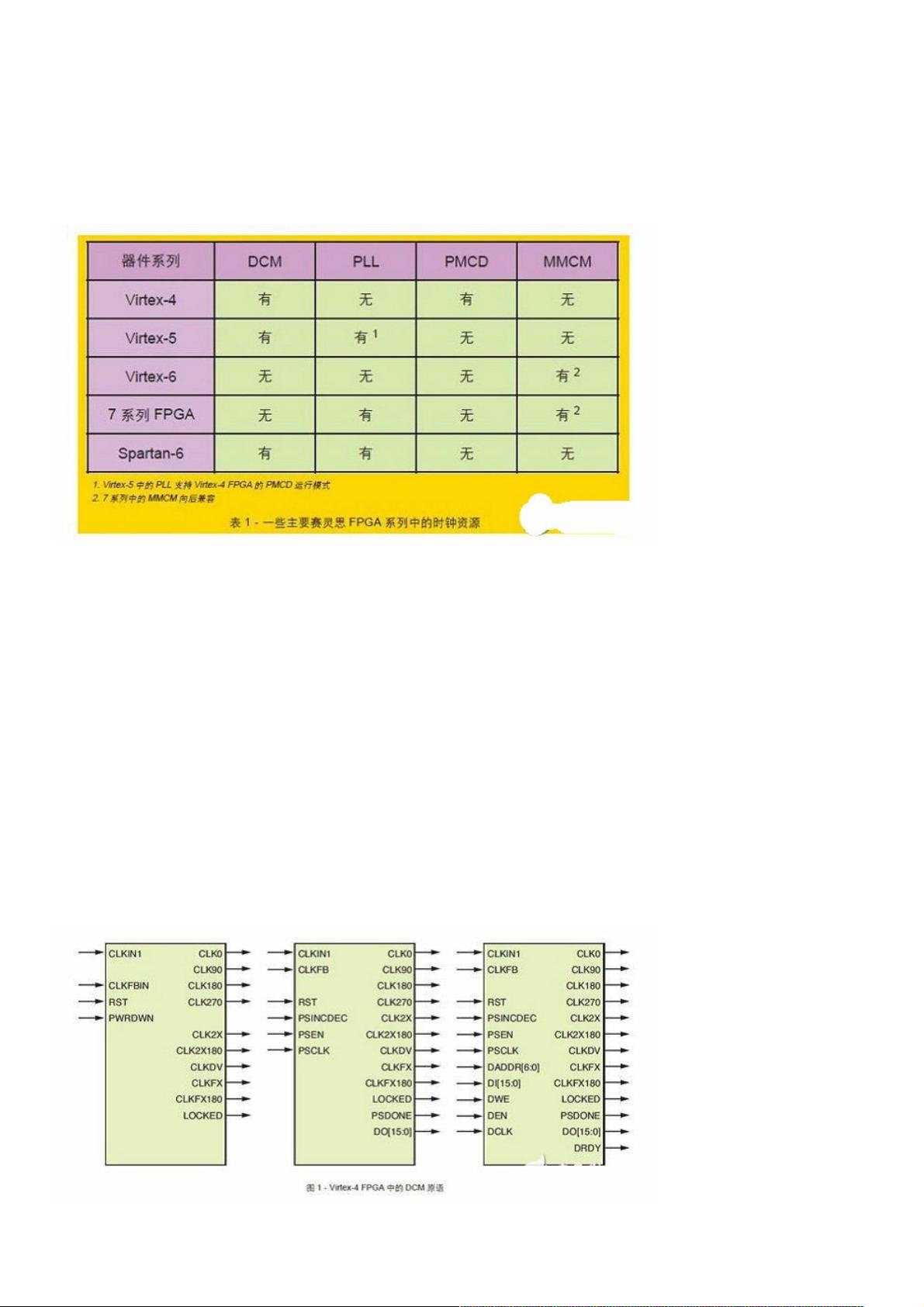

FPGA时钟资源详解 FPGA设计中,时钟资源是非常重要的组件之一,正确使用时钟资源可以提高FPGA设计的性能和稳定性。然而,对FPGA设计新手来说,什么时候用DCM、PLL、PMCD和MMCM四大类型中的哪一种,让他们颇为困惑。下面让我们深入了解一下这些时钟资源。 一、数字时钟管理器(DCM) DCM是FPGA设计中的一种重要的时钟资源,主要用于管理时钟架构和时钟信号的成形和操控。DCM内含一个延迟锁相环(DLL),可根据输入时钟信号,去除DCM输出时钟信号的歪斜,从而避免时钟分配延迟。DCM可以在时钟路径上引入延迟,比如生成行和列访问选通信号的时序。DCM还可以用于扩频时钟,并通过调制时钟信号来降低时钟信号的峰值电磁辐射。 二、锁相环(PLL) PLL是FPGA设计中的一种重要的时钟资源,主要用于实现频率综合、内外部时钟抖动滤波、时钟去歪斜等功能。PLL和MMCM处理的工作有许多是相同的,但是PLL更加灵活和强大。PLL可以用来实现相位匹配分配时钟或相位匹配延迟时钟。 三、相位匹配时钟分频器(PMCD) PMCD是FPGA设计中的一种重要的时钟资源,主要用于实现相位匹配分配时钟或相位匹配延迟时钟。PMCD可以用来实现时钟信号的相位匹配和时钟频率的调整。 四、混合模式时钟管理器(MMCM) MMCM是FPGA设计中的一种重要的时钟资源,主要用于实现频率综合、内外部时钟抖动滤波、时钟去歪斜等功能。MMCM和PLL处理的工作有许多是相同的,但是MMCM更加灵活和强大。 五、时钟资源的选择 在FPGA设计中,选择合适的时钟资源是非常重要的。不同的时钟资源适用于不同的应用场景。例如,DCM适用于实现延迟锁相环(DLL)、数字频率综合器、数字移相器或数字频谱扩展器。PLL和MMCM适用于实现频率综合、内外部时钟抖动滤波、时钟去歪斜等功能。 六、时钟资源的设计注意事项 在FPGA设计中,设计人员需要注意时钟资源的设计。例如,需要考虑时钟资源的精度、稳定性和可靠性。同时,设计人员还需要注意时钟资源的互连和布局,以避免时钟信号的互扰和干扰。 FPGA时钟资源是非常重要的组件之一,正确使用时钟资源可以提高FPGA设计的性能和稳定性。设计人员需要了解不同时钟资源的特点和应用场景,以便选择合适的时钟资源。

- 粉丝: 5

- 资源: 997

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 设计学长素材 (5).psd

- GPA案例介绍之计算耕地保有量

- 恶劣天气下道路上的行人、车辆,图像目标检测数据【已标注,约1000张数据,YOLO 标注格式】

- ros中用话题通信的方式实现Robotiq 300-S力矩传感器的数据传输(2024年12月17日)

- Vue3-devtools 可视化工具

- flink-1.20.0安装包

- 6500张黑夜场景下的交通灯检测、标注格式保存在csv文件中

- 2024年数据库课程设计-计算机科学技术.rar

- 基于ssm的戒烟网站源代码(完整前后端+mysql+说明文档+LW).zip

- 基于ssm的大学校医院信息管理系统源代码(完整前后端+mysql+说明文档).zip

信息提交成功

信息提交成功