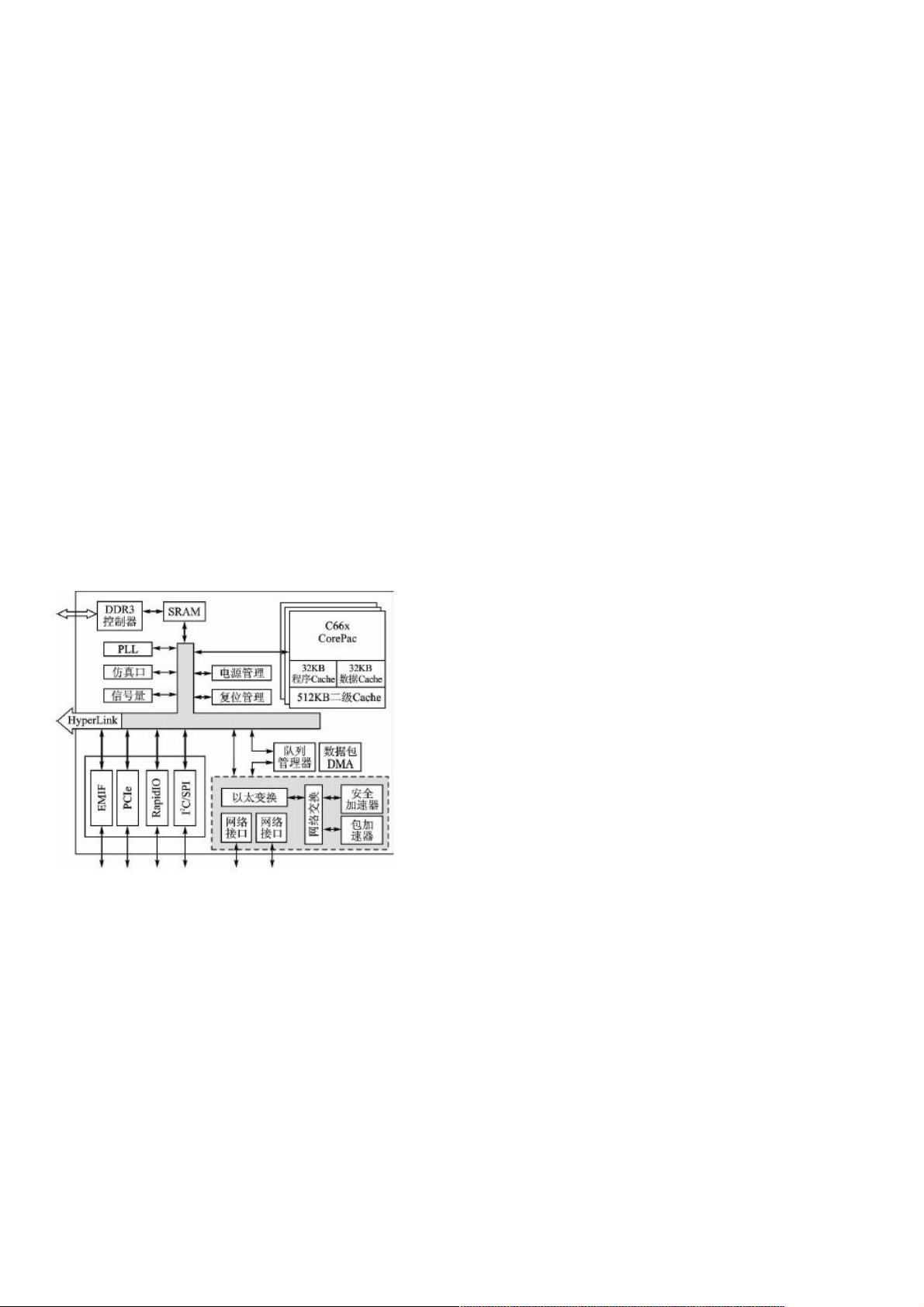

"八核浮点型DSP的双千兆网接口设计" 本文介绍了一种基于多核数字信号处理器TMS320C6678的嵌入式双千兆网络接口设计,实现单个芯片连接两个千兆网口,这两个网口可以各自独立传输数据,也可以联合传输数据,提高了实际的数据传输速率。 知识点: 1、TMS320C6678多核数字信号处理器:该处理器具有8核浮点型DSP,每个核最高工作频率可达1.25GHz,每个核可以提供40GMAC定点计算或者20GFLOP浮点计算能力,单个芯片可以提供320GMAC或者160GFLOP计算能力。 2、DSP(数字信号处理器)的应用:DSP具有较高的工作频率,其内部集成硬件网络MAC接口,外接一个物理层芯片就可以方便地实现千兆网络通信。多核DSP芯片可以连接多个千兆网口,使得其可以应用到高速数据传输场合。 3、千兆网络接口的优点:千兆网络接口具有数据传输速率快、连接方便、可以即插即用的优点,使得其应用较为广泛。 4、高速数据传输的需求:随着电子技术和处理器的发展,很多应用场合的数据通信速率超过千兆网口的实际传输速率。例如,在A/D采样中,需要直接存储A/D转换的采样数据,如果A/D转换位数为16位,工作在100MHz,则实际数据量为1.6Gbps。 5、RapidIO和PCIe接口的限制:这些接口不具有即插即用功能,与很多工业既有设备不能直接连接,限制了其应用场合。 6、TMS320C6678的片内结构:包括一个4MB的共享SRAM,RapidIO、PCIe、EMIF、SPI、I2C总线等接口。这些接口通过片内的高速互联总线和各个处理器交互数据。 7、网络相关的片内设备:包括两个对外的SGMII接口、以太交换和网络交换模块,以及用于数据管理的安全加速器和包加速器,可以快速检测数据的校验以及协议是否遵循网络标准,对于错误的数据直接丢弃,降低CPU的负担。 8、88E1111物理层芯片:具有SGMII接口,用于连接TMS320C6678,并提供了锁相环(PLL)、自动增益控制(AGC)、时序/相位控制、回音抵消等模块,以提高数据传输的可靠性。 9、硬件设计:包括TMS320C6678和两个88E1111的接口、88E1111和RJ45的接口、88E1111的硬件配置设计等几个部分。

- 粉丝: 0

- 资源: 891

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 计算机毕业设计:python+爬虫+cnki网站爬

- nyakumi-lewd-snack-3-4k_720p.7z.002

- 现在微信小程序能用的mqtt.min.js

- 基于MPC的非线性摆锤系统轨迹跟踪控制matlab仿真,包括程序中文注释,仿真操作步骤

- shell脚本入门-变量、字符串, Shell脚本中变量与字符串的基础操作教程

- 基于MATLAB的ITS信道模型数值模拟仿真,包括程序中文注释,仿真操作步骤

- 基于Java、JavaScript、CSS的电子产品商城设计与实现源码

- 基于Vue 2的zjc项目设计源码,适用于赶项目需求

- 基于跨语言统一的C++头文件设计源码开发方案

- 基于MindSpore 1.3的T-GCNTemporal Graph Convolutional Network设计源码

信息提交成功

信息提交成功