单片机与DSP中的基于单片机的跳频控制器的设计与实现

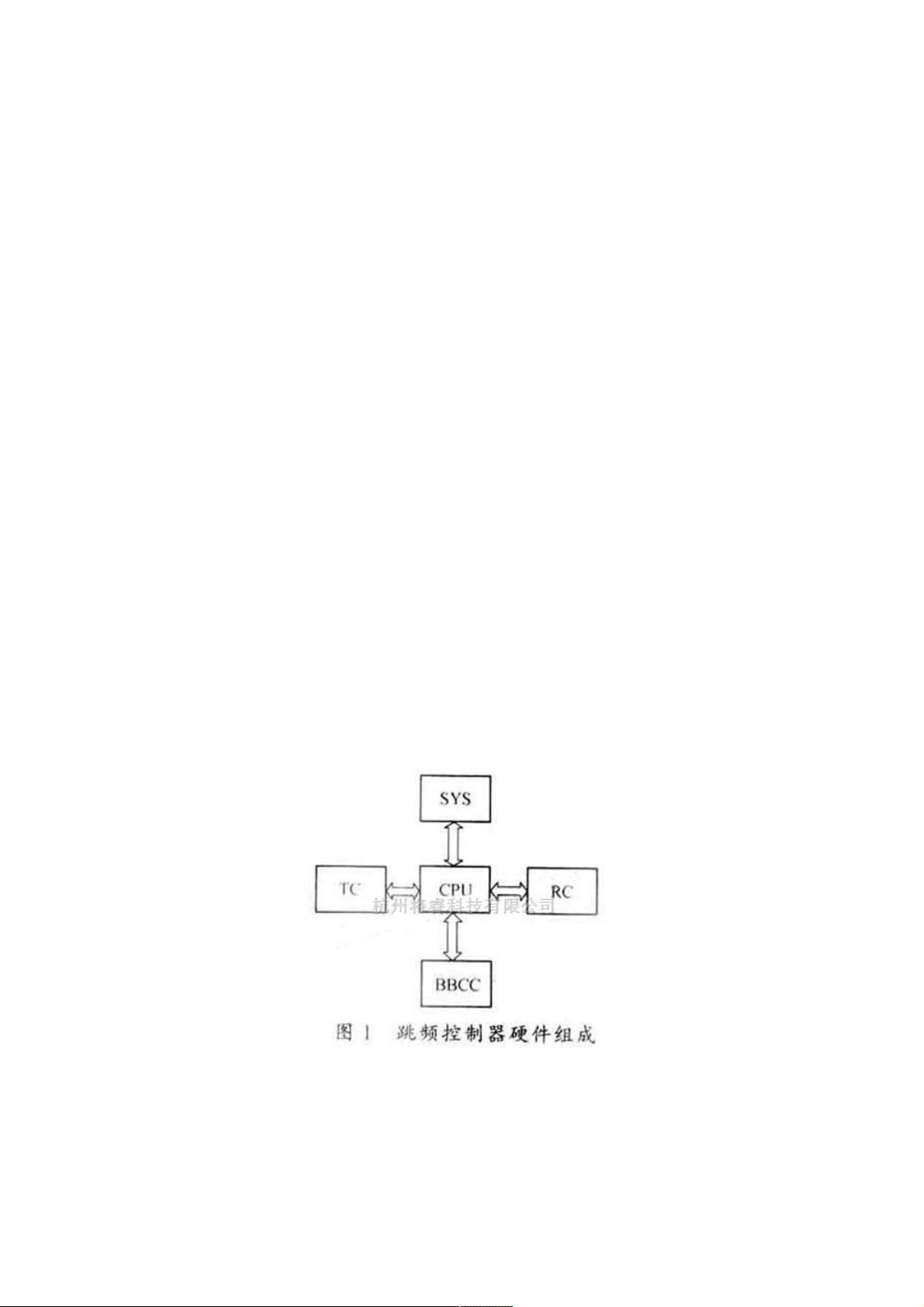

1 引言 跳频就是“多频、选码、频移键控”,即用伪码序列构成跳频指令来控制频率合成器,并在多个频率中进行选择的移频键控。 跳频通信具有抗干扰、抗截获的能力,并能做到频谱资源共享,所以,在当前现代化的电子战中,跳频通信已显示出巨大的优越性,它是战术无线电通信抗干扰措施的具体体现。另外,跳频通信也正应用到民用通信中,以抗衰落、抗多径、抗网间干扰和提高频谱利用率。 跳频控制器是跳频通信系统中的核心部件,具有跳频图案的产生、同步、自适应控制等功能。我们研制了超短波跳频通信系统中的跳频控制器。下面详细讨论其设计与实现。 2 跳频控制器设计 2 跳频控制器设计与实现 跳频通信是一种先进的通信方式,通过使用伪码序列来控制频率合成器,使得通信系统可以在多个频率之间快速切换,从而达到抗干扰和抗截获的效果。这种技术在军事电子战中有着重要的应用,同时也在民用通信中被用来提升频谱利用率和增强通信的稳定性。 跳频控制器作为跳频通信系统的关键组件,它的主要职责包括生成跳频图案、同步通信双方以及执行自适应控制。设计一个高效的跳频控制器,需要考虑以下几个主要的技术参数: 1. **跳频带宽**:控制器应支持较宽的跳频带宽,以覆盖所需的工作频率范围,如30MHz至87.975MHz。 2. **跳频频率数**:控制器应能够切换多个频率,例如256个不同的频率点,以实现更复杂的频谱利用策略。 3. **跳频速率**:快速的跳频速率可以提高通信的安全性和抗干扰能力,例如203跳/秒。 4. **跳频序列周期**:周期需足够长,超过1011bit,以增加破解的难度。 5. **同步时间**:首次同步时间应小于0.5s,迟后入网同步时间小于6s,保证通信效率和可靠性。 6. **同步可靠性**:在一定误码率下(如10^-1),保持较高的同步概率(如95%)。 7. **组网能力**:支持128个网络,并具有迟入网功能,适应多用户环境。 8. **跳频密钥量**:提供大量的跳频密钥,大于2^64,增加安全性。 在硬件系统的设计中,跳频控制器通常由以下几个模块组成: 1. **微处理器模块**:由87C51FB单片机为核心的CPU,负责生成控制信号,协调整个控制器的工作。 2. **基带模块**:包括射频音频接口、增量调制器、FIFO控制器、Bit同步器和伪随机码发生器,处理信号的编码和同步。 3. **接收模块**:包含相关器、同步检测器和TOD解码器,用于接收数据的处理和同步检测。 4. **定时模块**:提供精确的定时控制信号,确保跳频的准确执行。 5. **系统模块**:作为各个单元之间的接口,协调整个系统的运作。 跳频控制器的工作流程大致如下:数字化的发送信号经过FC的串入并出寄存器组织,由CPU存储并发送给FIFO。FC还有一个并入串出寄存器,数据从这里移出并发送给收发信机。同步信号和频率变化由FC根据预设的跳频图案控制,确保数据在正确的时间点发送。 设计一个基于单片机的跳频控制器,需要综合考虑各种技术参数,优化硬件模块设计,并确保通信的同步、可靠性和安全性。这样的控制器在现代通信系统中扮演着至关重要的角色,尤其是在对抗干扰和保障信息安全的场景中。

- 粉丝: 5

- 资源: 937

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功