AD9914中文翻译,高速DDS,翻译,中文文档

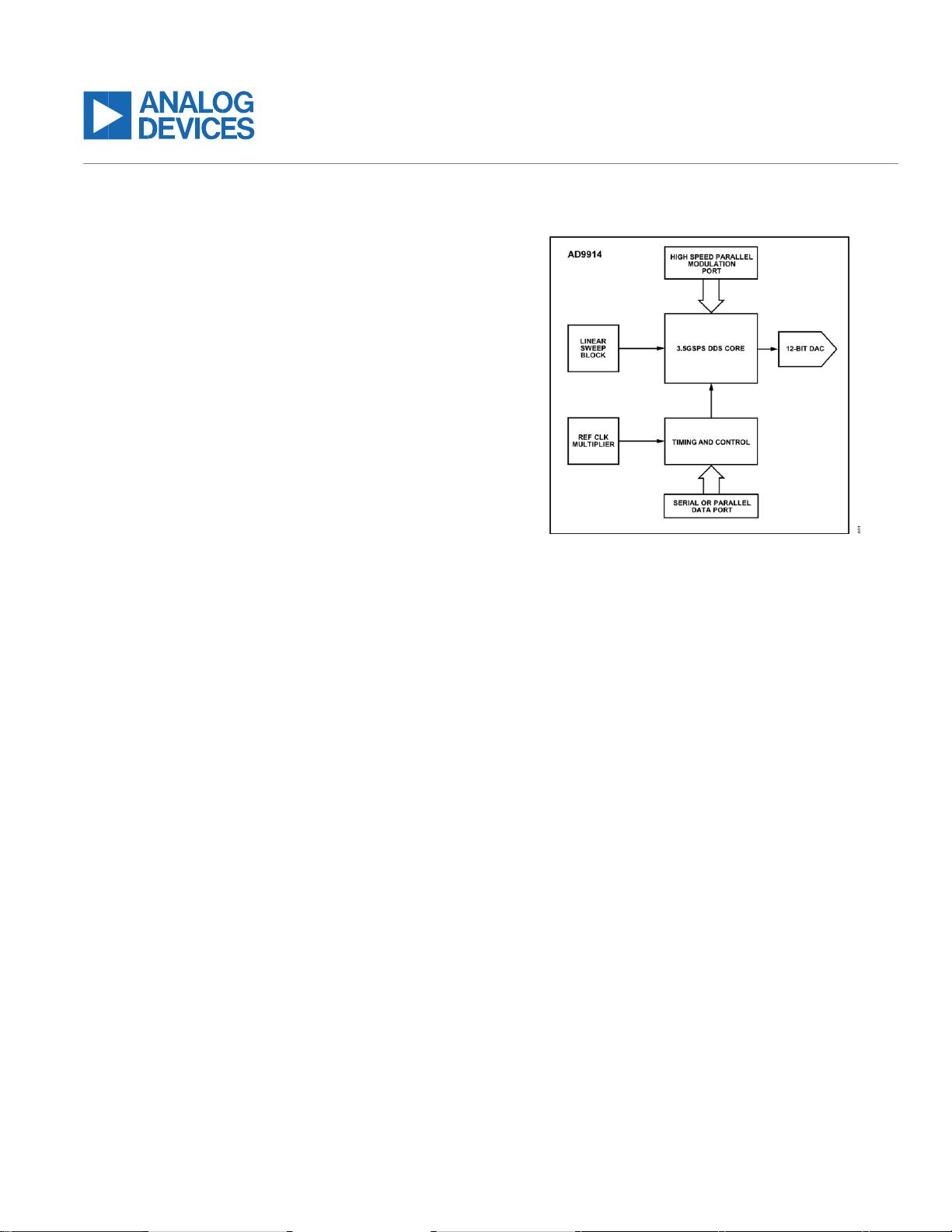

3.5 GSPS 内部时钟速度 ► 集成 12 位数字转换器 ► 频率调谐分辨率高达 190 pHz ► 16 位相位调谐分辨率 ► 12 位幅度缩放 ► 可编程模数 ► 自动线性和非线性扫频能力 ► 32 位并行数据路径接口 ► 8 个频率/相位偏移配置文件 ► 相位噪声:−128 dBc/Hz(1396 MHz 时偏移 1 kHz) ► 宽带 SFDR < −50 dBc ► 串行或并行输入/输出控制 ► 1.8 V/3.3 V 电源 ► 软件和硬件控制的关断 **AD9914**是一款高性能的直接数字频率合成器(DDS),专为需要高速、高精度频率合成的系统设计。这款芯片集成了多种高级功能,适用于多种应用领域,包括测试与测量、声光设备驱动、雷达和扫描系统等。 **主要特性:** 1. **3.5 GSPS(千兆样本每秒)内部时钟速度**:AD9914具有超快的内部采样率,能够在高频信号生成中提供卓越的性能。 2. **集成12位数字转换器**:内置的高分辨率DAC确保了信号质量,并提供了精细的频率和相位控制。 3. **频率调谐分辨率高达190 pHz**:这种极高的频率分辨率允许精确地设定和调整输出频率。 4. **16位相位调谐分辨率**:提供了对相位的微调能力,有助于生成更平滑的波形。 5. **12位幅度缩放**:能够调节输出信号的幅度,适应不同的应用需求。 6. **可编程模数**:用户可以通过编程设置不同的调制参数,实现灵活的信号生成。 7. **自动线性和非线性扫频能力**:自动扫频功能简化了系统调试和性能分析。 8. **32位并行数据路径接口**:并行接口提供了高速数据传输,提高了系统效率。 9. **8个频率/相位偏移配置文件**:支持多种预设配置,方便在不同工作模式间快速切换。 10. **低相位噪声:-128 dBc/Hz(1396 MHz时偏移1 kHz)**:这确保了信号的纯净度,对于要求低噪声的系统至关重要。 11. **宽带SFDR( spurious free dynamic range)< -50 dBc**:高的SFDR表明了AD9914在宽带信号生成时的出色动态性能。 12. **串行或并行输入/输出控制**:提供了灵活的控制接口选择,便于系统集成。 13. **1.8 V/3.3 V 电源**:低电压操作减少了功耗,同时也兼容各种电源系统。 14. **软件和硬件控制的关断**:支持通过软件或硬件控制芯片的开启和关闭,节省能源。 **应用场景:** - **敏捷本地振荡器频率合成**:在通信系统中,AD9914可以快速改变LO频率,适应多频段操作。 - **可编程时钟发生器**:为需要精确时钟信号的系统提供定制化解决方案。 - **雷达和扫描系统**:在雷达系统中,它可以生成线性调频连续波(LFCW)信号进行距离探测。 - **测试和测量设备**:作为高精度信号源,AD9914在实验室和生产测试环境中非常有用。 - **声光设备驱动器**:驱动声光调制器,实现高速数据传输。 - **极性调制器**:在光学调制应用中,它能够生成所需的调制信号。 **总结:** AD9914是一款高度集成的DDS芯片,具备高采样率、高分辨率和多种调制功能,适合需要高质量、高稳定性和灵活性的高频信号生成应用。其低相位噪声和宽带动态范围特性使其在通信、雷达和科学实验等领域表现出色。通过串行或并行接口的控制,AD9914能够轻松集成到各种系统架构中,提供便捷的配置和操作。

剩余59页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功