没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

CY7C63723是业界最小的Cypress专有M8控制器,内核集成的USB串行接口引擎和收发器;用于存储和数据缓冲的集成EPROM以及RAM;核心还包括可减少EMI的优化输出驱动器;另外要注意的是,此款控制具有内部小晶振,因此无需外部晶振或共鸣器;使鼠标电路设计能够更进一步简化;CY7C63723还集成了低速USB设备常见的其它片外元器件,如上拉电阻、唤醒电路和3.3V调压器;其主要作用就是将A2051生成的位移信号和按键系统的按键信号进行编码然后传输给PC主机;我们可以在几乎所有高集成度的光电鼠标上看到此款核心电路芯片。利用cypress半导体公司的CY7C63723 USB控制器芯片,设计并实现高性能的USB光电轨迹球的方法。由于USB接口具备连接简单、真正的即插即用以及热插拔等特点,使用USB接口的设备越来越普遍。本设计使用的CY7C63723 USB控制器芯片整合了USB SIE、通用I/O口以及USB优化R ISC内核,满足了USB的低价格、高性能两方面的要求,采用它能快速设计出低成本、高性能的光电输入部件,为输入部件的升级换代做出了有益的探索。

资源推荐

资源详情

资源评论

CY7C63722C

CY7C63723C

CY7C63743C

enCoRe™ USB Combination Low-Speed

USB and PS/2 Peripheral Controller

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document #: 38-08022 Rev. *E Revised April 15, 2011

Features

■ enCoRe™ USB - enhanced Component Reduction

❐ Internal oscillator eliminates the need for an external crystal

or resonator

❐ Interface can auto-configure to operate as PS/2 or USB with-

out the need for external components to switch between

modes (no General Purpose I/O [GPIO] pins needed to man-

age dual mode capability)

❐ Internal 3.3V regulator for USB pull-up resistor

❐ Configurable GPIO for real-world interface without external

components

■ Flexible, cost-effective solution for applications that combine

PS/2 and low-speed USB, such as mice, gamepads, joysticks,

and many others.

■ USB Specification Compliance

❐ Conforms to USB Specification, Version 2.0

❐ Conforms to USB HID Specification, Version 1.1

❐ Supports one low-speed USB device address and three data

endpoints

❐ Integrated USB transceiver

❐ 3.3V regulated output for USB pull-up resistor

■ 8-bit RISC microcontroller

❐ Harvard architecture

❐ 6-MHz external ceramic resonator or internal clock mode

❐ 12-MHz internal CPU clock

❐ Internal memory

❐ 256 bytes of RAM

❐ 8 Kbytes of EPROM

❐ Interface can auto-configure to operate as PS/2 or USB

❐ No external components for switching between PS/2 and

USB modes

❐ No GPIO pins needed to manage dual mode capability

■ I/O ports

❐ Up to 16 versatile GPIO pins, individually configurable

❐ High current drive on any GPIO pin: 50 mA/pin current sink

❐ Each GPIO pin supports high-impedance inputs, internal

pull-ups, open drain outputs or traditional CMOS outputs

❐ Maskable interrupts on all I/O pins

■ SPI serial communication block

❐ Master or slave operation

❐ 2 Mbit/s transfers

■ Four 8-bit Input Capture registers

❐ Two registers each for two input pins

❐ Capture timer setting with five prescaler settings

❐ Separate registers for rising and falling edge capture

❐ Simplifies interface to RF inputs for wireless applications

■ Internal low-power wake-up timer during suspend mode

❐ Periodic wake-up with no external components

■ Optional 6-MHz internal oscillator mode

❐ Allows fast start-up from suspend mode

■ Watchdog Reset (WDR)

■ Low-voltage Reset at 3.75V

■ Internal brown-out reset for suspend mode

■ Improved output drivers to reduce EMI

■ Operating voltage from 4.0V to 5.5VDC

■ Operating temperature from 0°C to 70°C

■ CY7C63723C available in 18-pin SOIC, 18-pin PDIP

■ CY7C63743C available in 24-pin SOIC, 24-pin PDIP, 24-pin

QSOP

■ CY7C63722C available in DIE form

■ Industry standard programmer support

[+] Feedback

CY7C63722C

CY7C63723C

CY7C63743C

Document #: 38-08022 Rev. *E Page 2 of 53

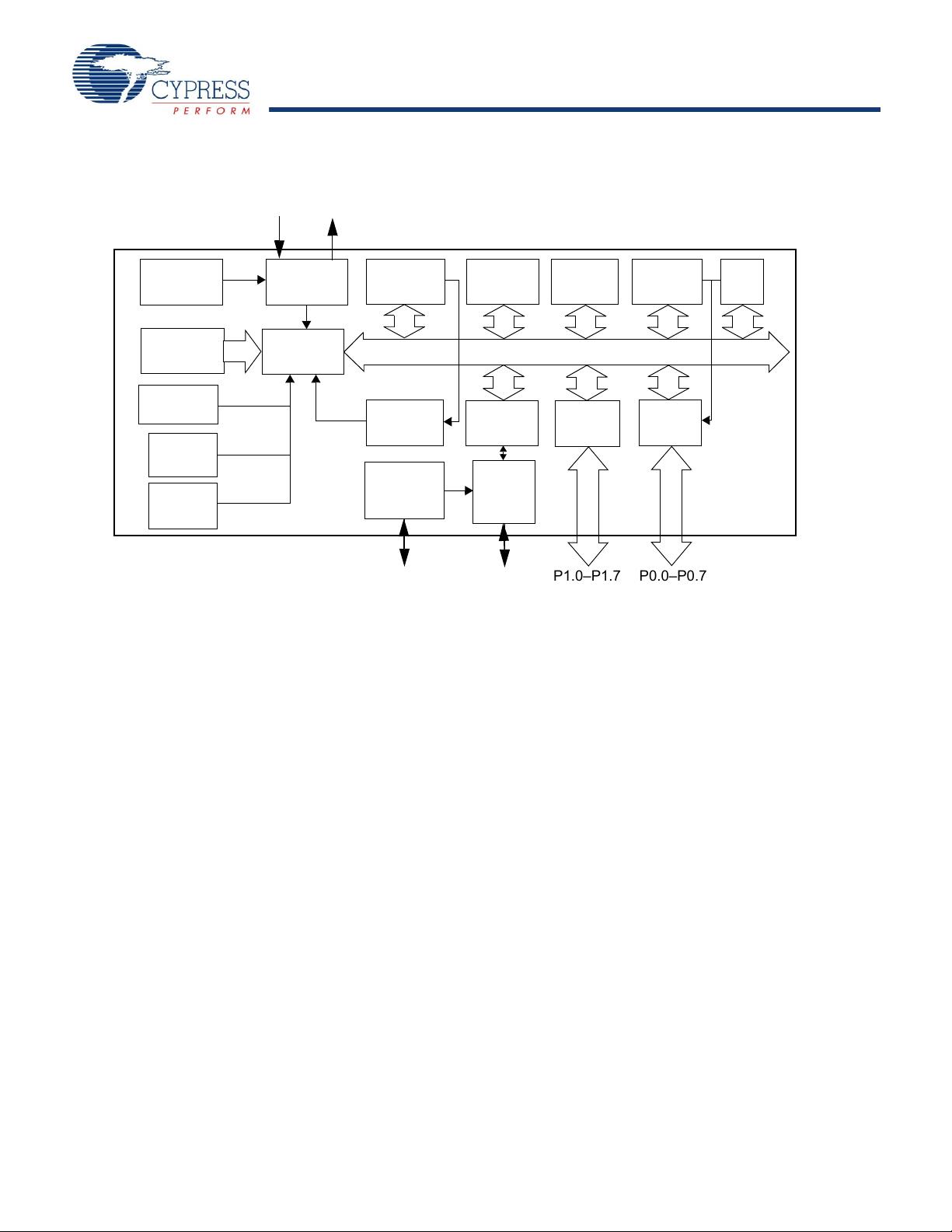

Logic Block Diagram

Functional Overview

enCoRe USB—The New USB Standard

Cypress has reinvented its leadership position in the low-speed

USB market with a new family of innovative

microcontrollers. Introducing...enCoRe USB—“enhanced

Component Reduction.” Cypress has leveraged its design

expertise in USB solutions to create a new family of low-speed

USB microcontrollers that enables peripheral developers to

design new products with a minimum number of components. At

the heart of the enCoRe USB technology is the breakthrough

design of a crystalless oscillator. By integrating the oscillator into

our chip, an external crystal or resonator is no longer needed.

We have also integrated other external components commonly

found in low-speed USB applications such as pull-up resistors,

wake-up circuitry, and a 3.3V regulator. All of this adds up to a

lower system cost.

The CY7C637xxC is an 8-bit RISC one-time-programmable

(OTP) microcontroller. The instruction set has been optimized

specifically for USB and PS/2 operations, although the microcon-

trollers can be used for a variety of other embedded applications.

The CY7C637xxC features up to 16 GPIO pins to support USB,

PS/2 and other applications. The I/O pins are grouped into two

ports (Port 0 to 1) where each pin can be individually configured

as inputs with internal pull-ups, open drain outputs, or traditional

CMOS outputs with programmable drive strength of up to 50 mA

output drive. Additionally, each I/O pin can be used to generate

a GPIO interrupt to the microcontroller. Note the GPIO interrupts

all share the same “GPIO” interrupt vector.

The CY7C637xxC microcontrollers feature an internal oscillator.

With the presence of USB traffic, the internal oscillator can be set

to precisely tune to USB timing requirements (6 MHz ±1.5%).

Optionally, an external 6-MHz ceramic resonator can be used to

provide a higher precision reference for USB operation. This

clock generator reduces the clock-related noise emissions

(EMI). The clock generator provides the 6- and 12-MHz clocks

that remain internal to the microcontroller.

The CY7C637xxC has 8 Kbytes of EPROM and 256 bytes of

data RAM for stack space, user variables, and USB FIFOs.

These parts include low-voltage reset logic, a Watchdog timer, a

vectored interrupt controller, a 12-bit free-running timer, and

capture timers. The low-voltage reset (LVR) logic detects when

power is applied to the device, resets the logic to a known state,

and begins executing instructions at EPROM address 0x0000.

LVR will also reset the part when V

CC

drops below the operating

voltage range. The Watchdog timer can be used to ensure the

firmware never gets stalled for more than approximately 8 ms.

The microcontroller supports 10 maskable interrupts in the

vectored interrupt controller. Interrupt sources include the USB

Bus-Reset, the 128-s and 1.024-ms outputs from the

free-running timer, three USB endpoints, two capture timers, an

internal wake-up timer and the GPIO ports. The timers bits cause

periodic interrupts when enabled. The USB endpoints interrupt

after USB transactions complete on the bus. The capture timers

interrupt whenever a new timer value is saved due to a selected

GPIO edge event. The GPIO ports have a level of masking to

select which GPIO inputs can cause a GPIO interrupt. For

additional flexibility, the input transition polarity that causes an

interrupt is programmable for each GPIO pin. The interrupt

polarity can be either rising or falling edge.

The free-running 12-bit timer clocked at 1 MHz provides two

interrupt sources as noted above (128 s and 1.024 ms). The

timer can be used to measure the duration of an event under

firmware control by reading the timer at the start and end of an

Wake-Up

12-bit

Timer

USB &

D+,D–

P1.0–P1.7

Interrupt

Controller

Port 0

P0.0–P0.7

GPIO

8-bit

RISC

Xtal

RAM

256 Byte

EPROM

8K Byte

Core

Brown-out

Reset

Xcvr

Watch

Timer

Dog

3.3V

Port 1

GPIO

Capture

Timers

USB

Engine

PS/2

Internal

Oscillator

Oscillator

Low

Reset

Voltage

Regulator

Timer

SPI

XTALOUT XTALIN/P2.1

VREG/P2.0

[+] Feedback

CY7C63722C

CY7C63723C

CY7C63743C

Document #: 38-08022 Rev. *E Page 3 of 53

event, and subtracting the two values. The four capture timers

save a programmable 8 bit range of the free-running timer when

a GPIO edge occurs on the two capture pins (P0.0, P0.1).

The CY7C637xxC includes an integrated USB serial interface

engine (SIE) that supports the integrated peripherals. The

hardware supports one USB device address with three

endpoints. The SIE allows the USB host to communicate with the

function integrated into the microcontroller. A 3.3V regulated

output pin provides a pull-up source for the external USB resistor

on the D– pin.

The USB D+ and D– USB pins can alternately be used as PS/2

SCLK and SDATA signals, so that products can be designed to

respond to either USB or PS/2 modes of operation. PS/2

operation is supported with internal pull-up resistors on SCLK

and SDATA, the ability to disable the regulator output pin, and an

interrupt to signal the start of PS/2 activity. No external compo-

nents are necessary for dual USB and PS/2 systems, and no

GPIO pins need to be dedicated to switching between modes.

Slow edge rates operate in both modes to reduce EMI.

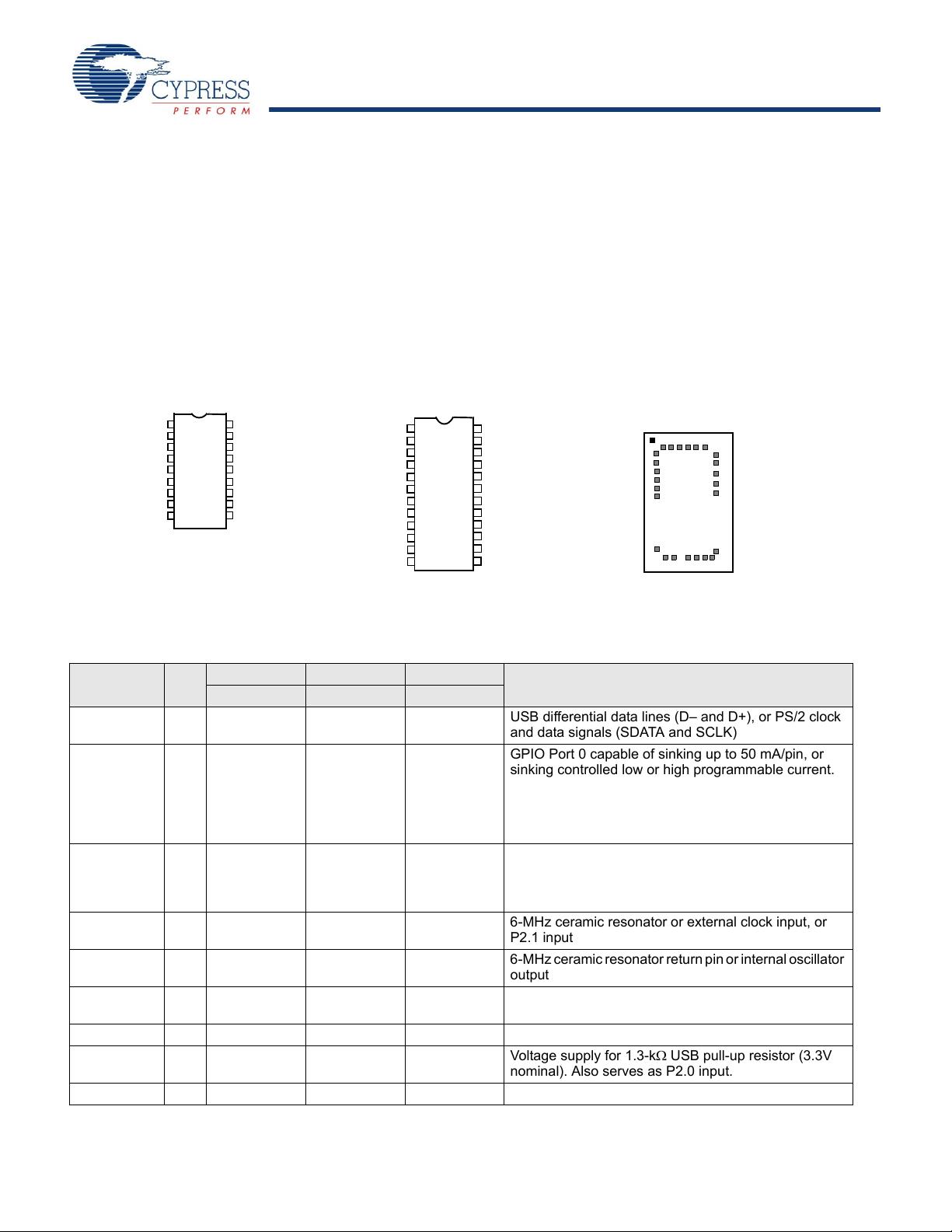

Pin Configurations

1

2

3

4

5

6

9

11

15

16

17

18

19

20

22

21

P0.0

P0.1

P0.2

P0.3

P1.0

P1.2

VSS

VREG/P2.0

P0.6

P1.5

P1.1

P1.3

D+/SCLK

P1.7

D–/SDATA

VCC

14

P0.7

10

VPP

XTALIN/P2.1

XTALOUT

12

13

7

8

P1.4

P1.6

24

23

P0.4

P0.5

24-pin SOIC/PDIP/QSOP

CY7C63743C

1

2

3

4

6

7

8

10

11

12

13

15

16

18

17

P0.0

P0.1

P0.2

P0.3

VSS

VREG/P2.0

P0.4

P0.6

P0.7

D+/SCLK

D–/SDATA

VCC

18-pin SOIC/PDIP

P0.5

9

VPP

XTALIN/P2.1

XTALOUT

CY7C63723C

5

14

P1.0

P1.1

Top View

4

5

6

7

8

9

3 P0.2

1 P0.0

2 P0.1

25 P0.4

24 P0.5

23 P0.6

22

21

20

19

18

11

12

13

14

15

16

17

P0.3

P1.0

P1.2

P1.4

P1.6

VSS

VSS

VPP

XTALIN/P2.1

VREG

XTALOUT

VCC

D-/SDATA

D+/SCLK

P0.7

P1.1

P1.3

P1.5

P1.7

CY7C63722C-XC

DIE

10

Pin Definitions

Name I/O

CY7C63723C CY7C63743C CY7C63722C

Description

18-Pin 24-Pin 25-Pad

D–/SDATA,

D+/SCLK

I/O 12

13

15

16

16

17

USB differential data lines (D– and D+), or PS/2 clock

and data signals (SDATA and SCLK)

P0[7:0] I/O 1, 2, 3, 4,

15, 16, 17, 18

1, 2, 3, 4,

21, 22, 23, 24

1, 2, 3, 4,

22, 23, 24, 25

GPIO Port 0 capable of sinking up to 50 mA/pin, or

sinking controlled low or high programmable current.

Can also source 2 mA current, provide a resistive

pull-up, or serve as a high-impedance input. P0.0 and

P0.1 provide inputs to Capture Timers A and B, respec-

tively.

P1[7:0] I/O 5, 14 5, 6, 7, 8,

17, 18, 19, 20

5, 6, 7, 8,

18, 19, 20, 21

IO Port 1 capable of sinking up to 50 mA/pin, or sinking

controlled low or high programmable current. Can also

source 2 mA current, provide a resistive pull-up, or

serve as a high-impedance input.

XTALIN/P2.1 IN 9 12 13 6-MHz ceramic resonator or external clock input, or

P2.1 input

XTALOUT OUT 10 13 14 6-MHz ceramic resonator return pin or internal oscillator

output

V

PP

7 10 11 Programming voltage supply, ground for normal

operation

V

CC

11 14 15 Voltage supply

VREG/P2.0 8 11 12 Voltage supply for 1.3-k USB pull-up resistor (3.3V

nominal). Also serves as P2.0 input.

V

SS

6 9 9, 10 Ground

[+] Feedback

CY7C63722C

CY7C63723C

CY7C63743C

Document #: 38-08022 Rev. *E Page 4 of 53

Programming Model

Refer to the CYASM Assembler User’s Guide for more details on

firmware operation with the CY7C637xxC microcontrollers.

Program Counter (PC)

The 14-bit program counter (PC) allows access for up to 8

Kbytes of EPROM using the CY7C637xxC architecture. The

program counter is cleared during reset, such that the first

instruction executed after a reset is at address 0x0000. This

instruction is typically a jump instruction to a reset handler that

initializes the application.

The lower 8 bits of the program counter are incremented as

instructions are loaded and executed. The upper six bits of the

program counter are incremented by executing an XPAGE

instruction. As a result, the last instruction executed within a

256-byte “page” of sequential code should be an XPAGE

instruction. The assembler directive “XPAGEON” will cause the

assembler to insert XPAGE instructions automatically. As

instructions can be either one or two bytes long, the assembler

may occasionally need to insert a NOP followed by an XPAGE

for correct execution.

The program counter of the next instruction to be executed, carry

flag, and zero flag are saved as two bytes on the program stack

during an interrupt acknowledge or a CALL instruction. The

program counter, carry flag, and zero flag are restored from the

program stack only during a RETI instruction.

Please note the program counter cannot be accessed directly by

the firmware. The program stack can be examined by reading

SRAM from location 0x00 and up.

8-bit Accumulator (A)

The accumulator is the general-purpose, do everything register

in the architecture where results are usually calculated.

8-bit Index Register (X)

The index register “X” is available to the firmware as an auxiliary

accumulator. The X register also allows the processor to perform

indexed operations by loading an index value into X.

8-bit Program Stack Pointer (PSP)

During a reset, the program stack pointer (PSP) is set to zero.

This means the program “stack” starts at RAM address 0x00 and

“grows” upward from there. Note that the program stack pointer

is directly addressable under firmware control, using the MOV

PSP,A instruction. The PSP supports interrupt service under

hardware control and CALL, RET, and RETI instructions under

firmware control.

During an interrupt acknowledge, interrupts are disabled and the

program counter, carry flag, and zero flag are written as two

bytes of data memory. The first byte is stored in the memory

addressed by the program stack pointer, then the PSP is incre-

mented. The second byte is stored in memory addressed by the

program stack pointer and the PSP is incremented again. The

net effect is to store the program counter and flags on the

program “stack” and increment the program stack pointer by two.

The return from interrupt (RETI) instruction decrements the

program stack pointer, then restores the second byte from

memory addressed by the PSP. The program stack pointer is

decremented again and the first byte is restored from memory

addressed by the PSP. After the program counter and flags have

been restored from stack, the interrupts are enabled. The effect

is to restore the program counter and flags from the program

stack, decrement the program stack pointer by two, and reenable

interrupts.

The call subroutine (CALL) instruction stores the program

counter and flags on the program stack and increments the PSP

by two.

The return from subroutine (RET) instruction restores the

program counter, but not the flags, from program stack and

decrements the PSP by two.

Note that there are restrictions in using the JMP, CALL, and

INDEX instructions across the 4-KByte boundary of the program

memory. Refer to the CYASM Assembler User’s Guide for a

detailed description.

8-bit Data Stack Pointer (DSP)

The data stack pointer (DSP) supports PUSH and POP instruc-

tions that use the data stack for temporary storage. A PUSH

instruction will pre-decrement the DSP, then write data to the

memory location addressed by the DSP. A POP instruction will

read data from the memory location addressed by the DSP, then

post-increment the DSP.

During a reset, the Data Stack Pointer will be set to zero. A PUSH

instruction when DSP equals zero will write data at the top of the

data RAM (address 0xFF). This would write data to the memory

area reserved for a FIFO for USB endpoint 0. In non-USB appli-

cations, this works fine and is not a problem.

For USB applications, the firmware should set the DSP to an

appropriate location to avoid a memory conflict with RAM

dedicated to USB FIFOs. The memory requirements for the USB

endpoints are shown in Section . For example, assembly instruc-

tions to set the DSP to 20h (giving 32 bytes for program and data

stack combined) are shown below.

MOV A,20h ; Move 20 hex into Accumulator (must be D8h

or less to avoid USB FIFOs)

SWAP A,DSP ; swap accumulator value into DSP register

Address Modes

The CY7C637xxC microcontrollers support three addressing

modes for instructions that require data operands: data, direct,

and indexed.

Data

The “Data” address mode refers to a data operand that is actually

a constant encoded in the instruction. As an example, consider

the instruction that loads A with the constant 0x30:

■ MOV A, 30h

This instruction will require two bytes of code where the first byte

identifies the “MOV A” instruction with a data operand as the

second byte. The second byte of the instruction will be the

constant “0xE8h”. A constant may be referred to by name if a

prior “EQU” statement assigns the constant value to the name.

For example, the following code is equivalent to the example

shown above.

■ DSPINIT: EQU 30h

[+] Feedback

CY7C63722C

CY7C63723C

CY7C63743C

Document #: 38-08022 Rev. *E Page 5 of 53

■ MOV A,DSPINIT

Direct

“Direct” address mode is used when the data operand is a

variable stored in SRAM. In that case, the one byte address of

the variable is encoded in the instruction. As an example,

consider an instruction that loads A with the contents of memory

address location 0x10h:

■ MOV A, [10h]

In normal usage, variable names are assigned to variable

addresses using “EQU” statements to improve the readability of

the assembler source code. As an example, the following code

is equivalent to the example shown above.

■ buttons: EQU 10h

■ MOV A, [buttons]

Indexed

“Indexed” address mode allows the firmware to manipulate

arrays of data stored in SRAM. The address of the data operand

is the sum of a constant encoded in the instruction and the

contents of the “X” register. In normal usage, the constant will be

the “base” address of an array of data and the X register will

contain an index that indicates which element of the array is

actually addressed.

■ array: EQU 10h

■ MOV X,3

■ MOV A, [x+array]

This would have the effect of loading A with the fourth element

of the SRAM “array” that begins at address 0x10h. The fourth

element would be at address 0x13h.

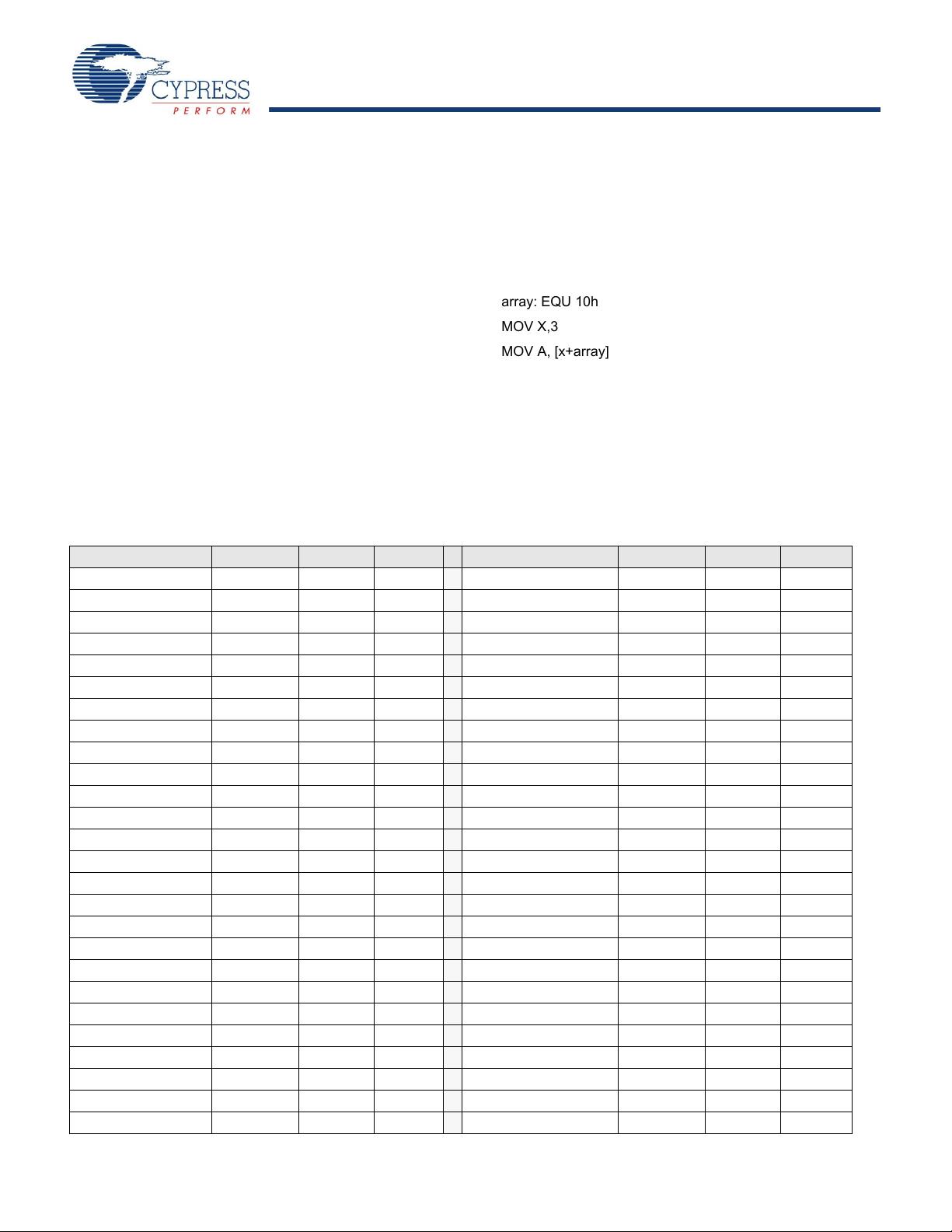

Instruction Set Summary

Refer to the CYASM Assembler User’s Guide for detailed infor-

mation on these instructions. Note that conditional jump instruc-

tions (i.e., JC, JNC, JZ, JNZ) take five cycles if jump is taken, four

cycles if no jump.

MNEMONIC Operand Opcode Cycles MNEMONIC Operand Opcode Cycles

HALT 00 7

NOP 20 4

ADD A,expr data 01 4

INC A acc 21 4

ADD A,[expr] direct 02 6 INC X x 22 4

ADD A,[X+expr] index 03 7

INC [expr] direct 23 7

ADC A,expr data 04 4

INC [X+expr] index 24 8

ADC A,[expr] direct 05 6 DEC A acc 25 4

ADC A,[X+expr] index 06 7

DEC X x 26 4

SUB A,expr data 07 4

DEC [expr] direct 27 7

SUB A,[expr] direct 08 6 DEC [X+expr] index 28 8

SUB A,[X+expr] index 09 7

IORD expr address 29 5

SBB A,expr data 0A 4

IOWR expr address 2A 5

SBB A,[expr] direct 0B 6

POP A 2B 4

SBB A,[X+expr] index 0C 7

POP X 2C 4

OR A,expr data 0D 4

PUSH A 2D 5

OR A,[expr] direct 0E 6

PUSH X 2E 5

OR A,[X+expr] index 0F 7

SWAP A,X 2F 5

AND A,expr data 10 4

SWAP A,DSP 30 5

AND A,[expr] direct 11 6

MOV [expr],A direct 31 5

AND A,[X+expr] index 12 7

MOV [X+expr],A index 32 6

XOR A,expr data 13 4

OR [expr],A direct 33 7

XOR A,[expr] direct 14 6

OR [X+expr],A index 34 8

XOR A,[X+expr] index 15 7

AND [expr],A direct 35 7

CMP A,expr data 16 5

AND [X+expr],A index 36 8

CMP A,[expr] direct 17 7

XOR [expr],A direct 37 7

CMP A,[X+expr] index 18 8

XOR [X+expr],A index 38 8

MOV A,expr data 19 4

IOWX [X+expr] index 39 6

[+] Feedback

剩余52页未读,继续阅读

资源评论

走在茫然的路上

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 三菱FX3U PLC与台达变频器通讯:Modbus RTU协议下的昆仑通态触摸屏控制程序详解,三菱FX3U与台达变频器通讯 器件:三菱FX3U PLC+FX3U 485BD板,台达VFD变频器,昆仑

- 源荷协同优化的低碳性挖掘:运用多时间尺度调度克服碳捕集电厂局限,基于matlab+cplex仿真平台,提升系统低碳性能,内容:挖掘源荷两侧低碳资源并分析其低碳性,荷侧调用不同响应速度的价格型、激励型需

- mongodb可视化工具(兼容较低版本使用)

- 三相异步电机Simulink仿真:中南大学与山河智能合作开发电动叉车高实用性仿真模型与文献分享,三相异步电机simulink仿真 中南大学与山河智能合作开发电动叉车的校企合作项目的仿真模型,感应电机F

- 新时达软件上位机:全协议支持,解除限制,灵活设置运行,电脑调试系统便捷高效,新时达软件上位机,256全协议,007软件 能解除主板限制,能解除轿厢锁 能人为设置运行限制 新时达电脑调试软件多协议,方便

- Comsol光栅波导耦合器:高效耦合效率计算与经典复古小案例,Comsol光栅波导耦合器,耦合效率计算 经典复古小案例 ,核心关键词:Comsol光栅波导耦合器; 耦合效率计算; 经典复古; 小案

- 文件批量重命名工具.exe

- linux系统下安装sysstat以及依赖的cpp

- 半挂汽车列车横向稳定性控制研究:低附路面下的三工况仿真分析与模糊PID等算法应用基于Trucksim与Simulink联合仿真参考论文,半挂汽车列车4自由度6轴整车model,横向稳定性控制,在低附着

- 基于动态粒子群算法的动态环境寻优算法:随机初始化粒子群,适应度评价搜索最优解,Matlab基于动态粒子群算法的动态环境寻优算法 基本粒子群算法首先是在解空间中随机初始化所有粒子,每个粒子位置即代表问题

- 双碳背景下基于Matlab的综合能源系统低碳优化调度策略研究:涉及新能源消纳等多元素综合优化分析,双碳+24小时分时综合能源系统低碳优化调度(用Matlab+Yalmip+Cplex) 包含新能源消纳

- 参考资料-治理环境、企业寻租与交易成...公司非生产性支出的经验证据.pdf

- [整站程序]LDU v702汉化版_ldu702hh.rar

- 基于lunwen的四永磁同步电机相邻耦合转速同步控制Simulink仿真模型优化与二次开发建议,根据lunwen搭建的四永磁同步电机相邻耦合转速同步控制simulink仿真模型 采用的是PI算法跟随

- Java + LibreOffice + Excel转换为PDF + 工具类

- [整站程序]MyTopix v1.3.0简体中文版_mytopix_v_130.rar

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功