没有合适的资源?快使用搜索试试~ 我知道了~

摘要:本系统基于数字存储示波器的基本原理,以单片机和FPGA组成的最小系统为控制核心,具有实时采样方式和等效采样方式,其实时采样速率≤并采用顺序等效采样的方式使

资源详情

资源评论

资源推荐

- 第 1 页 -

数字示波器

摘要 :本系统基于数字存储示波器的基本原理,以单片机和 FPGA组成的最小系

统为控制核心,具有实时采样方式和等效采样方式,其实时采样速率≤ 1MSa/s,

并采用顺序等效采样的方式使等效采样速率达到 200MSa/s。系统输入频率范围

为 10Hz~10MHz,输入幅值范围为 4mvVpp~8vVpp,周期测量精度优于 0.1%,

幅值测量误差小于 5%。系统具有三档垂直灵敏度和七档水平灵敏度,采用内触

发方式, 触发电平可通过外部旋钮进行调节,同时也具有单次触发功能。能够对

波形进行存储, 并且能在需要时调出存储波形进行回放。 系统在模拟示波器上显

示波形和刻度,并且借助于 128*64 点阵液晶显示示波器参数及波形信息,功能

稳定,波形清晰,人机界面友好。

关键词: 数字存储示波器,实时采样,等效采样,取样保持

一、方案论证与选择

系统要求制作一台实时采样方式和等效采样方式的数字示波器, 要求测量周

期信号的频率范围为 10Hz~10MHz,实时采样速率≤ 1MSa/s,等效采样速率≥

200MSa/s,要求包含三档水平扫描速率和三档垂直灵敏度, 采用内触发方式, 触

发电平可调, 可扩展存储和单次触发的功能, 并能对信号进行幅值和频率的实时

测量。

1. 采样方式选择

一般示波器有两种采样方式,实时采样和等效时间采样。

方案一: 实时采样。实时采样是在信号存在周期对其采样,故都是在信号经

历的实际时间内显示信号波形。 根据采样定理, 采样速率必须高于信号最高频率

分量的2倍。对于周期的正弦信号, 一个周期内至少应该有2个采样点。 为了不

失真的恢复原被测信号, 通常一个周期内就需要采样8个点以上。 其优点是采样

时间较短,缺点是对 A/D 转换其的速度和精度要求很高。

方案二 :等效时间采样。使用等效采样法的前提是被测信号是周期出现的,

因此,为了重建原信号, 可以每一个周期内等效地等间隔地抽取少量的样本, 最

后将多个周期抽取的样本集合到同一个周期内, 这样就可以等效成在一个被测信

号周期内采样效果。 该方案的优点是采样频率不需要太高, 与被采样信号频率相

当即可,缺点是要求被测信号是周期的,而且采样过程较慢,比较耗时。

根据题目要求我们选择实时采样和等效采样相结合的方式,实时采样速率

≤1MSa/s,即限制了 A/D 转换器的速率为≤ 1MSa/s,题目要求水平分辨率至少

为 20 点/div,故我们 50KHz 以下采用实时采样方式, 50KHz~10MHz 采用等效时

间采样方式,最高等效采样速率可达到 200MSa/s。

2.触发方案选择

为了在示波器上显示稳定的波形, 必须利用触发使扫描信号与被观测信号保

持同步关系, 即当满足触发条件时才启动一次扫描。我们采用内触发方式,即以

输入的被测信号作为触发源,且采用上升沿触发。

- 第 2 页 -

方案一: 采用比较器实现,当信号大于所设比较触发电平时, 即产生一次触

发。但是被测信号为 10Hz~10MHz,对比较器的要求较高,而且比较器的边沿

容易产生抖动,导致触发不稳。

方案二:通过数字电路电路实现。 在 FPGA 中可通过软件将触发电平写入一

个寄存器中,通过 A/D 对信号进行实时采样,并与该寄存器的值进行比较当大

于改值时即产生一个触发脉冲。

由于方案二可排除硬件毛刺产生的干扰, 触发和波形较稳定, 且易实现触发

电压的调整,故采用方案二。

3.频率测量

方案一: 测周法,即以待测信号为门限,用计数器记录在此门限内的高频标

准时钟脉冲数, 从而确定待测信号的频率。 当选定高频时钟脉冲而被测信号频率

较低时可以获得很高的精度, 而被测信号频率过高时由于测量时间不够会有精度

不够的问题,适用于低频信号的测量。

方案二:相关计数测频法 (等精度测频法 )。这种方法和测周法很相似,不同

的是测周法测量时间为被测信号的一个周期, 不是固定值, 测较高频率时测量时

间过短,造成精度不够;而等精度测量法的测量时间并不是被测信号的一个周期,

而是人为设定的一段时间。 闸门的开启和闭合由被测信号的上升沿来控制, 测量

精度与被测信号频率无关,因而可以保证在整个测量频段内的测量精度保持不

变。我们采用方案二,可使在 10Hz~10MHz 输入信号范围测频精度相等。

4.幅值测量

方案一:峰值检波法。 通过峰值检波器将输入信号的峰值转换为直流信号输

出,然后通过 AD 采样测的其幅值。但是峰值检波器在低频段的精度较低。

方案二:数字方法,通过 A/D 转换器对其采样,然后对采样数据进行处理

得到信号的幅值。该方案受 A/D 转换器的速率的限制,当信号频率升高时,其

精度会由于采样点数减少而降低。

我们决定采用两种方案相结合的方法对信号的峰值进行测量, 以提高幅值测

量的在整个频段范围内的精度,使电压测量误差小于 5%。

- 第 3 页 -

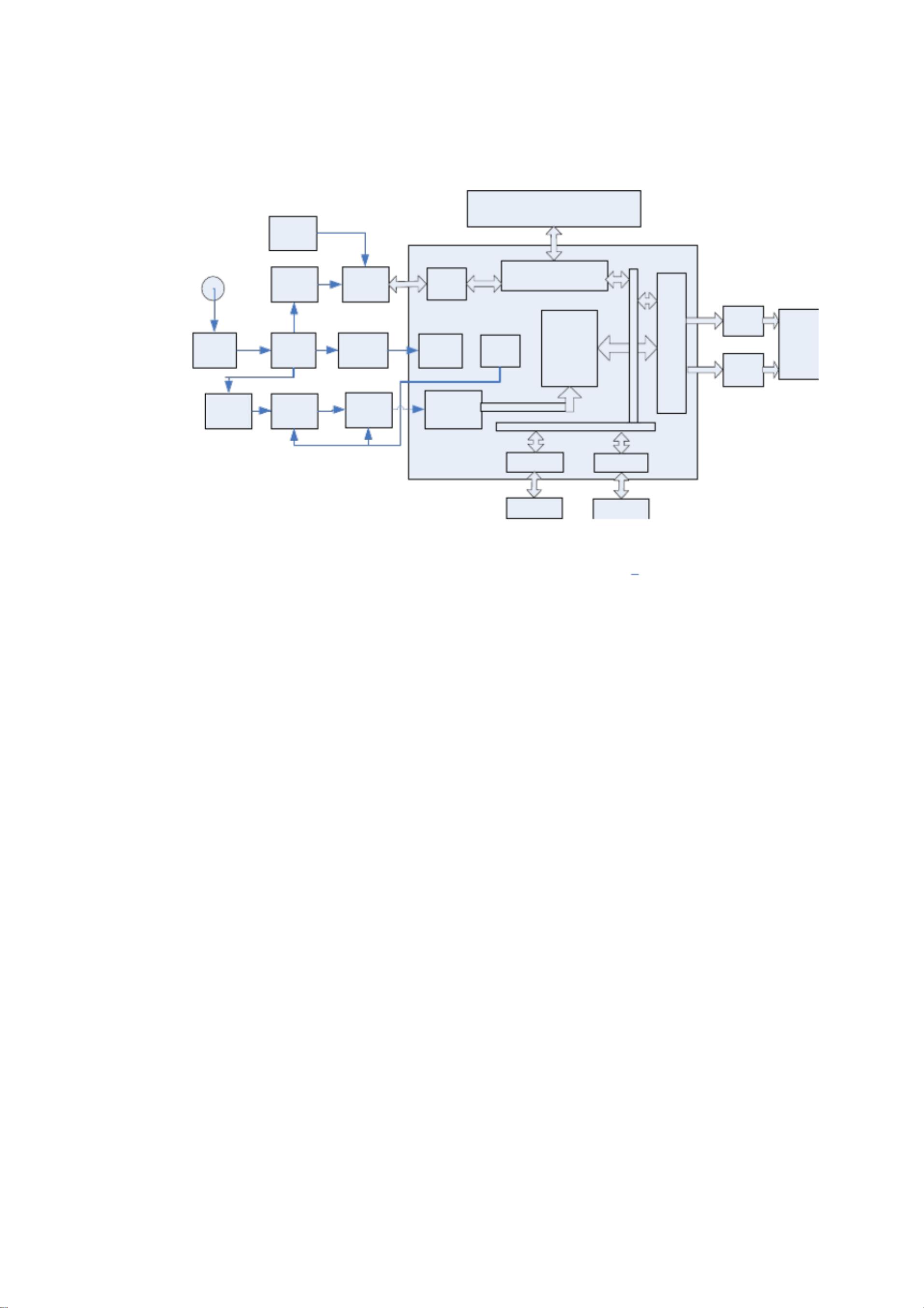

二、系统总体设计方案及实现方框图;

阻抗

匹配

程控

放大

测频

加法器

采样保持

电路

MAX118

峰值检

波

MCU(AT89S52)

Max197

采样控

制

双口

RAM

波形

显示

控制

模块

键盘扫描

显示驱动

行扫描

D/A

列扫描

D/A

模拟

示波

器

键盘

128*64点阵

显示

MAX197

等精度

测频

波形数据

存储控制

采样控

制

总线控制

触发电平

调节

FPGA

输入

图 1 系统总体框图

系统框图如图 1 所示,系统以单片机 AT89S52和 FPGA为控制核心。被测

10Hz~10MHz信号经由射极跟随器构成的阻抗匹配电路输入系统,为实现三档垂

直灵敏度,共设置三级程控放大电路, 然后信号经加法器变为单极性信号, 经设

计的采样保持电路送入 A/D 转换器进行采样。 A/D 转换器采用 1Msps采样速率 8

位的 MAX118。同时程控放大后的信号经测频整形电路送入 FPGA进行测频,并经

峰值检波电路由 12 位 A/DMAX197采样,进行幅值测量。 同时 MAX197采样触发电

平调节电位器电压,实现触发电平的调节。 FPGA内部实现等精度测频,当所测

频率小于 50KHz时即采用实时采样, 当所测频率大于 50KHz时,采用等效时间采

样。采样所得数据由波形数据存储控制模块写入 FPGA内部,同时由波形显示控

制模块将数据读出,送入列扫描电路, 行扫描电路产生扫描电压, 在模拟示波器

上显示出信号波形。 可以实现连续触发显示和单次触发显示, 并能实现波形的存

储与回放。

三、理论分析与计算

1. 等效采样分析

等效时间采样是一种用低频信号采样高频信号的一种方法,即对每个周期

仅采样一个点, 经过若干个周期后就可对信号各个部分采样一遍, 而这些点可以

借助步进延迟方法均匀地分布于信号波形的不同位置。设输入信号 f (t )(t) 的

周期为 T(频率为 f ),若将 f (t )的一个周期 T 以△t 等分,则在采样时钟周期

为 Tc,且 Tc=m×T+△ t (m为正整数)时,在经过 k 个时钟周期后,

且 k=T/ △t ,

f(kTc) =k(m×T+△ t )= T/ △t (m×T+△ t )= T(mk+1)

即实现了对信号 f (t )一个周期 k个点的等效采样,等效采样频率为 k×f ,实时

剩余10页未读,继续阅读

王佛伟

- 粉丝: 13

- 资源: 320

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0