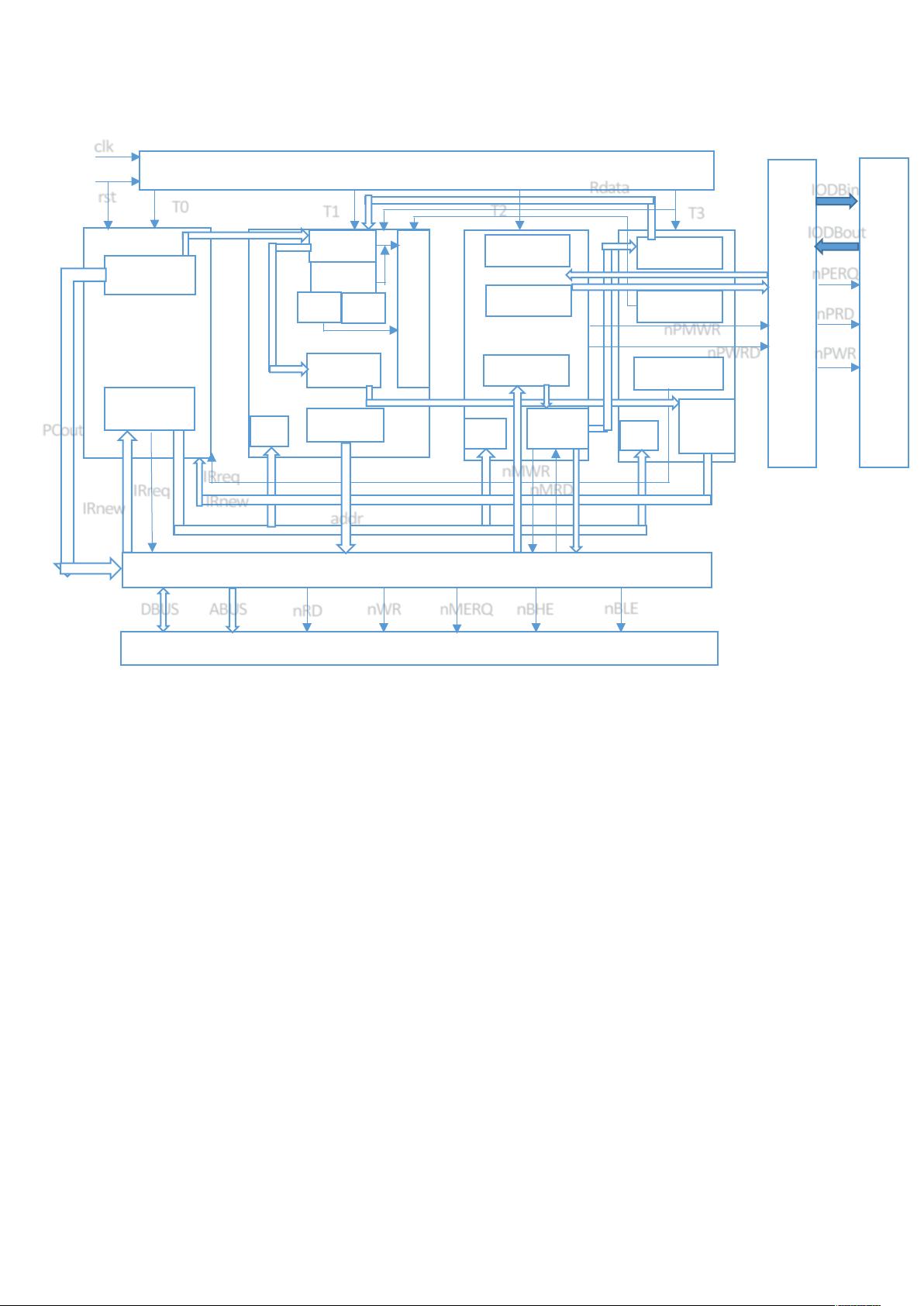

CPU(中央处理器)是计算机硬件系统的核心部件,它负责执行指令和处理数据。"CPU设计原理图1"可能是一个详细展示CPU内部结构和工作流程的图表。以下将根据描述和标签,结合CPU的一般设计原理,来阐述相关知识点。

1. **时钟控制模块**:CPU的操作是同步进行的,由时钟信号驱动。时钟控制模块产生精确的时钟脉冲,这些脉冲决定了CPU的运行速度和所有内部操作的节奏。时钟频率通常用来衡量CPU的性能。

2. **取址模块(PC - 程序计数器)**:程序计数器存储下一条要执行指令的内存地址。在每条指令执行完毕后,PC通常会自动增加,指向下一条指令的地址,除非遇到转移指令。

3. **IR(指令寄存器)**:存储当前正在执行的指令。当CPU从内存取出指令时,指令会先被放入IR。

4. **运算模块**:执行算术和逻辑运算,包括加法、减法、位操作等。运算结果可能被写回至寄存器或内存。

5. **存储模块**:CPU内部有高速缓存(如L1、L2缓存),用于临时存储频繁访问的数据,提高数据存取速度。这部分可能还包括主存接口,用于与外部主存交换数据。

6. **回写模块**:在指令执行后,可能会更新某些寄存器或内存单元,回写模块负责完成这个任务。

7. **I/O控制模块**:管理与外设(如显示器、键盘、硬盘等)的通信。输入/输出(I/O)操作通常通过数据总线(如DBUS)进行。

8. **访存控制模块**:决定何时读取或写入主存,处理内存访问请求。包括读使能(RDn)、写使能(WRn)和总线请求(如MERQn,内存请求信号)等信号。

9. **寄存器和总线**:例如,IOR(输入寄存器)、Rtmp(暂存寄存器)等,用于暂时存储数据。总线(如ABUS、DBUS)是CPU内部和外部设备之间传输数据的通道。

10. **控制信号**:如nBHE(高有效位标志)、nMWR(内存写信号)、nMRD(内存读信号)、nPRD(外围设备读信号)等,用于协调CPU和其它组件的操作。

11. **状态和条件码**:如IRRdata、Rupdate等,反映指令执行的状态,比如是否溢出、进位等,这些信息对分支和跳转决策至关重要。

12. **流水线技术**:现代CPU通常采用指令流水线技术,将CPU操作分为多个阶段(如T0-T3),使得多条指令可以同时在不同的阶段并行处理,提高执行效率。

以上知识点涵盖了CPU设计中的关键部分,实际的"CPU设计原理图1"会更详细地展示各组件间的连接和交互方式。理解这些原理对于深入学习计算机体系结构和硬件设计非常重要。