实验2单周期CPU取指译码实验指导书1

需积分: 0 128 浏览量

更新于2022-08-08

收藏 530KB DOCX 举报

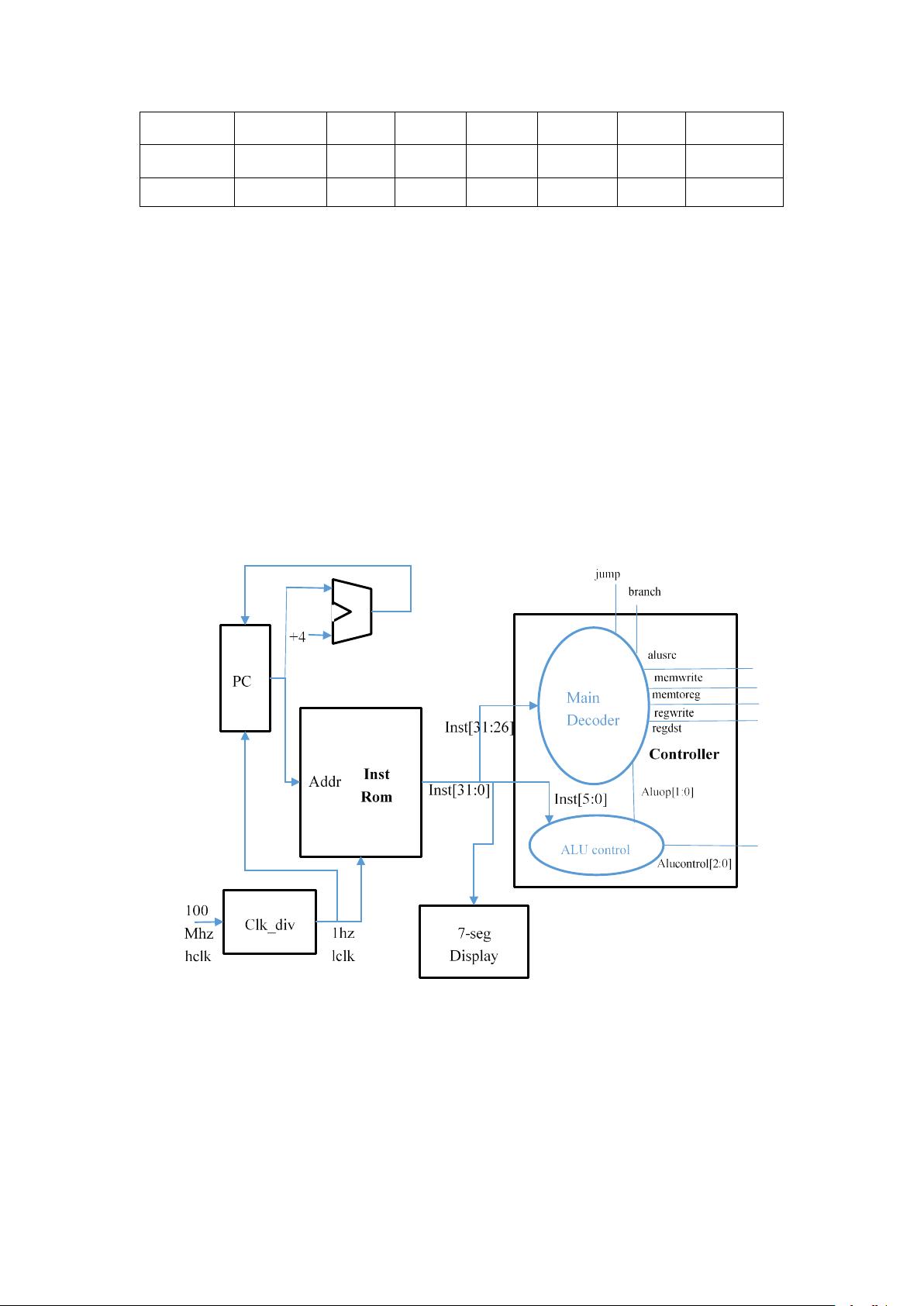

实验二的“单周期CPU取指译码”是计算机体系结构中的一个重要环节,主要涉及MIPS架构的CPU操作流程。MIPS CPU的传统执行流程包括五个阶段:取指(IF)、译码(DE)、执行(EXE)、访存(MEM)和回写(WB)。在本次实验中,我们将关注取指和译码阶段。

取指阶段由程序计数器(PC)执行,它随着每个时钟周期自动递增,输出地址和使能信号给指令存储器(Inst_Rom)。PC的输出地址用于读取指令存储器中相应位置的指令。如果选择了按字节使能,PC会递增4个字节来获取下一条指令,否则仅递增1个字节。

接下来是译码阶段,取出的指令需要被解码以确定其类型和操作。控制器是这一过程的关键,它通过生成各种控制信号来协调CPU的数据通路,确保指令正确执行。控制器主要由main_decoder和alu_decoder两部分组成,它们负责产生如Memtoreg、memwrite、pcsrc、alusrcreg、regdst、regwrite、jump等控制信号,这些信号对应于MIPS指令的不同操作。

实验设备包括一台PC机,一个计算机系统能力培养实践平台,如MINISYS定制开发板或Nexys4 DDR实验开发板,以及Xilinx Vivado开发套件。实验内容包括实现PC模块、Controller模块、Block Memory Generator IP核构建的指令存储器,以及将指令显示在7段数码管上的功能。此外,还需要通过仿真程序验证取指和译码阶段的正确性,使用时钟分频器调整时钟频率,并在顶层(top)将所有模块正确连接。

在实验原理图中,取指阶段的PC是一个32位寄存器,每执行完一条指令,其值加4以指向下一条指令。在指令译码阶段,MIPS指令的[31:16]字段是opcode,[5:0]字段是funct,这两者用于识别指令类型并生成相应的控制信号。例如,opcode为01表示R-type指令,funct字段可以进一步决定ALU的操作,如加法、减法、逻辑与、逻辑或等。

控制器实现原理涉及到多个控制信号的产生,例如Led[0]表示是否需要回写到寄存器堆,Led[1]表示是否需要写数据到存储器,Led[2]指示PC是否需要跳转,Led[3-4]用于立即数的32位扩展,Led[5-6]用于区分rt或rd寄存器,Led[7:9]则与ALU控制信号有关。

通过这个实验,学生将深入理解单周期CPU的工作原理,特别是控制器如何生成和协调控制信号,以及如何在硬件层面实现取指和译码的过程。这有助于他们对计算机底层运作的理解,为后续的学习打下坚实的基础。

小米智能生活

- 粉丝: 46

- 资源: 300