没有合适的资源?快使用搜索试试~ 我知道了~

1.设计概述 - 2 - 2.设计内部实现逻辑 - 2 - 3.设计描述 - 4 - 2.设计显示小时、分钟、秒数的值“timer.vhd”的端口、内部 VHD

资源详情

资源评论

资源推荐

2016 年《综合课程设计 2-1》课程实验报告(第三类实验)

实验题四:设计一个能显示时、分、秒

的实时时钟

姓名:王科

学号:1310583

专业:计算机科学与技术

完成日期:2016/4/10

- 1 -

目录

一、 实验内容 ...................................................................................................................................... - 2 -

二、 实验原理 ...................................................................................................................................... - 2 -

1.设计概述 ........................................................................................................................................... - 2 -

1.1 输入输出特性表 ................................................................................................................ - 2 -

1.2 设计外部端口 .............................................................................................................................. - 2 -

2.设计内部实现逻辑 ........................................................................................................................ - 2 -

2.1 信号产生器“singal_generator.vhd” .................................................................. - 3 -

2.2 显示正确的小时、分钟、秒数的值“timer.vhd”.............................................. - 3 -

2.3 顶层文件“clock.bdf” ................................................................................................ - 3 -

3.设计描述 ........................................................................................................................................... - 4 -

三、 实验步骤 ...................................................................................................................................... - 4 -

1.设计信号产生器“singal_generator.vhd”的端口、内部 VHDL 逻辑程序 ............ - 4 -

2.设计显示小时、分钟、秒数的值“timer.vhd”的端口、内部 VHDL 逻辑程序 ..... - 5 -

3.使用图形化方法设计原理图 ...................................................................................................... - 7 -

4.观察 FPGA 电路板,将输入输出端口进行引脚绑定 .......................................................... - 7 -

5.电路连接示意图 ............................................................................................................................. - 8 -

6.实验结果 ........................................................................................................................................... - 9 -

四、 实验原理图和 vhdl 程序 ...................................................................................................... - 11 -

1.整体原理图(“clock.bdf”) ............................................................................................. - 11 -

2.元部件 1(“singal_generator.vhd”).......................................................................... - 11 -

3.元部件 2(“timer.vhd”) ................................................................................................... - 12 -

五、 实验总结 .................................................................................................................................... - 17 -

1.实验遇到的问题 ........................................................................................................................... - 17 -

2.实验感悟 ......................................................................................................................................... - 17 -

- 2 -

一、 实验内容

本次实验是使用图形设计方法与 VHDL 编程相结合在 FPGA 芯片内构建独立逻

辑实验,要求设计一个能显示时、分、秒的实时时钟,通过 FPGA 板上的数码管

显示。初始时间为 0 时 0 分 0 秒。

二、 实验原理

1.设计概述

按照实验内容要求,设计一个实时显示时间的时钟,其初始时间为 0 时 0

分 0 秒,设计一个 reset 和 stop 按钮,当按下 reset 时,时间自动清零,当按

下 stop 时,时钟暂停跳动,再次按下时恢复跳动,其输入输出特性如下图:

1.1 输入输出特性表

INPUT

OUTPUT

clk

reset

stop

hourH

hourL

minH

minL

secH

secL

↑

1

x

0

0

0

0

0

0

↑

0

1

不变

不变

不变

不变

不变

不变

↑

0

0

计时

计时

计时

计时

计时

计时

1.2 设计外部端口

按照设计要求,即需要 3 个输入端口和 24 个输出端口,其中输入端口包括

时钟信号(clk)、重置信号(reset)、暂停/恢复信号(stop),输出信号包括

显示小时高位和低位、分钟高位和低位、秒数高位和低位,每个位数需要 4 位

共 24 个端口。

2.设计内部实现逻辑

即按照自底向上的设计方法,划分为三个模块,第一个模块是信号产生器,

即产生 1 秒的脉冲信号,第二个模块是接受 1 秒的 clk 信号进行计数并输出正确

的小时、分钟、秒数的值,第三个模块是顶层文件,将信号输出至 6 个七段数码

管上。

- 3 -

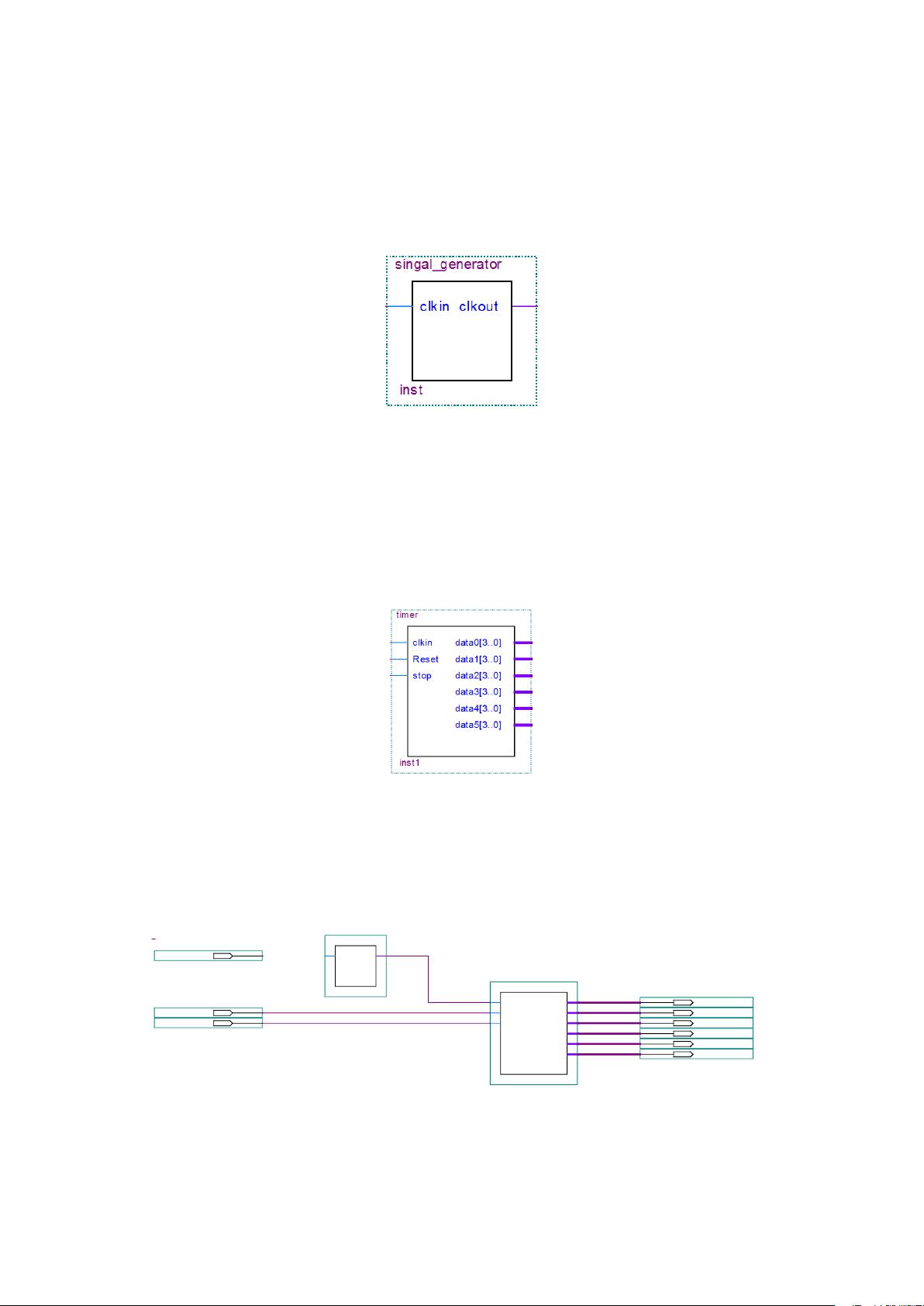

2.1 信号产生器“singal_generator.vhd”

此部分有一个输入端是 184.32KHZ 的时钟信号 clk,在内部进行分频,输出

一个周期是 1 秒的脉冲信号 clkout。其整体的外部模块图如下:

2.2 显示正确的小时、分钟、秒数的值“timer.vhd”

此部分的输入端是一个来自上一模块产生的时钟信号 clk,还有两个分别是

重置信号(reset)和暂停/恢复信号(stop)。输出是要显示的小时、分钟、秒

数的值,其整体的外部模块图如下:

2.3 顶层文件“clock.bdf”

此部分是顶层文件,将上面的两个模块连接起来,形成整体的时钟电路。其

逻辑电路图如下:

VCC

clk

INPUT

VCC

reset

INPUT

VCC

stop

INPUT

data0[3..0]

OUTPUT

data1[3..0]

OUTPUT

data2[3..0]

OUTPUT

data3[3..0]

OUTPUT

data4[3..0]

OUTPUT

data5[3..0]

OUTPUT

clkin

Reset

stop

data0[3..0]

data1[3..0]

data2[3..0]

data3[3..0]

data4[3..0]

data5[3..0]

timer

inst1

clkin

clkout

singal_generator

inst

剩余18页未读,继续阅读

伯特兰·罗卜

- 粉丝: 22

- 资源: 309

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- n.cpp

- jdk-8u411-windows-x64下载安装可用

- vgg模型-图像分类算法对水果识别-不含数据集图片-含逐行注释和说明文档.zip

- KMP算法(Knuth-Morris-Pratt算法

- vgg模型-python语言pytorch框架训练识别化妆品分类-不含数据集图片-含逐行注释和说明文档.zip

- KMP算法(Knuth-Morris-Pratt算法

- shufflenet模型-基于人工智能的卷积网络训练识别狗的表情-不含数据集图片-含逐行注释和说明文档.zip

- shufflenet模型-python语言pytorch框架训练识别张嘴闭嘴-不含数据集图片-含逐行注释和说明文档.zip

- resnet模型-基于人工智能的卷积网络训练识别面部表情识别-不含数据集图片-含逐行注释和说明文档

- resnet模型-python语言pytorch框架训练识别香蕉品质-不含数据集图片-含逐行注释和说明文档.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0