AWS_aes解密Demo使用说明1

需积分: 0 49 浏览量

更新于2022-08-08

收藏 232KB DOCX 举报

本文将详细介绍AWS_AES解密Demo的使用方法,以及其内部架构。这个Demo主要应用于ESP32通过QSPI串行通信接口与FPGA之间的数据交互,实现128bit加密数据的解密,还原成未加密的8bit传感器输入数据。

一、程序功能

1.1 概述

AWS_AES解密Demo的核心功能是接收ESP32通过QSPI接口发送的128bit加密数据,并在FPGA中进行AES解密,恢复出原始的8bit AD(模拟数字)数据。ESP32首先加载从AWS云端获取的128bit加密数据,这部分不在本说明文档内,需参考ESP32的相关文档。

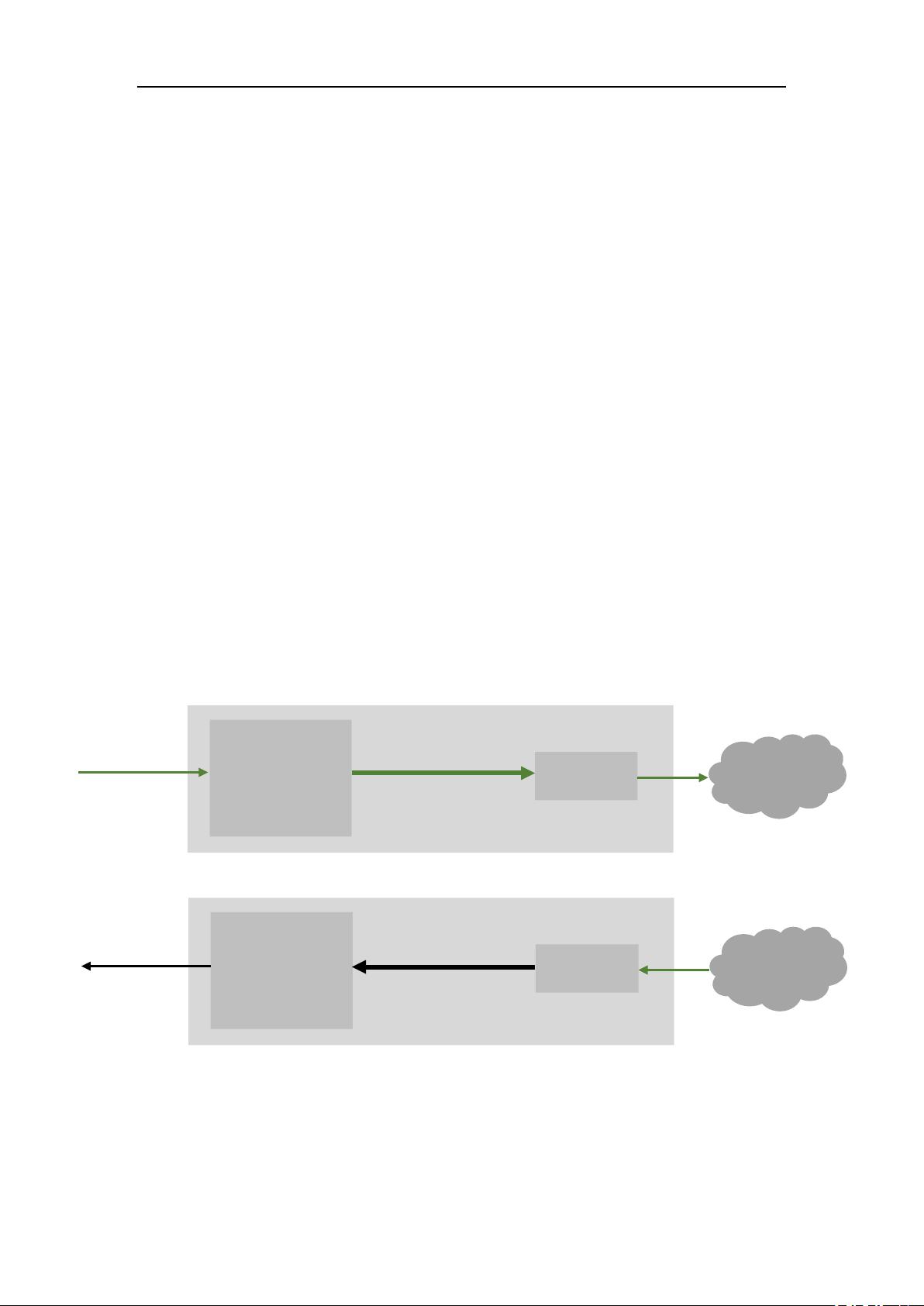

1.2 项目总体架构

系统由两部分组成:ESP32负责数据传输,FPGA负责解密。加密数据从AWS云发送到ESP32,再通过QSPI协议传输至FPGA,FPGA中的AWS_AES解密模块对数据进行解密,并通过IO口输出解密后的8bit AD数据。

二、解密程序架构

2.1 整体架构图

解密流程包括:AWS_AES_Inverse解密算法,秘钥加载,数据传输,解密,以及数据输出。秘钥可由4位拨码开关动态设置,解密数据存储在FPGA的RAM中。

2.2 引脚说明

- sclk:系统时钟输入,100MHz。

- rst_n:复位引脚,低电平有效。

- key_bus:4位秘钥输入端口,连接拨码开关。

- I_qspi_cs:QSPI片选信号。

- I_qspi_clk:QSPI时钟信号。

- qspi_data[3:0]:QSPI数据线,4根独立线。

- raw_data:8位解密后原始数据输入端口。

- DONE:解密完成使能信号。

- led_en:LED灯使能端口,用于测试。

三、内部架构说明

3.1 内部架构图

系统内部包含秘钥转换模块(key_128test)、AES解密模块(aes_inv_cipher_top)、RAM、数据压缩模块(data_compression)和LED控制模块(LED_control)。

3.2 架构详细说明

- 复位后,key_128test加载4位秘钥并扩展为128位AES秘钥,输出使能信号和秘钥。

- ESP32通过QSPI协议将数据写入RAM,ram_count组合数据为128bit解密数据。

- AES解密模块在秘钥加载完成后接收数据,解密后输出到data_compression模块。

- data_compression模块将128bit解密数据压缩为8bit原始数据,并输出到LED_control模块。

- LED_control模块根据解密数据判断是否超过阈值,控制LED灯的状态。

总结:

AWS_AES解密Demo是一个集成在FPGA中的解密系统,它利用AES解密算法,配合ESP32的QSPI通信,实现加密数据的安全传输与解密。该系统具有动态秘钥设置、数据实时解密和LED反馈等功能,适用于与AWS云平台结合的物联网安全应用场景。

柔粟

- 粉丝: 34

- 资源: 304

最新资源

- 地面无线电台(站)设置使用申请表.xlsx

- 档案材料归档移交目录表.docx

- 辅导员工作考核汇总表.docx

- 辅导员工作考核上报表.docx

- 辅导员工作考核登记表、辅导员工作量化考核表.docx

- 高中阶段(水平五)体育寒假作业建议表.docx

- 各年龄段骨密度参考值表.docx

- 工贸小微企业公示牌内容填写示范.docx

- 公寓管理服务中心研究生入住申请表.doc

- 管理工程系学生周五和周六晚不住校申请表.doc

- 国内公务接待清单.doc

- 技能学分项目和分值表.docx

- 教师学生听课记录.doc

- 快速随机Hough变换应用于多圆检测的研究与实现

- 普通高等学校毕业就业证明函.doc

- 省直住房货币化补贴提取申请表.xls