没有合适的资源?快使用搜索试试~ 我知道了~

PCI总线标准协议(中文版)1

需积分: 0 2 下载量 182 浏览量

2022-08-03

20:10:17

上传

评论

收藏 777KB PDF 举报

温馨提示

试读

14页

1.系统引线 2.地址和数据引线 3.接口控制信号 4.仲裁信号 5.错误报告信号 6.中断信号 7.高速缓存(Cache)支持信号

资源详情

资源评论

资源推荐

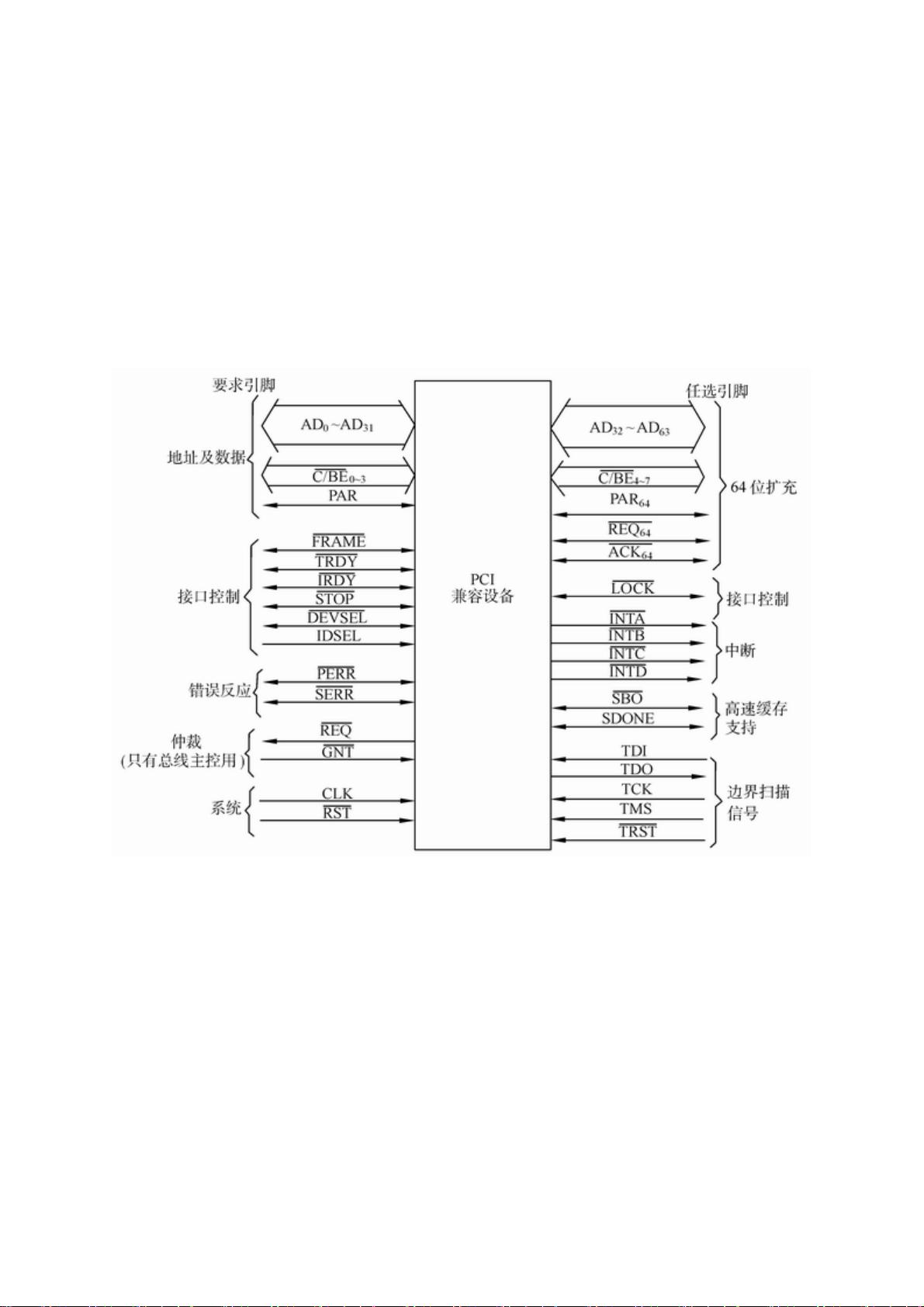

8.4.2 PCI

总线信号定义

在一个

PCI

应用系统中,如果某设备取得了总线控制权,就称其为

"

主设备

"

;而被主设备选中以进行

通信的设备称为

"

从设备

"

或

"

目标节点

''

。对于相应的接口信号线,通常分为必备的和可选的两大类,为了

进行数据处理、寻址、接口控制、仲裁等系统功能,

PCI

接口要求作为目标的设备至少需要

47

条引脚,

若作为主设备则需要

49

条引脚。下面对主设备与目标设备综合考虑,并按功能分组将这些信号表示在图

8

.

19

中。其中,必要的引脚在左边,任选的引脚在右边。

一.信号类型说明

图

8

.

19 PCI

引脚示图

为了叙述方便,将

PCI

信号按数传方向及驱动特性划分为五种类型,各种类型的规定 如下:

in

:输入信号。

out

:输出驱动信号。

t/s

:表示双向三态输入/输出驱动信号。

s

/

t

/

s

:持续三态(

Sustained Tri-State

),表示持续的并且低电平有效的三态信号。在某一时刻只

能属于一个主设备并被其驱动。这种信号从有效变为浮空(高阻状态)之前必须保证使其具有至少一个

时钟周期的高电平状态。另一主设备要想驱动它,至少要等到该信号的原有驱动者将其释放(变为三

态)一个时钟周期之后才能开始。同时,如果此信号处于持续的非驱动状态时,在有新的主设备驱动它

之前应采取上拉措施,并且该措施必须由中央资源提供。

o/d

:漏极开路(

Open Drain

)可作线或形势允许多个设备共同使用,

二.

PCI

总线信号定义

PCI

总线的信号线共有

100

根,下面按功能分组进行说明。

1/4 ページ微型计算机原理

2006-11-24http://www.hljnzy.net/kejian/weijijiekou/second/chapter8/c2-8-4-2.htm

1

.系统引线

CLK in

:时钟输入,为所有

PCI

上的接口传送提供时序。其最高频率可达

66MHz

,最低频率一般为

0

(

DC

),这一频率也称为

PCI

的工作频率。对于

PCI

的其他信号,除 、 、 、 之外,

其余信号都在

CLK

的上升沿有效(或采样)。

in

:复位,用来使

PCI

专用的特性寄存器和定时器相关的信号恢复规定的初始状况。每当复位

时,

PCI

的全部输出信号一般都应驱动到第三态。

2

.地址和数据引线

AD0

~

AD31 t/s

:地址、数据多路复用的输入/输出信号。在 有效时,是地址周期;在

和 同时有效时,是数据周期。一个

PCI

总线的传输中包含了一个地址信号周期和一个(或多

个)数据周期。

PCI

总线支持突发方式的读写功能。

地址周期为一个时钟周期,在该周期中

AD0

~

AD31

线上含有一个

32

位的物理地址。对于

I

/

O

操作,

它是一个字节地址;若是存储器操作和配置操作,则是双字地址。

在数据周期,

AD0

~

AD7

为最低字节,

AD24

~

AD31

为最高字节。当 有效时,表示写数据稳

定有效, 有效表示读数据稳定有效。

~

3 t/s

:总线命令和字节使能多路复用信号线。在地址周期内,这四条线上传输的是总线命

令;在数据周期内,传输的是字节使能信号,用来表示在整个数据期中,

AD0

~

AD31

上哪些字节为有

效数据。

3

.接口控制信号

s

/

t / s

:帧周期信号。由当前主设备驱动,表示一次访问的开始和持续时间。 无效

时,是传输的最后一个数据周期。

s / t / s

:主设备准备好信号。该信号有效表明发起本次传输的设备(主设备)能够完成一个

数据期。它要与 配合使用,当这两者同时有效时,才能进行完整的数据传输,否则即为等待周期。

在写周期,该信号有效时,表示有效的数据信号已在

AD0

~

AD31

中建立;在读周期,该信号有效时,表

示主设备已做好接收数据的准备。

s

/

t

/

s

:从设备准备好信号。该信号有效表示从设备已做好完成当前数据传输的准备工作,

此时可进行相应的数据传输。同样,该信号要与 配合使用,这两者同时有效数据才能进行完整传

输。在写周期内该信号有效表示从设备已做好了接收数据的准备。在读周期内,该信号有效表示有效数

据已被送入

AD0

~

AD31

中,同理, 和 的任何一个无效时都为等待周期。

s / t / s

:停止数据传送信号,该信号由从设备发出。当它有效时,表示从设备请 求主设备终

止当前的数据传送。

s / t / s

:锁定信号。是由

PCI

总线上发起数据传输的设备控制的,如果有几个不同的设备在

使用总线,但对 信号的控制权只属于一个主设备(由 信号标定)。当 信号有效时,表

示驱动它的设备所进行的操作可能需要多个传输才能完成,如果对某一设备具有可执行的存储器,那么

它必须能实现锁定,以便实现主设备对该存储器的完全独占性访问。对于支持 锁定的目标设备,必须能

提供一个互斥访问块,且该块不能小于

16

个字节。连接系统存储器的主桥路也必须使用 。

IDSEL in

:初始化设备选择信号。在参数配置读写传输期间,用作片选信号。

s

/

t

/

s

:设备选择信号,由从设备驱动,该信号有效时,表示驱动它的设备已成为当前访

问的从设备。它有效表明总线上的某一设备已被选中。

4

.仲裁信号

t

/

s

:总线请求信号。该信号一旦有效即表示驱动它的设备要求使用总线。它是一个点到点的

信号线,任何主设备都应有自己的 信号。

t /s

:总线允许信号。用来向申请占用总线的设备表示其请求已获批准。这也是一 个点到点的

2/4 ページ微型计算机原理

2006-11-24http://www.hljnzy.net/kejian/weijijiekou/second/chapter8/c2-8-4-2.htm

信号线,任何主设备都应有自己的 信号。

5

.错误报告信号

为了能使数据可靠、完整地传输,

PCI

局部总线标准要求所有挂于其上的设备都应具有错误报告线。

s / t / s

:数据奇偶校验错误报告信号,但是该信号不报告特殊周期中的数据奇偶 错。一个设

备只有在响应设备选择信号 和完成数据期之后,才能报告一个 。 对于每个数据接收设备,

如果发现数据有错误,就应在数据收到后的两个时钟周期将 激活。该信号的持续时间与数据期的

多少有关,如果是一个数据期,则最小持续时间为一 个时钟周期;若是一连串的数据期并且每个数据期

都有错,那么 的持续时间将多于一个时钟周期。由于该信号是持续的三态信号,所以该信号在释放

前必须先驱动为高电平。另外,对数据奇偶错的报告不能丢失也不能推迟。

o

/

d

:系统错误报告信号。该信号用于报告地址奇偶错,特殊命令序列中的数据奇偶错,以

及其他可能引起灾难性后果的系统错误。 是漏极开路信号,由返遣错误的单元驱动,在一个

PCI

时钟内有效。 信号的发出和时钟同步,因而满足总线上所有其他信号的建立时间和保持时间的要

求。

6

.中断信号

中断在

PCI

总线上是可选用的,低电平有效,用漏极开路方式驱动。同时,此类信号的建立和撤销是

与时钟不同步的。

PCI

为每一个单功能设备定义一根中断线。对于多功能设备或连接器,最多可有

4

条中

断线。对于单功能设备,只能使用 ,其余

3

条中断线无意义。

PCI

局部总线有四条中断线,定义如下:

o

/

d

:中断

A

,用于请求一次中断。

o

/

d

:中断

B

,用于请求一次中断并只在多功能设备上有意义。

o

/

d

:中断

C

,功能同中断

B

。

o

/

d

:中断

D

,功能同中断

B

。

多功能设备上的任何一种功能都能连到任何一条中断线上。中断寄存器决定该功能用哪一条中断线

去请求中断。如果一个设备只用一条中断线,则这条中断线就称为

INTA

,如果该设备用了两条中断线,

那么它们就称为

INTA

和

INTB

,依此类推。对于多功能设备,可以是所有功能用一条中断线,也可以是每

种功能有自己的一条中断线,还可以是上两种情况的综合,一个单功能设备不能用一条以上的中断线去

申请中断。

系统供应商在对

PCI

连接器的各个中断信号和中断控制器进行连接时,其方法是随意的,可以是线

或方式、程控电子开关方式,或者是二者的组合,这就是说,设备驱动程序对于中断共享事先无法作出

任何假定,即它必须能够给任何逻辑设备提供中断。

7

.高速缓存(

Cache

)支持信号

为了使具有可缓存功能的

PCI

存储器能够和贯穿写(

Write-Through

)或回写(

Write- Back

)的

Cache

相配合工作,可缓存的

PCI

存储器应该能实现两条高速缓存支持信号作为 输入。如果可缓存的存

储器位于

PCI

总线上,那么连接回写式

Cache

和

PCI

的桥路必须要利用两条引脚,且作为输出,而连接贯

穿写式

Cache

的桥只需要实现一个信号。上述两个信号的定义如下:

in

/

out

:双向试探返回信号(

Snoop Backoff

)。当其有效时,说明对某修改行的一次命中,

所访问的数据为无效数据。当 无效而

SDONE

有效时,说明

PCI

发起方正在访问存储器的有效行并可

进行高速缓存的操作。

SDONE in

/

out

:监听完成信号(

Snoop Done

),表明对处理器

Cache

对主存的监听状态。当其

无效时,说明监听仍在进行,否则表示监听已经完成。

8

.

64

位总线扩展信号

如果要进行

64

位扩展,以下信号都要使用。

3/4 ページ微型计算机原理

2006-11-24http://www.hljnzy.net/kejian/weijijiekou/second/chapter8/c2-8-4-2.htm

剩余13页未读,继续阅读

chenbtravel

- 粉丝: 16

- 资源: 296

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0