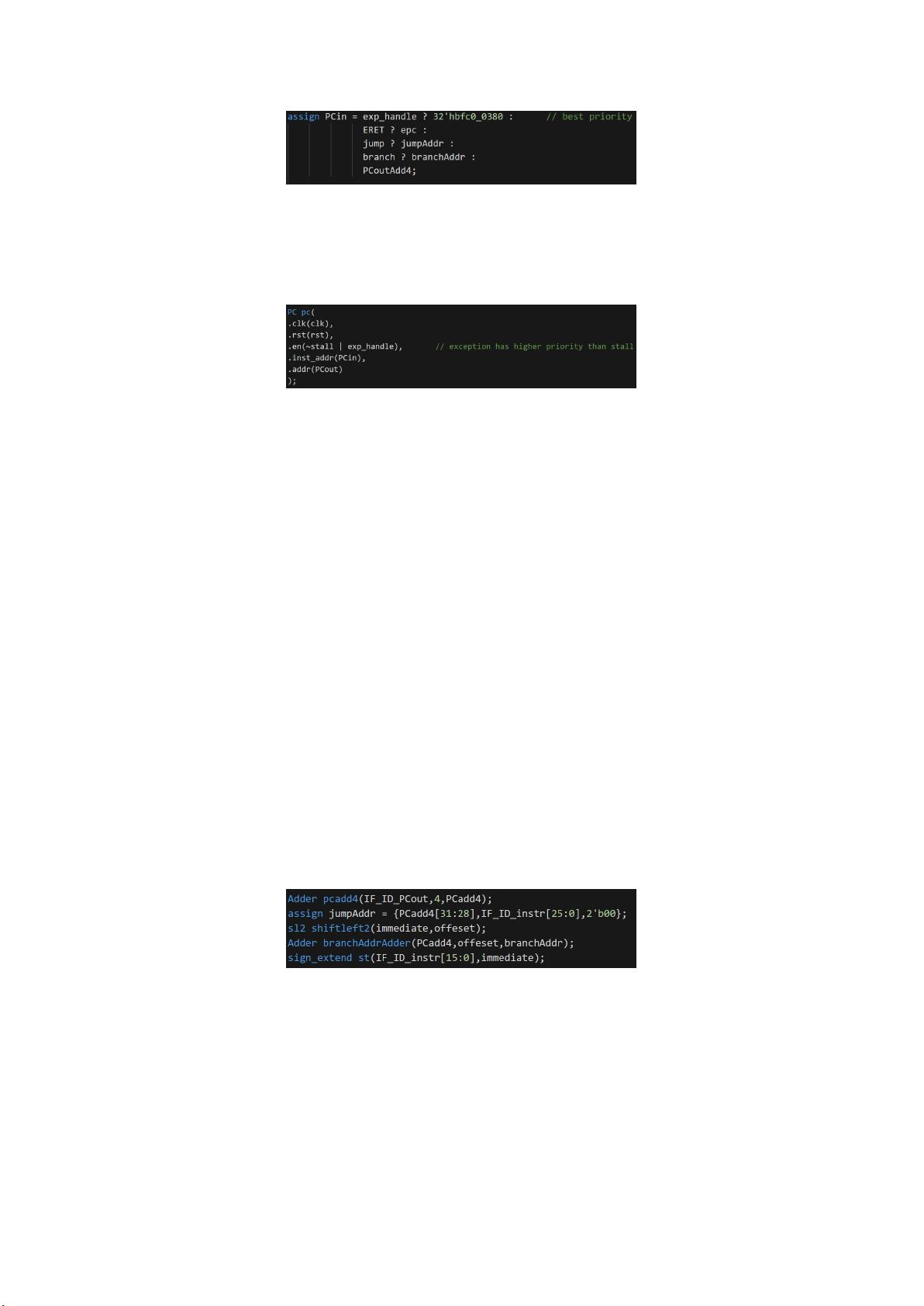

这篇硬件综合设计报告详细介绍了基于MIPS架构的SoC(System on Chip)设计与性能优化。设计团队在原有的五级流水线CPU基础上进行了扩展,增加了指令集和异常处理功能,以此提升系统的功能性和效率。 CPU的设计由最初的10条指令扩展到了57条,覆盖了MIPS I指令集的非浮点指令,包括算术运算、逻辑运算、移位、分支、数据移动、自陷、访存和特权指令等。这一扩展显著增强了CPU的处理能力,使其能够应对更复杂的计算任务。 异常处理模块的实现是设计的一个关键部分,它允许CPU在遇到错误或异常情况时采取适当的措施,如中断或跳转到错误处理程序,从而确保系统的稳定性和安全性。 在实现过程中,设计者遵循了五级流水线结构,即取指(IF)、译码(DE)、执行(EX)、内存访问(MEM)和写回(WB)阶段。针对不同类型的指令,设计者分析了它们在数据通路中的路径,并相应地修改了控制器和数据通路。每个指令类型的实现都经过了仿真和调试,以确保正确性。 为了优化性能,设计团队采用了暂停流水线的方式来处理多周期的乘法和除法运算,避免了因关键路径过长而影响主频的问题。此外,他们还引入了专门的乘除法控制单元来处理这些复杂运算。 在数据通路方面,Hilo寄存器被放在了执行阶段(EX),虽然在该阶段可以读取,但实际写入操作发生在内存访问阶段(MEM)。分支跳转则在内存阶段(MEM)实现,以处理延迟槽的执行。如果需要分支,延迟槽的下一条指令会被清除,这是通过假定分支不跳转的策略来实现的。 报告提到了团队成员的分工,代韵涛主要负责分支、数据移位、特权和陷阱指令的设计,以及乘法、除法单元和Hilo寄存器的实现,他还参与了数据冒险模块、数据通路的修改和SRAM接口的功能测试。蒙家鑫则专注于算术、逻辑、移位和访存指令模块,完成了57条指令的功能仿真测试,同时参与了上板操作和异常处理模块设计。 这个MIPS SOC设计展示了对计算机组成原理的深入理解和实践应用,通过扩展指令集和添加异常处理,提高了CPU的灵活性和鲁棒性,同时也体现了团队成员在系统设计、性能优化和故障处理方面的技能。

剩余26页未读,继续阅读

- 粉丝: 31

- 资源: 333

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论0