lab3实验报告1

需积分: 0 185 浏览量

更新于2022-08-03

收藏 1.22MB PDF 举报

【流水线改动】

在RISC-V处理器的流水线设计中,为了支持多周期乘除法器,需要对流水线进行相应的调整。主要改动包括:

1. **支持乘多周期除法器**:在alu和execute阶段增加了时钟和握手信号。当`execute_data_ok`信号为低时,表明execute阶段的计算还未完成,需要阻塞execute之前的所有流水段,同时,memory和writeback段可以继续流动并插入气泡。一旦`execute_data_ok`变高,流水线恢复正常。对于乘除法操作可能存在的数据延迟问题,如果execute需要memory阶段转发的数据,但memory阶段正在进行访存操作,可能导致数据不正确。这时,通过检测hazardOut.clear信号为1,拉高multiplier和divider的reset信号,等待memory获取正确数据后再开始计算,设置state_nxt为DOING,启动新的计算周期。

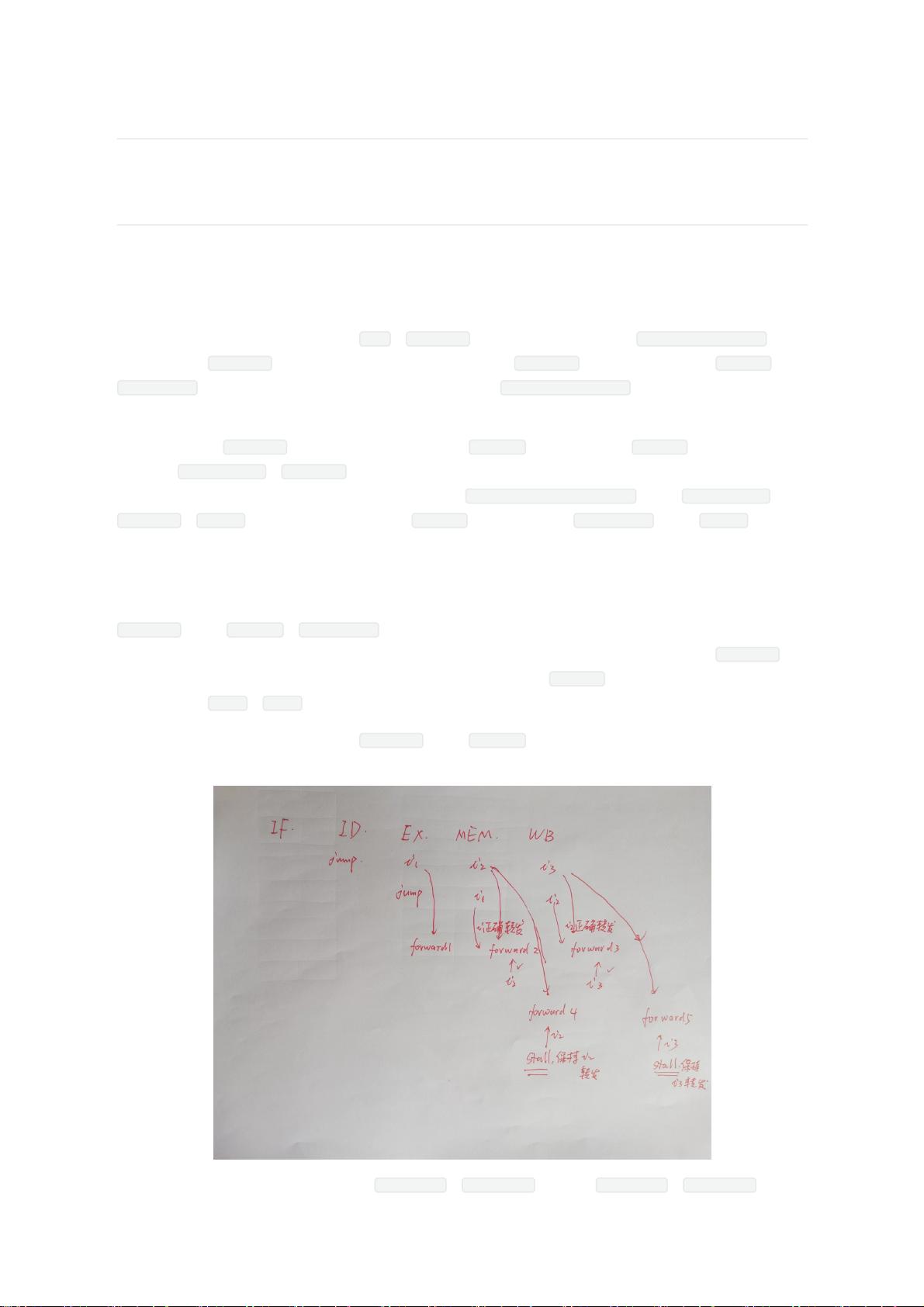

2. **转发器问题**:当execute被阻塞时,memory和writeback段仍可流动,这可能导致转发器数据覆盖。为解决此问题,引入了两个备份转发器。通常情况下,forward4和forward5与forward2和forward3同步转发数据。在execute阻塞而memory不阻塞的情况下,阻塞forward4和forward5,使用1~3号转发器保存数据,防止数据覆盖。当memory阻塞时,forward5保持i3的转发数据,forward3则接收i2的转发数据,确保数据源的完整性。

【缓存设计】

1. **状态机**:缓存的状态机包括IDLE(空闲)、COMPARE(标志比较)、FETCH(取数)、WRITEBACK(写回)和UNCACHED(不经过缓存)。在hit状态下存在一个周期的延迟。状态之间的转换遵循特定规则,确保缓存操作的正确进行。

2. **LRU替换策略**:采用LRU(Least Recently Used)策略进行缓存替换。每个cache set维护一个数组,记录各块的访问情况。数组中的值表示距离上次访问的时间,数值越小表示访问越近,越大表示访问越远。在COMPARE状态且hit条件满足时,更新used_line数组,保持最近访问的块的used_line值为0,其他块的值根据访问顺序递增。这样,当需要替换时,可以通过查找数组中的最大值确定替换块。

【测试结果】

1. **Verilator测试**:在Verilator环境下,针对不同的测试程序(如paint、coremark、dhrystone和stream),得到了相应的性能指标,如每秒迭代次数、标记数和最佳速率等。

2. **上板串口软件测试**:在实际硬件板上进行测试,同样对多个程序进行了测试,观察到的运行时间与Verilator测试有所不同,体现了硬件环境与仿真环境的差异。

本实验报告详细介绍了在RISC-V处理器流水线中支持多周期乘除法器所需的改动,以及为解决转发器和缓存问题所采用的策略。此外,还展示了通过Verilator和实际硬件板的测试结果,验证了这些改动的有效性和性能表现。

高中化学孙环宇

- 粉丝: 15

- 资源: 338

最新资源

- 毕设和企业适用springboot企业资源规划类及在线学习平台源码+论文+视频.zip

- 毕设和企业适用springboot企业资源规划类及智慧安防系统源码+论文+视频.zip

- 毕设和企业适用springboot区块链技术类及企业云管理平台源码+论文+视频.zip

- 毕设和企业适用springboot企业资源规划类及智能医疗监测系统源码+论文+视频.zip

- 毕设和企业适用springboot企业资源规划类及智能城市数据管理平台源码+论文+视频.zip

- 毕设和企业适用springboot企业资源规划类及智慧社区管理平台源码+论文+视频.zip

- 毕设和企业适用springboot区块链技术类及数字营销平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及城市智能管理系统源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及城市智能运营平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及广告效果评估平台源码+论文+视频.zip

- 毕设和企业适用springboot区块链技术类及网络营销平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及跨境电商管理平台源码+论文+视频.zip

- 毕设和企业适用springboot汽车电商类及教学资源共享平台源码+论文+视频.zip

- 毕设和企业适用springboot区块链技术类及云端储物管理系统源码+论文+视频.zip

- 毕设和企业适用springboot区块链技术类及在线教育管理系统源码+论文+视频.zip

- 毕设和企业适用springboot区块链技术类及智能会议管理平台源码+论文+视频.zip