CPU设计文档2

需积分: 0 143 浏览量

更新于2022-08-08

收藏 180KB DOCX 举报

在本文档中,我们讨论了单周期CPU设计的几个关键组成部分,包括IFU(指令 fetch unit)、GRF(通用寄存器文件)、ALU(算术逻辑单元)、DM(数据存储器)、EXT(立即数扩展)和Controller。这些组件协同工作,实现了CPU的基本功能。

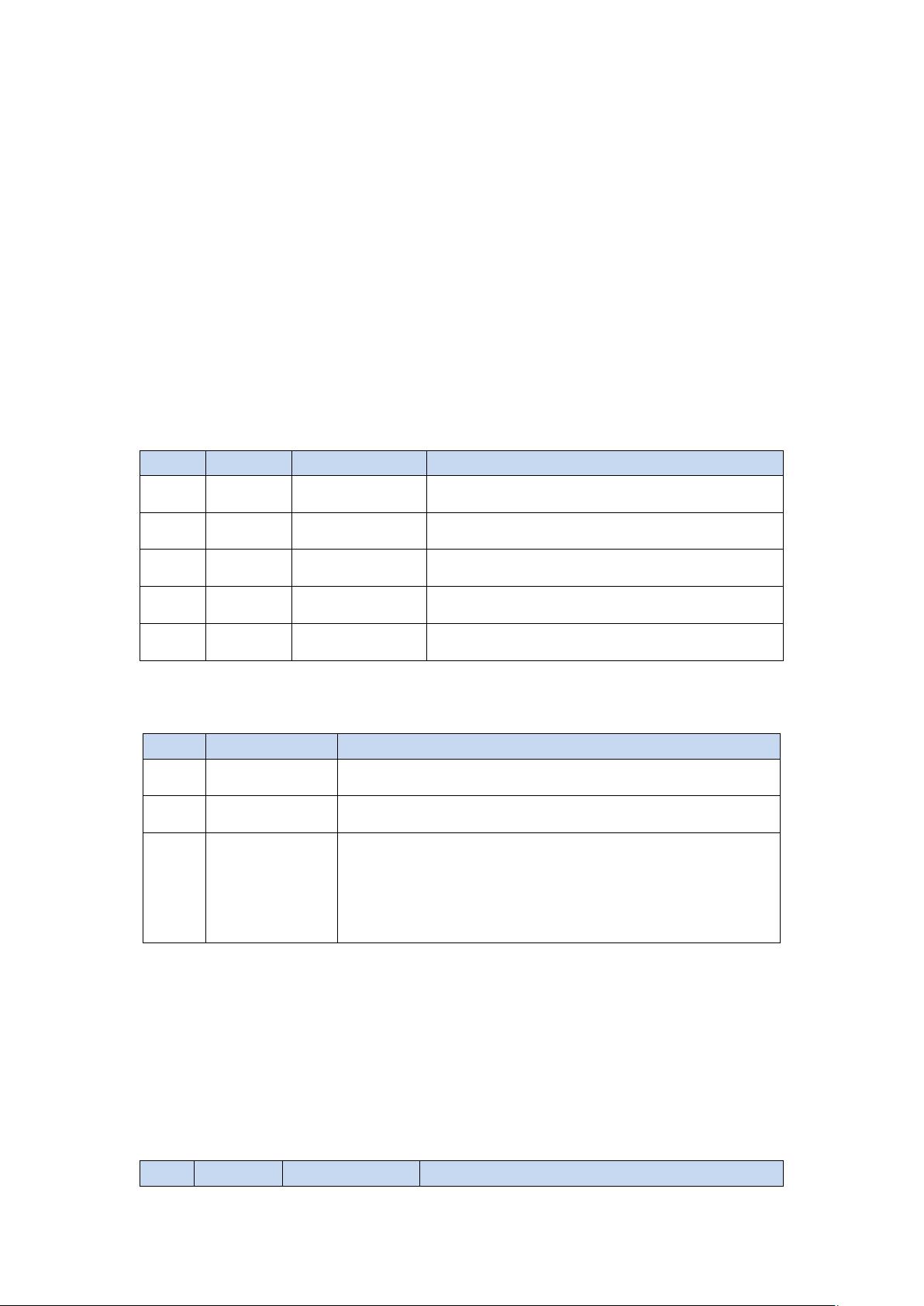

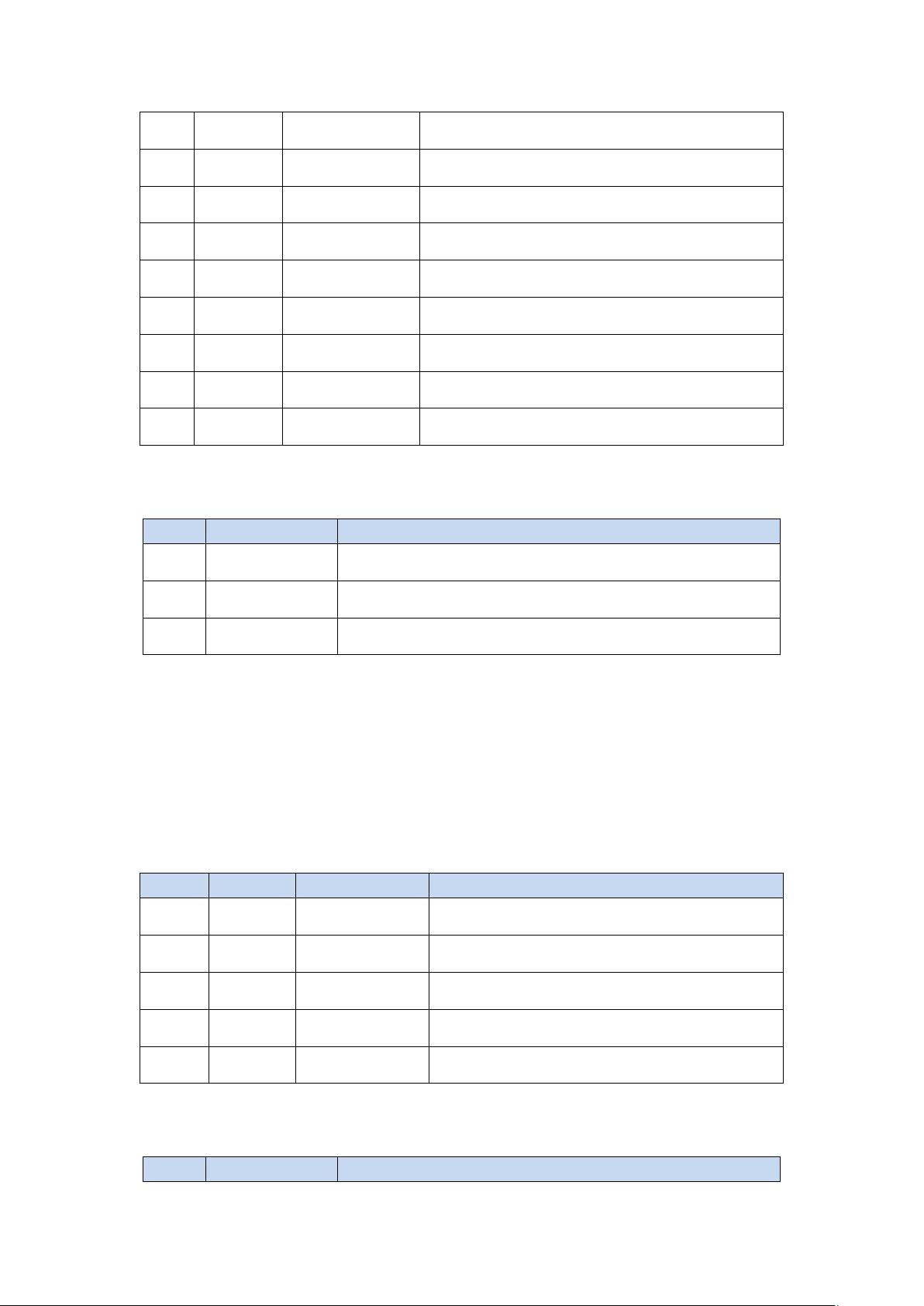

1. IFU(指令 fetch unit):

- IFU负责从内存中取出指令,并对跳转进行处理。

- 它由PC(程序计数器)和IM(指令存储器)组成,PC提供下一条要执行的指令地址。

- IFU有三个主要端口:ifJI、ifBcom和reset,分别用于判断当前指令是否为J型指令、是否满足跳转条件以及接收复位信号。

- 在复位时,PC被设置为0x00000000。若当前指令满足跳转条件或为J型指令,PC会更新。

2. GRF(通用寄存器文件):

- GRF包含32个通用寄存器,用于存储数据。

- 它有三个输入端口A1、A2和A3,用于指定要读写的寄存器,以及一个写使能信号WE。

- GRF的功能包括复位时清零所有寄存器,读取A1和A2指定寄存器的数据,以及在WE有效且时钟上升沿时写入A3指定寄存器的数据。

3. ALU(算术逻辑单元):

- ALU执行基本的算术和逻辑运算,如加、减、与、或,且不检查溢出。

- 它有两个输入端口AI和BI,一个2位选择信号sel,以及输出CO和notzero。

- 根据sel信号,ALU可以选择不同的操作,如加法、减法、按位与、按位或,并能判断运算结果是否为零。

4. DM(数据存储器):

- DM用于存储和检索数据,具有地址、数据输入、写使能信号WE和时钟输入。

- 当WE有效且时钟上升沿时,DM会写入数据;在地址指定的位置读取数据并输出。

5. EXT(立即数扩展):

- EXT将16位立即数扩展为32位,根据sel信号选择不同扩展方式,如无符号扩展、有符号扩展等。

- 输出是扩展后的32位数。

6. Controller:

- Controller根据指令的opcode和func字段解析指令,生成控制信号以驱动其他部件。

- 它提供了诸如regSlt(选择GRF的B来源)、aluOp(ALU操作选择)等输出信号,以及对其他组件如DM和EXT的控制。

通过以上组件的交互,CPU能够完成指令的解码、数据的读写、算术逻辑运算以及跳转控制。每个组件都有明确的功能定义和输入输出信号,共同构建了一个简单的单周期CPU模型。在实际设计中,还需要考虑更多的细节,如错误处理、中断管理等,以实现更复杂的系统。

亚赛大人

- 粉丝: 33

- 资源: 332

最新资源

- 音乐网站(JSP+SERVLET).rar

- 抢购软件:快速复制信息

- oracle错误代码和信息速查手册chm版最新版本

- MATLAB【逆变器二次调频模型】 微电网分布式电源逆变器DROOP控制二次调频模型,加入二次控制实现二次调频控制,及二次调压控制,程序可实现上图功能,工况有所改变 需要matlab2021A版

- 基于python的网页自动化工具项目全套技术资料100%好用.zip

- Oracle数据库命令速查手册doc版最新版本

- 程序名称:转向设计计算程序 开发平台:基于matlab平台 计算内容:阿克曼转角,转弯半径,转向阻力矩,回正力矩,转向主参数,转向传动比,力矩波动,转向梯形,EPS匹配,HPS匹配,齿轮齿条传动比,循

- 基于二阶自抗扰ADRC的轨迹跟踪控制,对车辆的不确定性和外界干扰具有一定抗干扰性,基于carsim和simulink仿真 跟踪轨迹为双移线,效果良好,有对应复现资料,是学习自抗扰技术快速入门很好的资料

- TianleSoftwareOracle学习手册中文pdf格式最新版本

- MATLAB代码:基于分布式ADMM算法的考虑碳排放交易的电力系统优化调度研究 关键词:分布式调度 ADMM算法 交替方向乘子法 碳排放 最优潮流 仿真平台:MATLAB+CPLEX GUROBI

- Oracle安装配置使用WORD文档doc格式最新版本

- 西门子840D HMI ADVANCED FOR PC 也可用于810D,840DSL中文版 1、软件可安装到台式机或笔记本上,可以连接到机床的NCU进行NC与PLC的数据备份与恢复,备份和恢复的数

- OraclePLSQL简单安装指南WORD文档doc格式最新版本

- 网页数据采集软件项目全套技术资料100%好用.zip

- Oracle高级SQL培训与讲解WORD文档doc格式最新版本

- 超智能体写的人工智能深度学习pdf