没有合适的资源?快使用搜索试试~ 我知道了~

一、实现要求 二、插值滤波原理 三、插值滤波实现 四、FPGA 实现流程 五、模块分析

资源详情

资源评论

资源推荐

插值 FPGA 实现分析文档

一、实现要求

功能要求:

对信号 2、5、10、20、25、50、100 倍插值;滤波器系数从外部输入,

保存在 RAM 中。

外部输入参数:

312.5M 时钟(插值模块时钟)

100M 时钟(系数存储时钟)

待插值信号(10 bit,10 位 ADC 输出,前级模块发送)

FIFO 满信号(高电平有效,前级模块发送)

输入有效信号(高电平有效,前级模块发送)

复位信号(高电平有效,PC 机发送,地址:0x88B4)

使能信号(高电平有效,PC 机发送,地址:0x88B8)

清零信号(高电平有效,PC 机发送,)

插值倍数(4bit,0 到 6 依次对应 2、5、10、20、25、50、100 倍插值,,

PC 机发送,地址:0x88A4)

滤波器系数(17 bit,PC 机发送,高位地址:0x88B0,低 16 位地址:

0x88AC)

地址(9 bit,PC 机发送,地址:0x88A8)

输入时序:

先产生一个正脉冲复位,复位后同时发送地址和滤波系数,发送滤波系数

和地址,等每个地址和滤波系数稳定后,发送一个写使能信号脉冲。在所有的

地址和系数发送完成后,将写使能信号变为低电平。发送插值倍数,等清零信

号无效后,且在 FIFO 满信号有效后,将带插值的信号输入,同时每发送一个

数据需要发送一个输入有效脉冲。

二、插值滤波原理

信号的插值是指增加抽样率以增加数据的过程。将抽样频率为的信号

进行

L

倍插值,即抽样频率变为,最简单直接的方式是在

每两个

点之间插入 个

0

,如图

2-1

所示。记补零后的信号为,则

图

2-1 3

倍插值前后图像

其它

从频域分析插值:

对做傅里叶变化有如下关系式

∞

∞

∞

∞

∞

∞

则抽取前后的频域关系为

由抽取前后的频域关系可知,

是将

频带压缩了

L

倍。

和

都是周期的,且

周期为,由于

是将

频带压缩

了

L

倍,则

的周期是,则在一个周期内产生了 个镜像。

插值后,

每个周期出现了

L

个周期,其中 个周期为

的

映像,需要去除。去除的方法是在

之后加一个低通滤波器,以滤除由于

频带压缩产生的镜像。低通滤波器的形式如下:

其它

低通滤波器的截止频率是。在频域上看,滤波器的主要作用是去除

中多余的 个映像。

从时域上分析:

图

2-2

插值后的滤波

如图

2-2

所示,在经过

L

倍

0

插值后,在经过低通滤波器。这时滤波

器在时域上表现为对做平滑处理。

输出的时域表达式为

)(nx

)(n

)(nh

)(ny

L

ℎ

ℎ

ℎ

(

)

或

ℎ

(

)

∞

∞

三、插值滤波实现

若将数据插值后再滤波,即

ℎ

ℎ

,由于插

值后

有很多零值,而零值与

ℎ

相乘为零,这实际上是不需要的;在实现

时,乘零运算也会占用乘法器的资源,由于乘法器的资源有限,所以要避免不

必要的乘零运算。

对

2-2

式的表达形式,以三倍插值为例,滤波器系数个数为

12

,则有

ℎ

∞

∞

ℎ

ℎ

ℎ

ℎ

ℎ

同理可得

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

ℎ

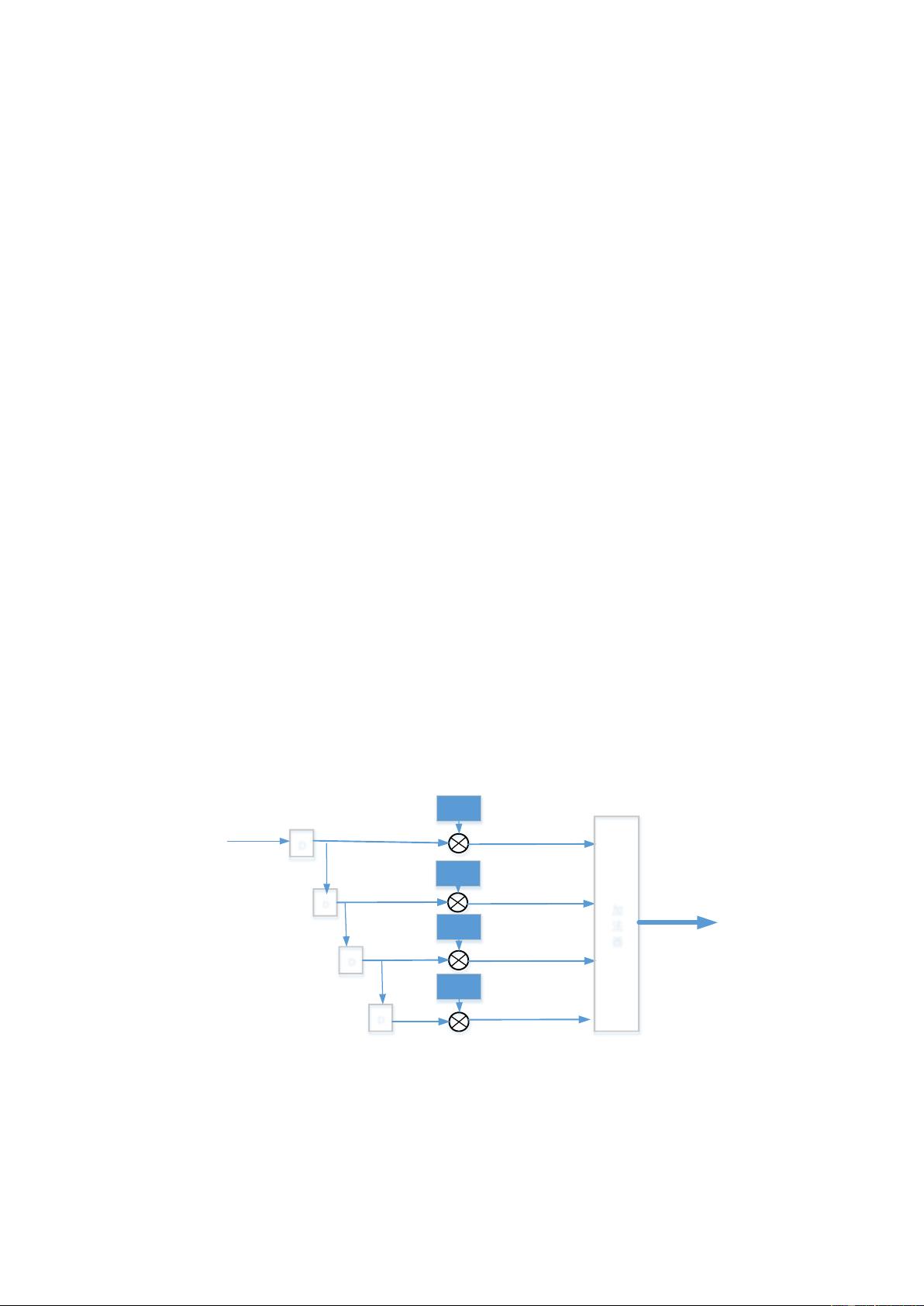

根据以上的计算过程,可以发现,每输入一个数据

,要产生 L 个输出

、

、

、、

。如图 3-1 所示,根据式 2-2

的表达式,可以画出如下的框图完成对插值的滤波实现。

RAM1

D

RAM2

D

RAM3

D

RAM4

D

加

法

器

图 3-1 实现框图

RAM1

中依次存储的是

ℎ

、ℎ

、ℎ

ℎ

,

RAM2

中依次存储的是

ℎ

、ℎ

、ℎ

ℎ

,直到存完所有的

RAM

。

四、FPGA 实现流程

剩余12页未读,继续阅读

亚赛大人

- 粉丝: 26

- 资源: 333

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0