Altera FPGA 开发入门1

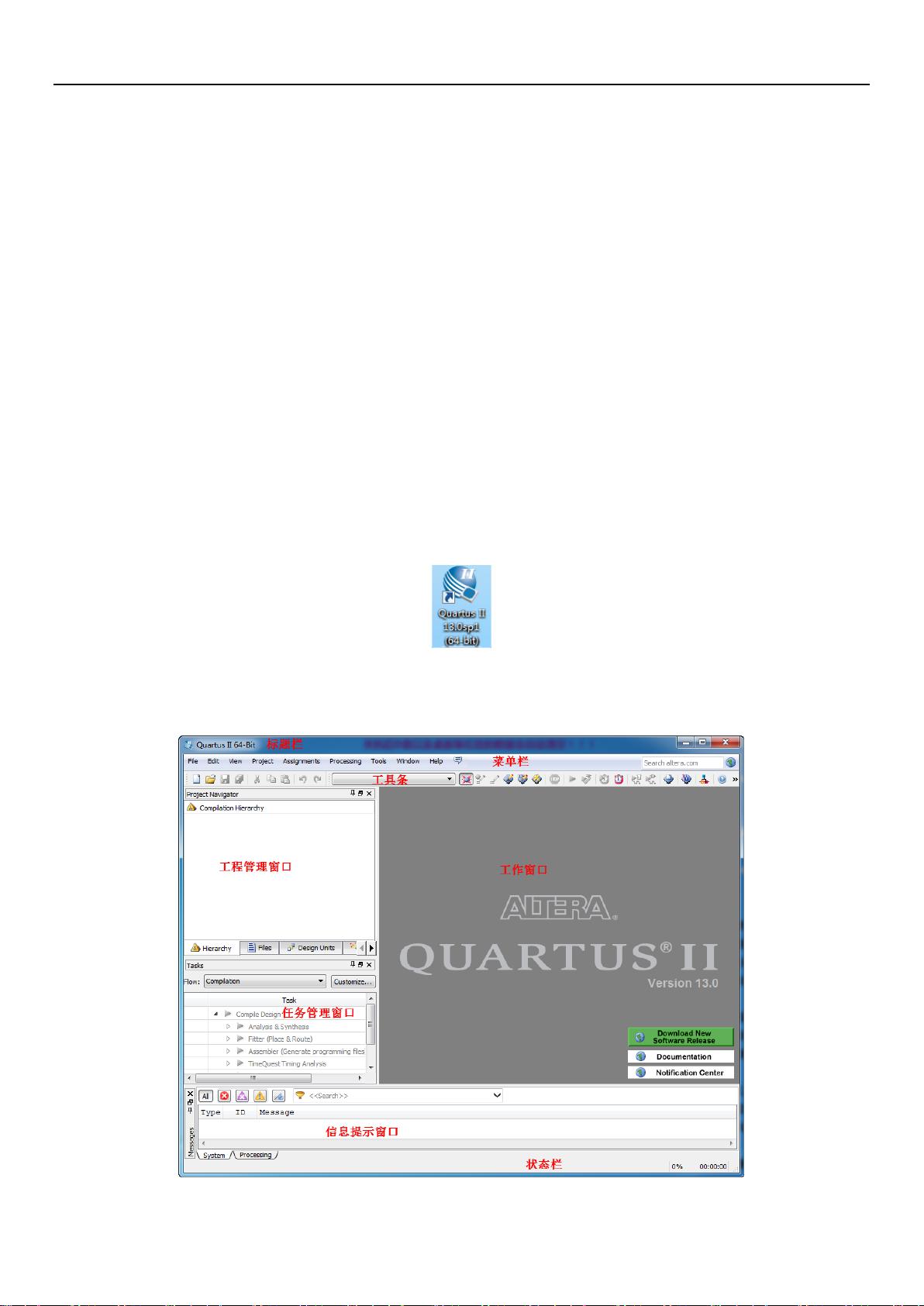

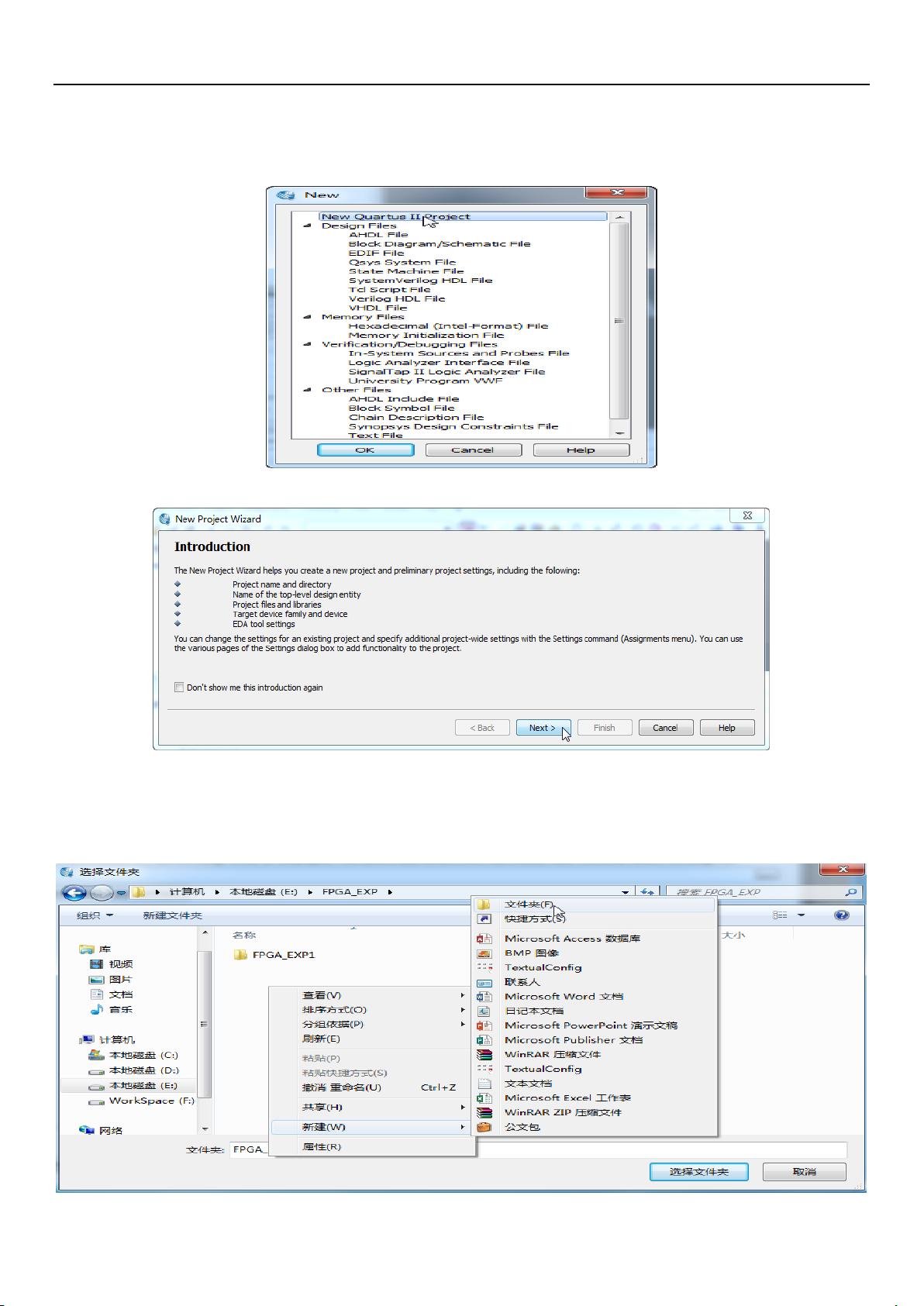

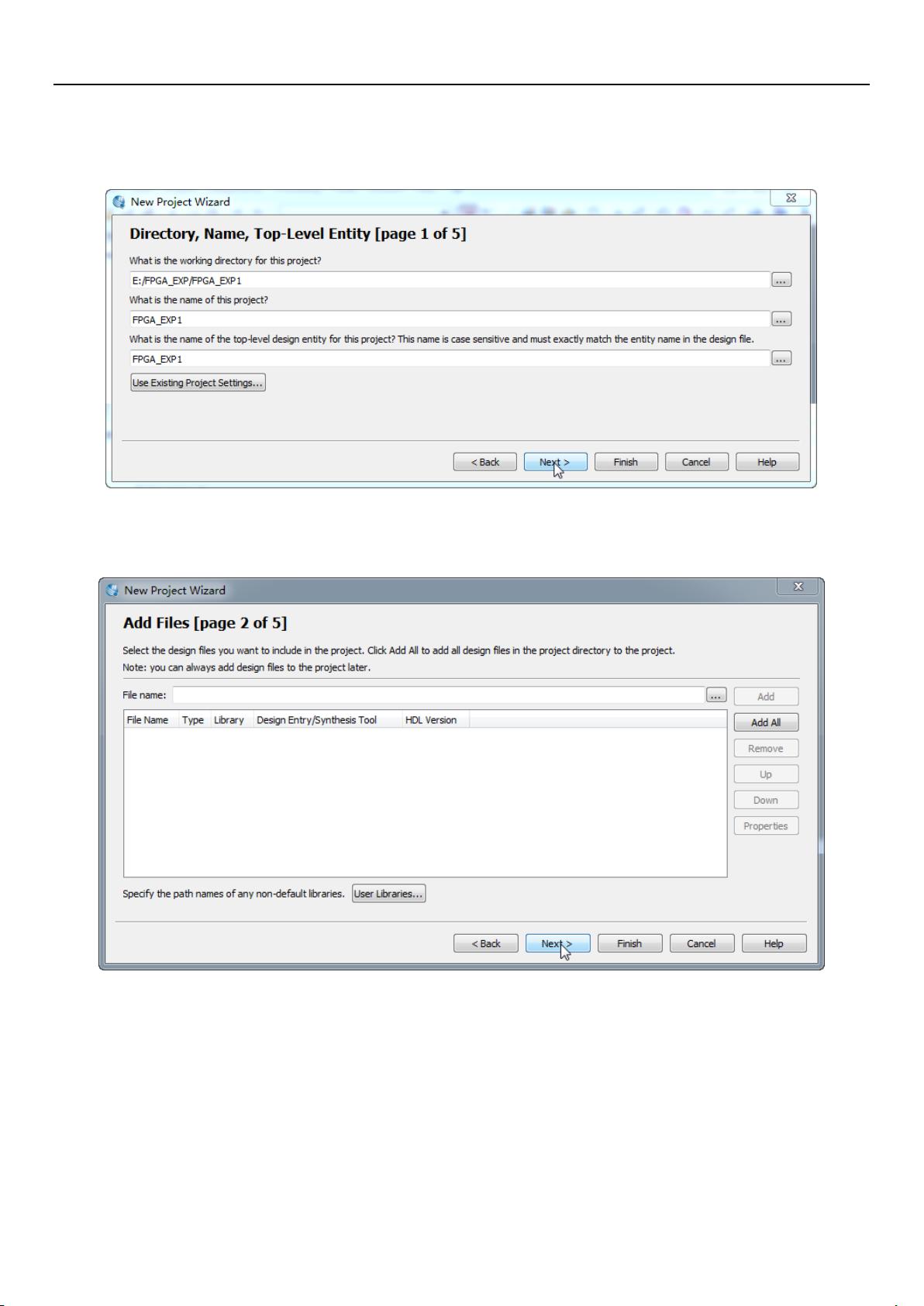

本文将介绍Altera FPGA开发入门的基础知识,包括如何使用Quartus II 13.0 SP1软件创建FPGA设计工程,以及设置相关的硬件和仿真工具。Altera FPGA是一种可编程逻辑器件,广泛应用于电子系统设计中,提供高度灵活和高效的解决方案。 启动Quartus II 13.0 SP1软件,这是Altera公司提供的FPGA综合和开发平台。该软件界面包括常见的Windows应用程序元素,如菜单栏、工具条和状态栏,还有特定的工程管理和任务管理功能。 创建FPGA设计工程的步骤如下: 1. 通过"File"菜单选择"New...",在弹出的窗口中选择"New Quartus II Project"。 2. 在"New Project Wizard"的第一步,选择工程的工作目录。在本例中,创建名为"FPGA_EXP"的文件夹,并在其下创建子文件夹"FPGA_EXP1"作为工程存储位置,项目名设为"FPGA_EXP1"。 3. 第二步,添加设计文件。如果没有预先准备的设计文件,可以直接跳过此步。 4. 第三步,配置设备家族和设备设置。这里选择了Cyclone V系列,具体型号为"Cyclone V E Extended Features",并进一步设置了封装类型、引脚数量和速度等级。 5. 第四步,设置EDA工具。对于仿真,选择工具类型为"Simulation",工具名为"Modelsim",格式为VHDL。 在完成工程创建后,下一步是添加设计文件和代码。设计文件通常包含用VHDL或Verilog编写的硬件描述语言(HDL)代码,这些代码定义了FPGA内部的逻辑功能。在Quartus II中,可以通过"File"菜单的"Add/Remove Files in Project"选项将这些文件添加到工程中。 接下来是分析和综合(Analysis & Synthesis)阶段,这是FPGA设计的关键步骤。在这一阶段,Quartus II会读取设计文件,进行语法检查和逻辑优化,将HDL代码转换成门级网表,这个过程称为逻辑综合。综合后的结果将显示在工程的逻辑资源占用情况,如逻辑单元、触发器、I/O口等。 为工程添加仿真文件和代码。仿真用于验证设计的功能是否正确,Modelsim是常用的FPGA仿真工具。用户需要编写测试激励(Testbench)文件,用以模拟设计的输入和预期输出,然后在Modelsim中运行仿真,观察和分析结果。 通过这个实验,学习者将了解Altera FPGA开发的基本流程,包括设计环境的设置、工程创建、设计文件的添加、逻辑综合以及仿真验证。这些知识是进行更复杂FPGA设计的基础,对于电子系统设计和嵌入式系统的开发至关重要。在实践中,不断积累经验,解决遇到的问题,是提高FPGA设计能力的有效途径。

剩余18页未读,继续阅读

- 粉丝: 23

- 资源: 319

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 结合 Swin Transformer 的小物体检测算法用于茶芽检测.zip

- 彩蝶ARP防火墙,很好用!

- 简单易用的模拟器 YOLOv5 鸟瞰视角物体检测.zip

- 高恪AC固件斐讯K2通用包

- 简单插入一些源码,实现的人脸识别项目 供学习参考 具体使用到yolov5人脸检测、arcface人脸识别 .zip

- windows 2003密钥

- 社交距离检测,一个使用 yolo 物体检测的深度学习计算机视觉项目.zip

- 传奇微端架设详细说明,快来下载啊

- 音频放大器的设计与制作-(模拟电子技术综合设计)项目报告

- 目标检测yolov5 v6.0版,pytorch实现,标注,增强,自定义训练数据集全流程.zip

信息提交成功

信息提交成功