没有合适的资源?快使用搜索试试~ 我知道了~

02开发流程(中)1

需积分: 0 0 下载量 176 浏览量

2022-08-03

19:29:45

上传

评论

收藏 456KB PDF 举报

温馨提示

试读

8页

数字逻辑与部件设计 实验部分-02.开发流程(中)Convert code to circuit.数字逻辑与部件设计 实验部分-02.开发流程(中)将已有的代码

资源详情

资源评论

资源推荐

数字逻辑与部件设计 实验部分-02.开发流程

(中)

Convert code to circuit.

数字逻辑与部件设计 实验部分-02.开发流程(中)

将已有的代码生成bit文件

Step 0:在Vivado安装目录中添加实验板信息

Step 1:新建项目

Step 2:运行tcl脚本添加源文件

Step 3:开启多线程(optional)

Step 4:生成bitstream

Step 5:上板

硬件描述语言简介

硬件描述语言与实际硬件

硬件描述语言与C语言

SystemVerilog基础语法:二进制位

变量声明

常量

接入电路系统:assign语句

SystemVerilog基础语法:模块与元件

模块的定义

元件例化:模块接入电路系统

更加简便的设计

黑盒

SystemVerilog基础语法:运算符

将已有的代码生成bit文件

我们已经学会了如何将bit文件载入实验板。现在,我们来学一下,有了硬件代码,如何生成bit文件。

Step 0:在Vivado安装目录中添加实验板信息

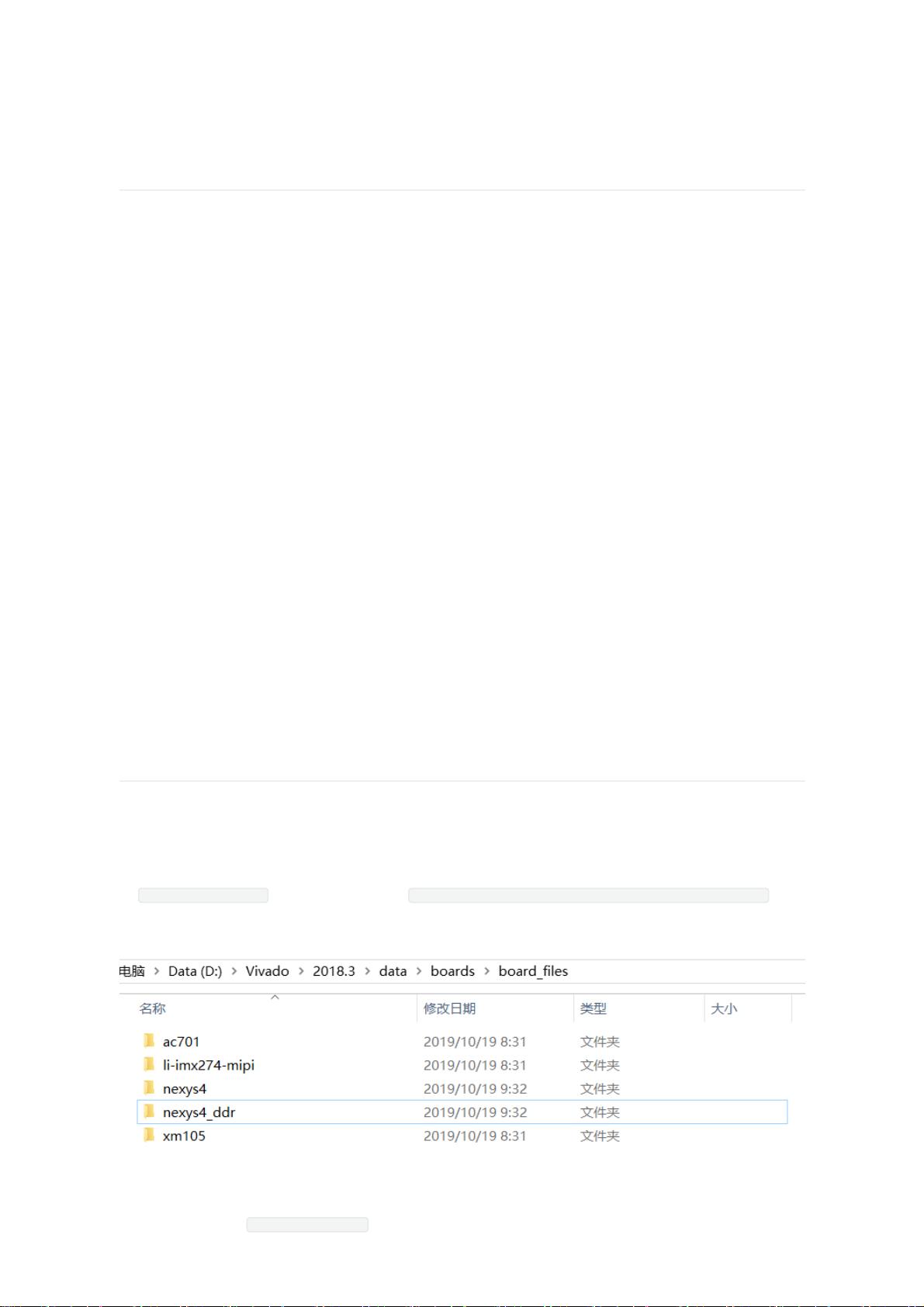

将 board_files.zip 的两个文件夹解压至 <VivadoInstallDir>/data/boards/board_files/ 。

解压后的目录应如图所示:

Step 1:新建项目

打开Vivado,点击 Create Project ,新建一个项目。

文润观书

- 粉丝: 26

- 资源: 317

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0