没有合适的资源?快使用搜索试试~ 我知道了~

交织器设计报告 1.61

需积分: 0 2 下载量 147 浏览量

2022-08-03

13:13:37

上传

评论 1

收藏 1.29MB PDF 举报

温馨提示

试读

42页

2.1 卷积交织器的实现 1 3.1 交织器的设计 3 3.2 时钟延时模块 13 3.3 解交织器 13 3.4 交织解交织综合模块 19 2.1 卷积交织器

资源推荐

资源详情

资源评论

实 验 报 告

课程名称:

数字系统设计

学生姓名:

陈永炜 201630257370

学生姓名:

邢靖 201630258803

学生姓名:

敖梓茗 201630257165

学生姓名:

蒲尧 201630258438

学生专业:

信息工程

开课学期:

2018——2019 第一学期

电子与信息学院

2018 年 9 月 制

目录

交织器的设计 .............................................................................. 1

一、设计卷积交织器的目的 ................................................ 1

二、卷积交织的原理 ............................................................ 1

2.1 卷积交织器的实现 .................................................... 1

三、模块设计 ........................................................................ 3

3.1 交织器的设计 ............................................................. 3

3.2 时钟延时模块 ........................................................... 13

3.3 解交织器 ................................................................... 13

3.4 交织解交织综合模块 ............................................... 19

四、设计中遇到的问题及解决方法 .................................. 23

五、设计总计 ...................................................................... 23

附录 A 全部源代码 ............................................................ 25

1

交织器的设计

一、设计卷积交织器的目的

在数字传输系统中,因为存在噪声、信道衰落等干扰因素,会使传输的信号发生错

误,产生误码。虽然数字信号的传输为了防止误码而会进行信道编码,增加传输码的冗

余,例如增加监督位等来克服信号在信道传输过程中的错误,但这种检错纠错能力是有限

的。例如当出现突发错误,出现大片连续误码时,这时信道的纠错是无能为力的。而卷积

交织器可以将原来的信息码打乱,这时尽管出现大面积突发性错误,这些可以通过解交织

器来进行分散,从而将大面积的错误较为平均地分散到不同的码段,利于信道纠错的实

现。

二、卷积交织的原理

卷积交织的原理其实是编码与解码,实际表现是“延迟”。发送端使用交织器,对原信

号序列通过某种逻辑进行打乱后发送,接收端通过反逻辑对打乱后的信息序列进行重新排

列,恢复出原信号序列。

解交织的结果是恢复出来的序列和原信号序列内容一致,但有一个延迟,体现在恢复

出来的信号序列开头有若干个“0”,“0”的个数取决于交织器的规格。

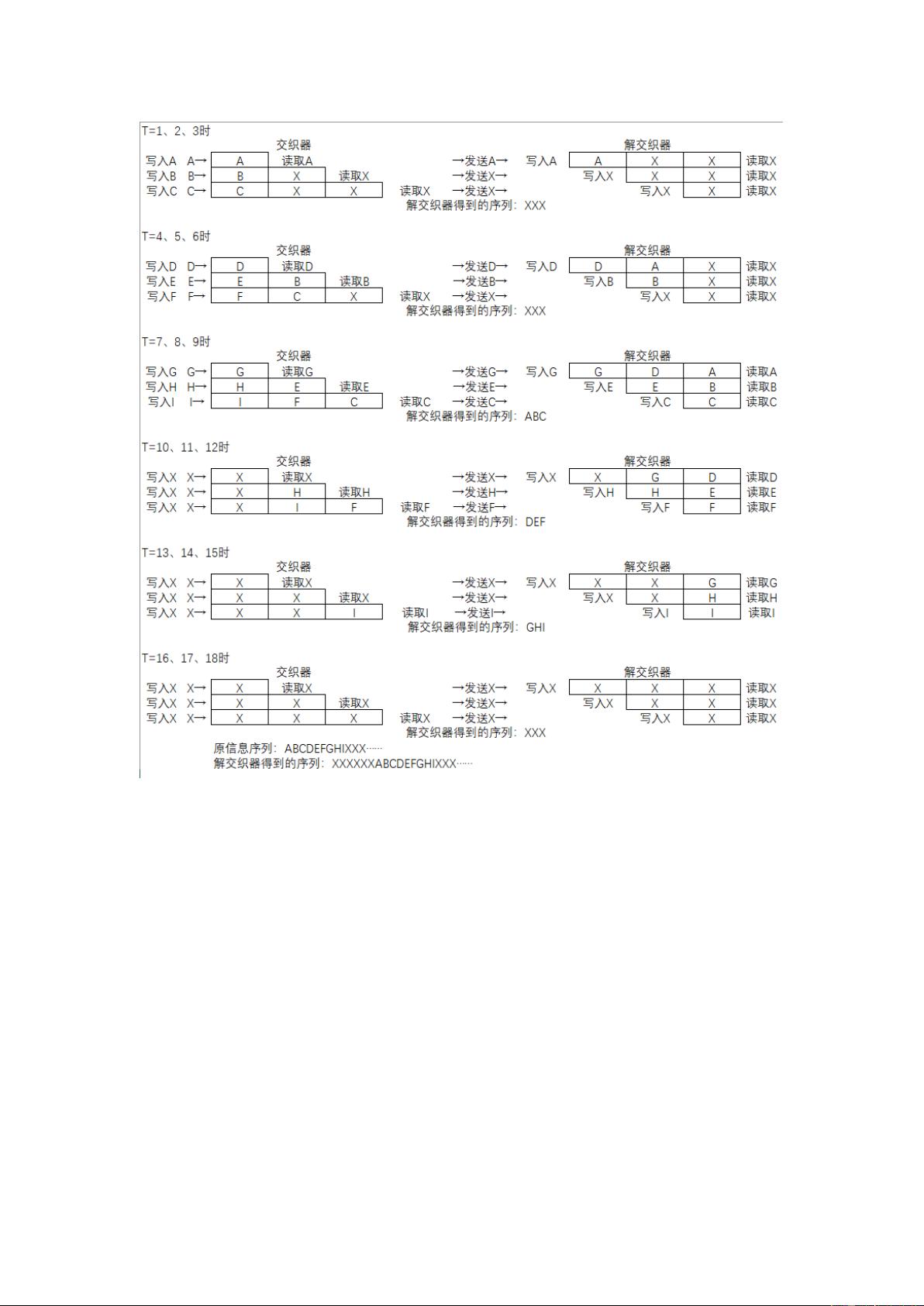

2.1 卷积交织器的实现

卷积交织有两种实现方法,一种是直接使用移位寄存器,另一种是使用 RAM 来实现

类似于移位寄存器的功能。

假设要发送的序列为 ABCDEFGHIXXX……,X 表示无效信息,示例使用三支路、

延迟 M=1 的移位寄存器实现,原理图如下图 1:

2

图 1 卷积交织原理

由结果可见,原信息序列 ABCDEFGHIXXX……经过交织器后序列被打乱,而经过解

交织器后恢复序列包含了原信号序列的全部信息,体现了编码与解码的原理。而恢复序列

和原信息序列相比,序列前端多了“XXXXXX……”,体现了交织器延迟的特性。利用移

位寄存器在硬件上实现延时虽然在理论上很简单,需要延时 T 个单位只需要 T 级寄存

器;但当系统变得庞大,需要的交织器的支路数、延时数变大时,需要的移位寄存器也会

相应地增多,而实验板不一定能提供这么多的资源。而且每个时钟的到来,都会有大量存

在于移位寄存器中的数据移动,会使整个系统的功耗剧烈升高。为了克服移位寄存器的缺

点,我们选择用 RAM 来模拟移位寄存器的功能。定义一个长度为 4 的 RAM,模拟移

位寄存器的功能如下:

例如对信息序列“ABCD”进行延时:

T=1 时,将 A 数据写入 1 单元,读出 2 单元数据,结果为空。

T=2 时,将 B 数据写入 2 单元,读出 3 单元数据,结果为空。

T=3 时,将 C 数据写入 3 单元,读出 4 单元数据,结果为空。

T=4 时,将 D 数据写入 4 单元,读出 1 单元数据,结果为 A。

刚好延迟了 4 个时钟。如此循环,序列“ABCD”就延迟了 4 个时钟后输出,和 4

剩余41页未读,继续阅读

资源评论

以墨健康道

- 粉丝: 25

- 资源: 307

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功