A01_多周期处理器移植_2016K80099290291

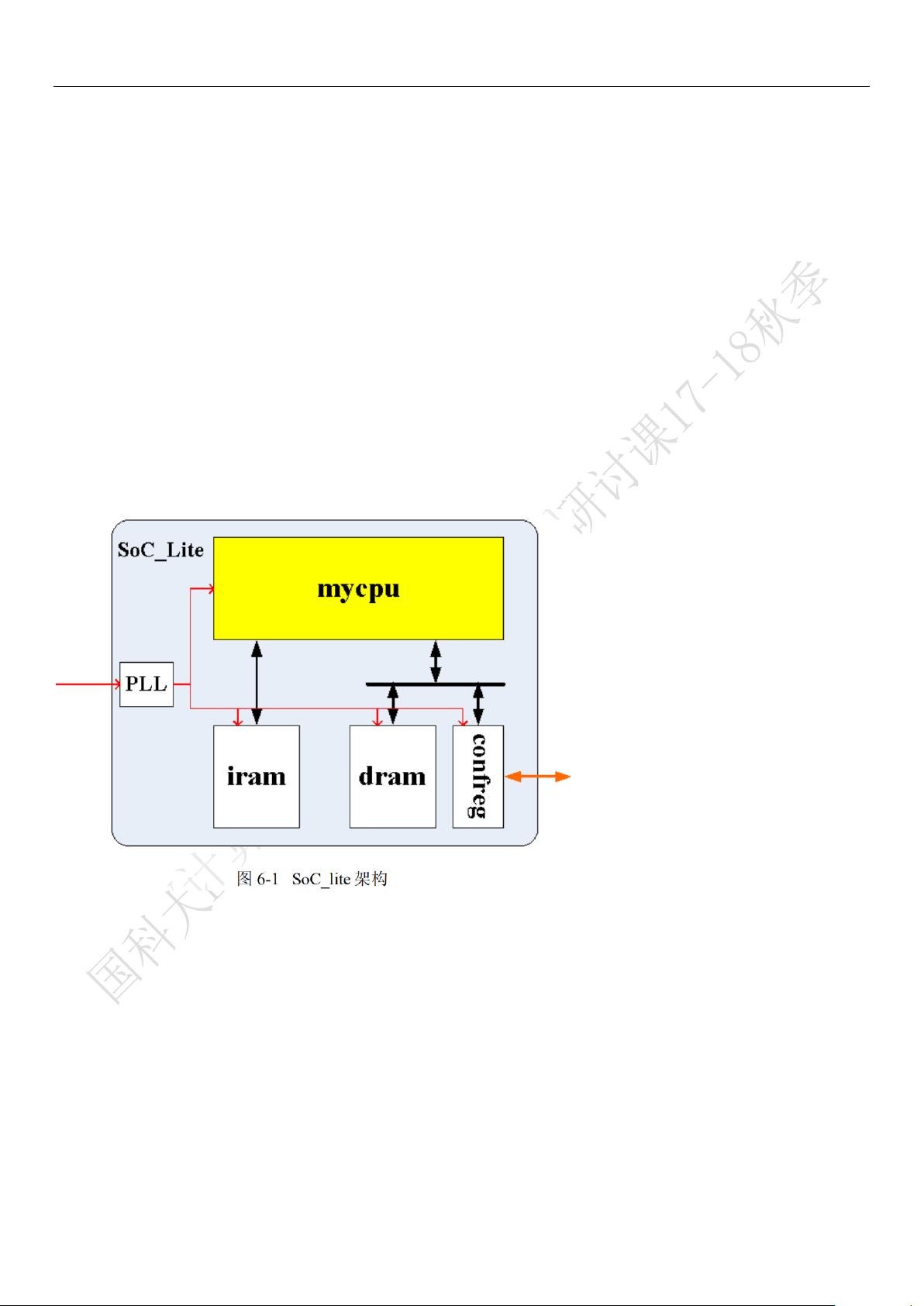

"A01_多周期处理器移植_2016K80099290291" 涉及的是一个处理器设计项目,主要任务是将龙芯三级流水线处理器的代码替换为多周期处理器的代码,并进行系统级整合和测试。 提到的主要设计步骤包括: 1. 在`mycpu_top`模块中,设计者需要定义接口,调用`mips_cpu`模块,以确保新设计的多周期处理器与原有接口的兼容性。 2. 在`mips_cpu`模块中,工作原理需要重新定义,以适应多周期处理的逻辑。 "软件/插件 测试 网络协议"表明这个项目不仅涉及到硬件设计,还涉及到软件和测试方面,可能包括软件的集成、插件的使用以及网络协议的考量,但具体细节未在描述中明确给出。 【部分内容】中详细阐述了实验的组织结构和流程: 1. 实验任务主要是替换`myCPU`中的龙芯三级流水代码,使用多周期代码,并调整顶层接口,使其适应`SoC_lite`框架。 2. 实验环境包括多个目录,如`cpu132_gettrace`、`rtl`、`testbench`、`func`和`mycpu_verify`等,分别负责不同功能,如生成参考跟踪信息、仿真、Vivado工程、编译和验证自实现的CPU。 3. 使用Vivado进行硬件设计和调试,通过`run all`自动测试寻找错误,最终在硬件板上进行测试,确保设计的正确性。 4. `testbench`目录下的`tb_top.v`负责捕获调试信息,生成参考跟踪文件与实际结果进行对比,确保CPU功能的正确实现。 在进行多周期处理器移植的过程中,需要考虑以下关键知识点: 1. **多周期处理器设计**:与单周期处理器相比,多周期处理器将指令的各个阶段(如取指、解码、执行、访存、写回)分开在不同的时钟周期内完成,以提高性能并简化设计。设计中需要考虑控制逻辑、数据路径以及各级之间的时序协调。 2. **接口设计**:`mycpu_top`模块是整个系统的顶层,需要定义与外部系统交互的接口,包括输入输出信号,确保与`mips_cpu`模块和其他子系统(如内存、外设)的正确通信。 3. **VHDL/Verilog编程**:硬件描述语言(如VHDL或Verilog)用于描述处理器的行为和结构,实现模块化设计。 4. **仿真与验证**:使用硬件描述语言的测试平台(如`tb_top.v`)进行功能仿真,确保处理器在不同场景下的正确行为。通过比较实际生成的跟踪信息与预期的参考跟踪文件,可以发现设计中的错误。 5. **FPGA实现**:使用工具如Vivado进行硬件综合、布局布线,生成适配特定FPGA的配置文件,然后在硬件板上进行实际运行和测试。 6. **软件编译与链接**:`func`目录下的内容表明存在软件层面的测试,包括汇编语言的编译和链接,以生成可执行文件测试CPU功能。 7. **系统级集成**:CPU需要与存储器、外设等其他组件协同工作,因此需要考虑整个SoC的集成,包括地址映射、总线协议、中断处理等。 通过以上分析,可以看出这个项目是一个复杂的嵌入式系统设计,涵盖了硬件处理器设计、软件编译、系统集成、验证和测试等多个环节。

剩余9页未读,继续阅读

- 粉丝: 855

- 资源: 316

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (源码)基于C语言的系统服务框架.zip

- (源码)基于Spring MVC和MyBatis的选课管理系统.zip

- (源码)基于ArcEngine的GIS数据处理系统.zip

- (源码)基于JavaFX和MySQL的医院挂号管理系统.zip

- (源码)基于IdentityServer4和Finbuckle.MultiTenant的多租户身份认证系统.zip

- (源码)基于Spring Boot和Vue3+ElementPlus的后台管理系统.zip

- (源码)基于C++和Qt框架的dearoot配置管理系统.zip

- (源码)基于 .NET 和 EasyHook 的虚拟文件系统.zip

- (源码)基于Python的金融文档智能分析系统.zip

- (源码)基于Java的医药管理系统.zip

信息提交成功

信息提交成功

评论0