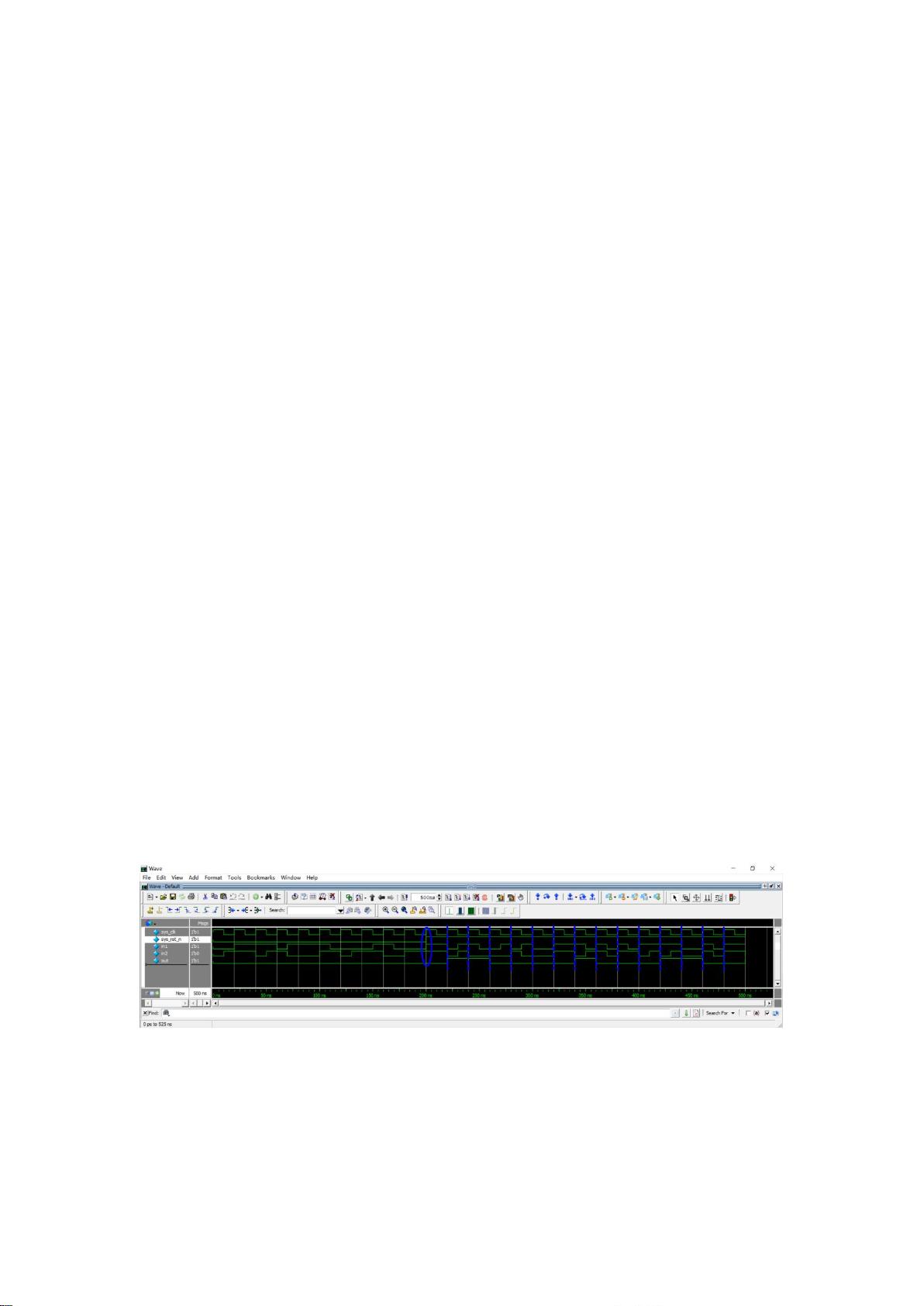

在电子设计自动化(EDA)领域,特别是在数字集成电路的设计和验证过程中,Verilog 是一种常用的硬件描述语言(HDL)。在Verilog中,正确地使用赋值符号对于确保时序逻辑和组合逻辑的正确性至关重要。本文将深入探讨在仿真文件中使用“=”和“<=”赋值的区别以及它们在时序逻辑和组合逻辑中的应用。 我们要明确两个基本概念: 1. **时序逻辑**:涉及到信号随时间变化的电路,如寄存器、触发器等,它们通常与时钟信号同步。 2. **组合逻辑**:不依赖于时间顺序,仅基于当前输入产生输出的电路。 在Verilog中,这两个概念的表示方式不同: - **“=”赋值**:用于表示组合逻辑。它立即更新信号的值,而不论时钟边缘如何。在仿真中,这用于描述逻辑运算的结果或任何非时序操作。 - **“<=”赋值**:称为非阻塞赋值,用于表示时序逻辑。它会在当前时钟周期结束时异步地更新变量的值,确保数据在时钟边沿之后稳定。 在上述的“测试代码1”中,时钟“sys_clk”用“=”赋值,而输入信号“sys_rst_n”,“in1”,“in2”用“<=”赋值,这是正确的做法。这样确保了时钟在时钟边沿变化时被正确处理,而输入信号则根据需要更新,符合时序逻辑的定义。在仿真中,尽管这种方法在Testbench中并不严格要求,但能保证逻辑的正确性。 然而,在“测试代码2”中,时钟“sys_clk”和输入信号都使用“<=”赋值,这是一个错误。时钟不应使用非阻塞赋值,因为这可能导致信号在时钟边沿之前或之后的不确定状态,从而导致仿真结果错误。在这个例子中,由于不正确的赋值,可能会导致仿真出的波形不符合预期,进而影响测试结果的准确性。 此外,测试还涉及到了对运算符“|”(或)、“+”(加)、“^”(异或)的验证。在组合逻辑中,这些运算符应该与“=”赋值一起使用,以确保它们在时钟周期内立即完成计算。而在时序逻辑中,它们通常出现在非阻塞赋值的右侧,作为时钟边沿触发的条件。 理解并正确使用“=”和“<=”赋值是编写Verilog代码的基础。在Testbench中,尽管非阻塞赋值的使用可能不会直接影响最终电路的功能,但为了确保测试的准确性和可预测性,最好遵循正确的编程习惯。在描述时序逻辑时使用“<=”,描述组合逻辑时使用“=”。这样做不仅可以帮助避免仿真错误,也有助于在代码综合阶段生成更有效的电路实现。

剩余9页未读,继续阅读

- 粉丝: 32

- 资源: 327

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 推荐一款JTools的call-this-method插件

- html+css网页设计马林旅行社移动端4个页面.zip

- Coda Hale Metrics 库的 Go 移植.zip

- java学籍管理系统源码带本地搭建教程数据库 MySQL源码类型 WebForm

- php+mysql学生成绩查询(系统)

- Bazel 的 Go 规则.zip

- Android ListView下拉刷新 Demo.zip

- Python实现基于一维卷积神经网络(1D-CNN)的多元时间序列分类源码+文档说明

- java基于springBoot课程评价系统源码数据库 MySQL源码类型 WebForm

- 5G工业无线路由器说明书

信息提交成功

信息提交成功

评论0