5.4.1_硬布线控制器1

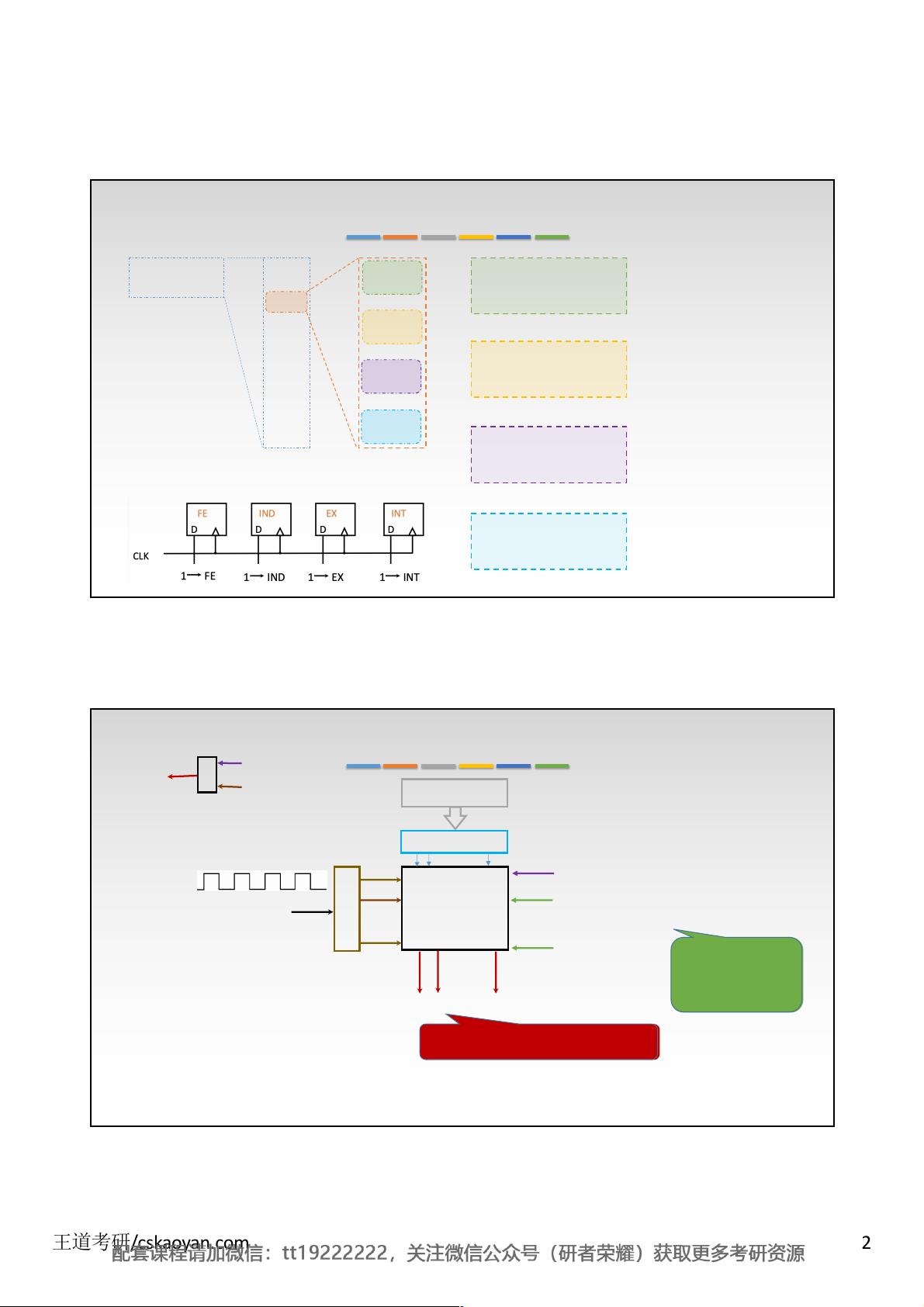

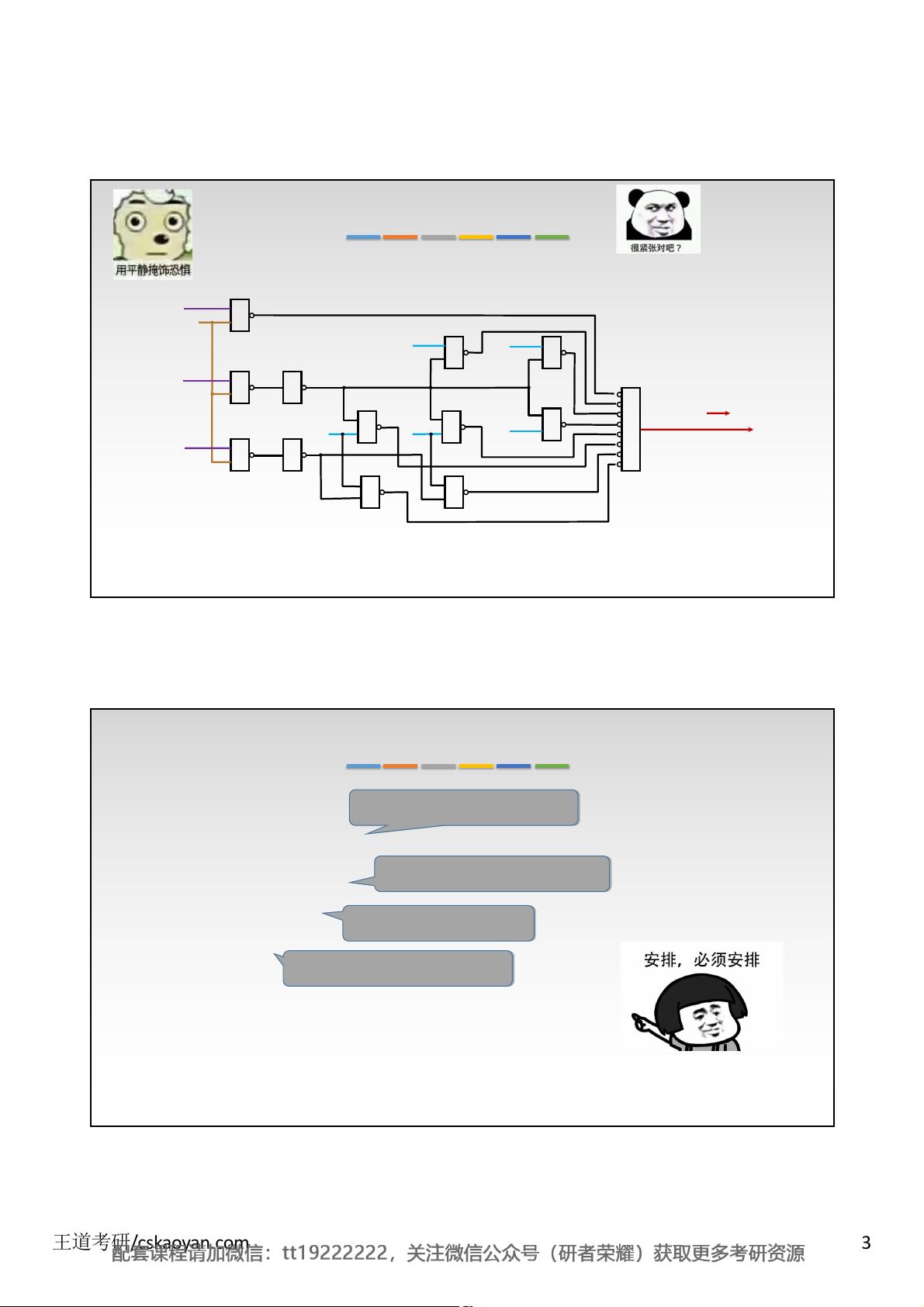

硬布线控制器是CPU设计中的一个重要组成部分,它负责协调和控制CPU内部各个部件的操作。在设计硬布线控制器时,通常需要遵循以下步骤: 1. **分析微操作序列**:我们需要对指令的执行过程进行细致的分析,确定每个阶段(取值、间址、执行、中断)所需的微操作序列。例如,在取值阶段,所有指令都需要从存储器读取指令,因此微操作可能包括PC到MAR的数据传输、MAR到MDR的数据传输以及MDR到IR的数据传输。 2. **选择控制方式**:在CPU控制方式的选择上,硬布线控制器是一种固定逻辑结构,不依赖于微程序,而是直接通过硬件电路实现控制。这种设计方式速度快,但灵活性较低。 3. **安排微操作时序**:接下来,我们需要安排微操作的时序,确保它们能在适当的时间执行。考虑到可能有的指令执行周期不同,通常会选择一个定长的机器周期,以最长的微操作序列为基础,确保所有指令都能在规定的时序内完成。如果某些指令在某个阶段没有操作,可以在该阶段的末尾安排这些微操作。 4. **电路设计**:我们将微操作转化为逻辑表达式,并设计电路来实现这些微操作。例如,微操作 `(PC)àMAR` 可能由微命令 `C1` 控制,其逻辑表达式可能是 `FE·T0`,表示只有在取指周期 (`FE=1`) 的第一拍 (`T0`) 才有效。电路设计包括操作码译码器、节拍发生器、各种控制信号的逻辑组合等。 在硬布线控制器设计中,通常需要关注以下几个关键点: - **操作码译码器**:根据指令操作码,决定当前指令需要执行的微操作。 - **时钟信号**:机器的主时钟频率决定了每个机器周期的长度,而节拍发生器则根据时钟信号产生内部的节拍信号。 - **状态条件**:CPU的状态信息,如标志位,可能会影响微命令的生成。 - **逻辑表达式**:每个微操作的启动可以通过逻辑表达式来描述,例如 `FE·T1+ IND·T1(ADD+STA+LDA+JMP+BAN) + EX·T1(ADD+LDA)`,用于控制数据从内存读取到寄存器的微操作。 在实际设计中,还需要考虑如何在有限的节拍内并行执行相容的微操作,以及如何处理不同指令执行时间不同的问题。例如,对于定长机器周期,如果某个指令在一个机器周期内无法完成,可以将剩余的微操作安排在机器周期的末尾。 硬布线控制器设计是一个复杂的过程,需要对计算机体系结构有深入理解,涉及到指令执行流程、微操作控制、时序安排和逻辑电路设计等多个方面。虽然考试中可能不会直接考察具体的电路设计,但理解这些基本概念对于理解CPU的工作原理至关重要。

剩余10页未读,继续阅读

- 粉丝: 13

- 资源: 331

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功

评论0