没有合适的资源?快使用搜索试试~ 我知道了~

高等计算机体系结构-第一讲-预习版1

需积分: 0 0 下载量 162 浏览量

2022-08-03

16:28:36

上传

评论

收藏 861KB PDF 举报

温馨提示

试读

15页

Gates to C and Beyond(计算机系统概论)第一章(基础)• Patterson & Hennessy‘s Computer Organizat

资源详情

资源评论

资源推荐

1

高等计算机体系结构

第一讲: 课程概论&计算机体系结构的基本概念

栾钟治

北京航空航天大学 计算机学院 中德联合软件研究所

你们为什么而来

汇编程序最终是如何按照数字

逻辑的方式执行的?

这中间发生了什么?

一台用逻辑门和连线设计实现

的计算机是如何满足那些特定目

标的?

2

“C” :一种计算模式

数字逻辑:一种计算模式

计算机系统工作的程序员视角

计算机系统工作的硬件设计者视角

体系架构师/微架构师的视角:

如何设计一台能够满足

系统设计目标的计算机。

这里如何选择将严重影响

软件设计者和硬件设计者

Lw $t0, 0($2)

Lw $t1, 4($2)

Sw $t1, 0($2)

Sw $t0, 4($2)

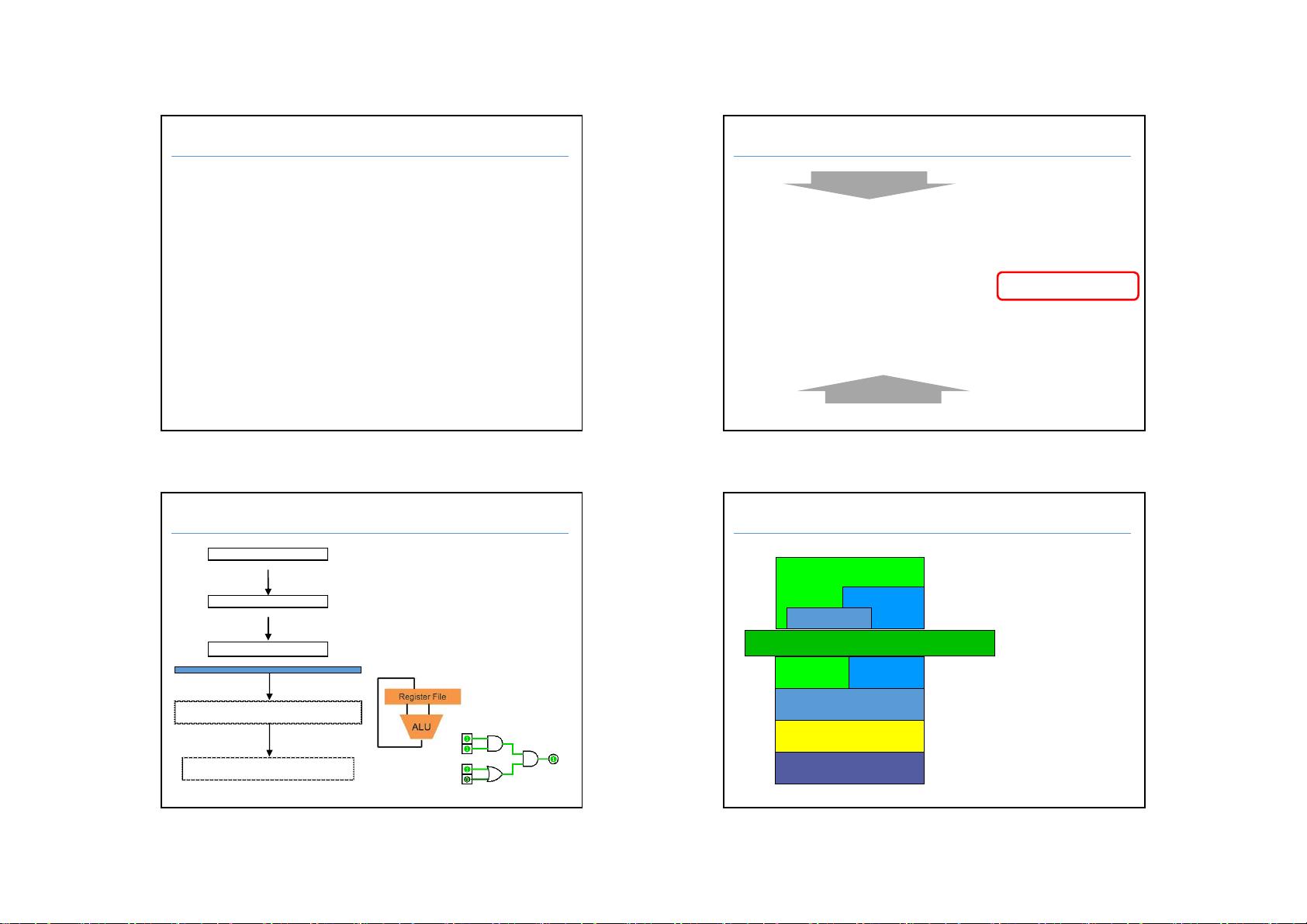

高级语言程序(e.g. C)

汇编程序(e.g. MIPS)

机器语言程序(MIPS)

硬件结构描述

(e.g. 硬件框图)

编译器

汇编器

机器解释

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

0000 1001 1100 0110 1010 1111 0101 1000

1010 1111 0101 1000 0000 1001 1100 0110

1100 0110 1010 1111 0101 1000 0000 1001

0101 1000 0000 1001 1100 0110 1010 1111

逻辑电路描述

(电路原理图)

体系结构实现

计算机系统的层次结构

3

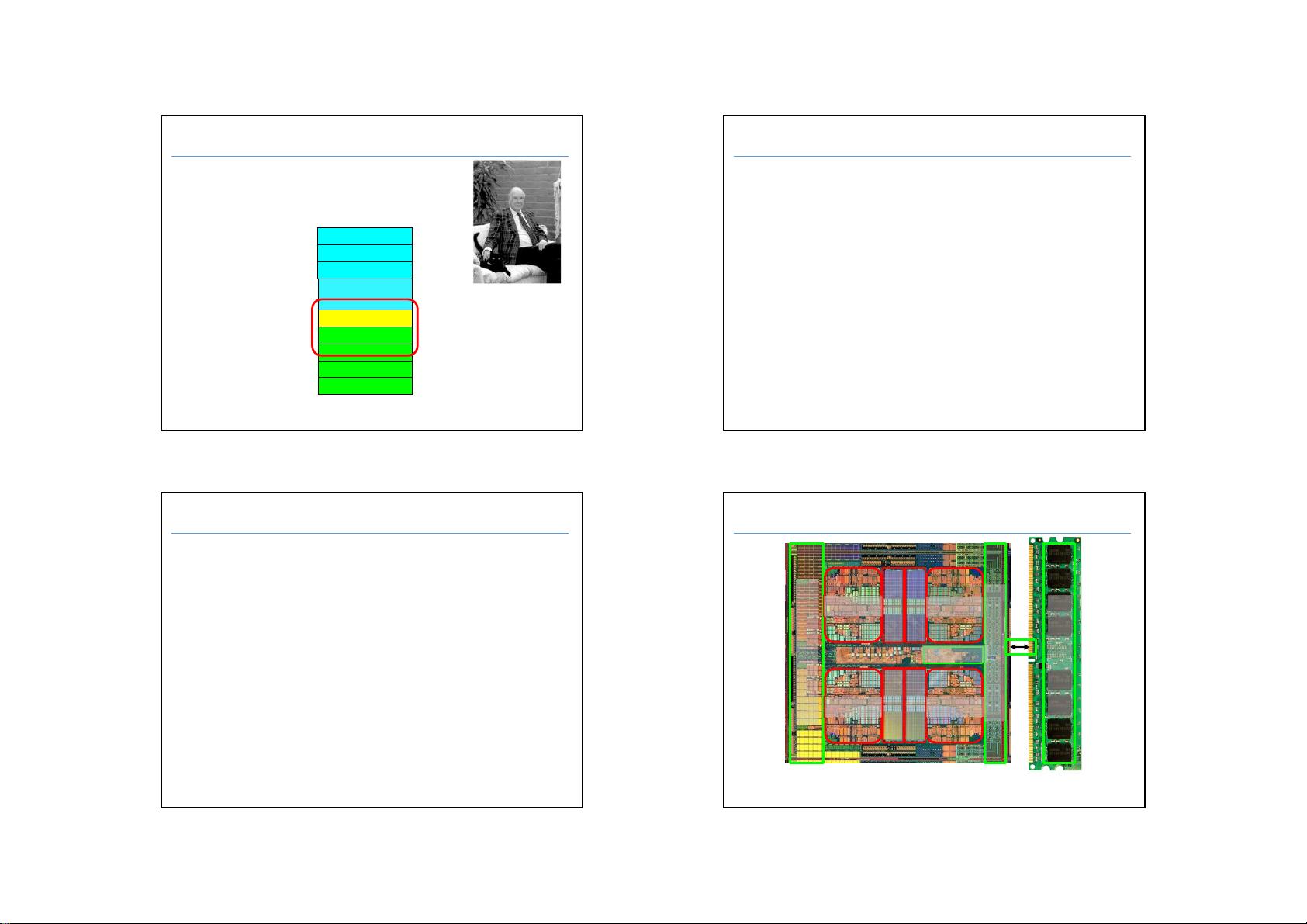

计算机系统的层次结构

应用

OS

编译器

指令集体系结构(ISA)

指令处理 输入/输出

硬件设计抽象层次

数据通路 & 控制

数字设计

电路设计

软件抽象层次

4

1 2

3 4

2

系统层次结构

5

微体系结构

ISA (体系结构)

程序/语言

算法

问题

逻辑

电路

运行时系统

(VM, OS, MM)

电子

“The purpose of computing is insight” (Richard Hamming)

我们在解决问题过程中获得洞察

如何确保可以用电子解决问题?

抽象的力量

• 分层描述系统产生了抽象

• 抽象: 上一层只需要知道跟下一层的接口,而不需要知道下一层是

如何实现的

• 例如, 高级语言的程序员并不需要“真的”了解什么是ISA以及计算

机是如何执行指令的

• 抽象提高了生产效率

• 不需要考虑底层所做出的决策

• 例如, Java编程 vs. C编程 vs. 汇编语言编程 vs. 二进制代码 vs. 每一个

时钟周期作用在每个晶体管上的电信号

• 那么,为什么你想要知道到底下一层或者上一层发

生了什么呢?

6

跨越抽象层次

• 如果一切顺利,不知道别的层次发生了什么也无

关紧要

• 但是,如果

• 你写的程序跑得很慢呢?

• 你写的程序执行得不正确呢?

• 你写的程序能耗太高呢?

• 但是,如果

• 在你设计的硬件上编程太困难呢?

• 你设计的硬件效率太低因为你为软件提供的原语不够合理呢?

• 这门课的一个目标就是理解一个处理器是如何工

作在软件层面之下以及硬件的决策是如何影响软

件和程序员的

7

一个例子

8

CORE 1

L2 CACHE 0

SHARED L3 CACHE

DRAM INTERFACE

CORE 0

CORE 2

CORE 3

L2 CACHE 1

L2 CACHE 2

L2 CACHE 3

DRAM BANKS

多核芯片

* AMD Barcelona

DRAM MEMORY

CONTROLLER

5 6

7 8

3

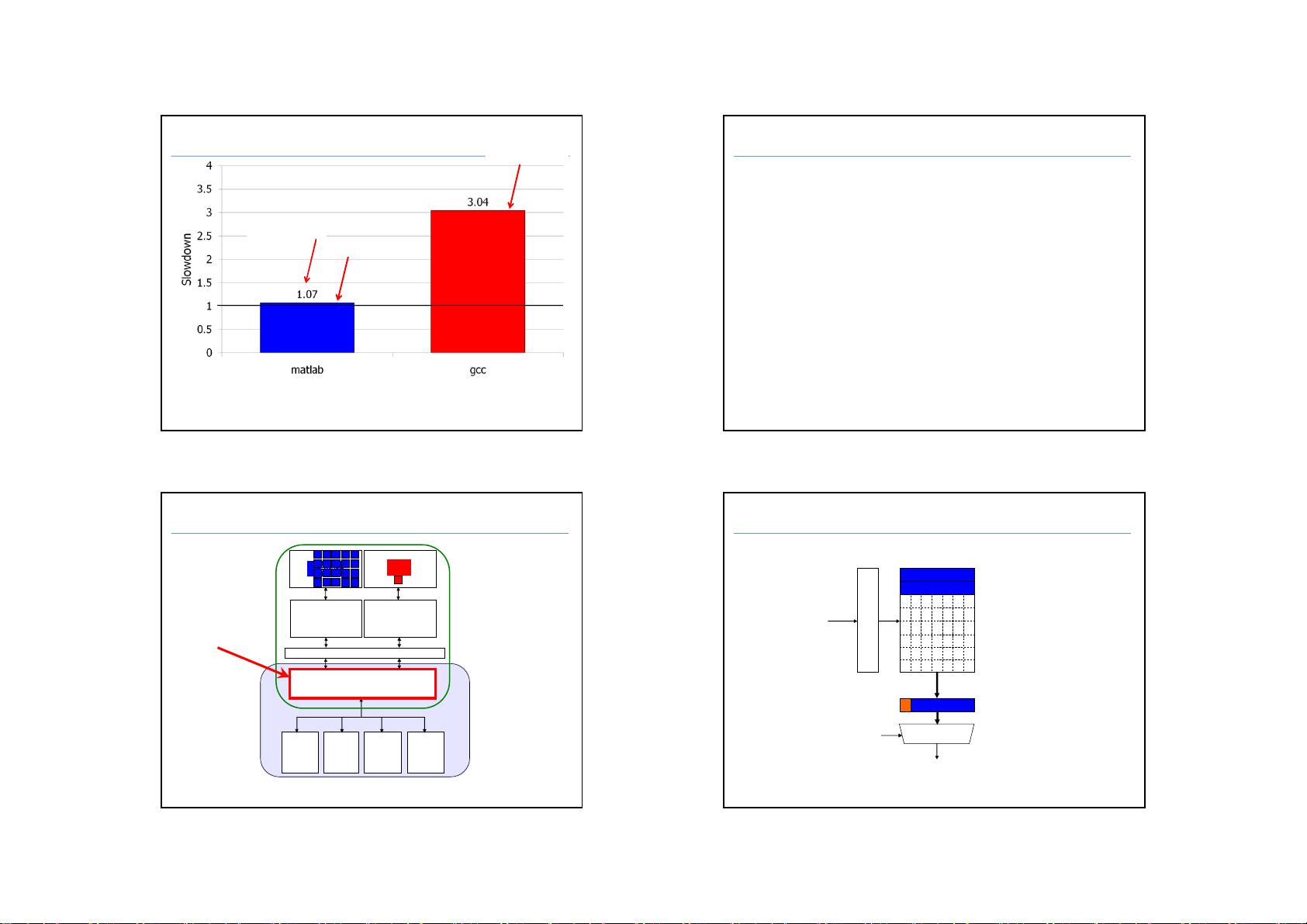

多核环境下的性能下降现象

9

内存性能抢占

低优先级

高优先级

(Core 0) (Core 1)

Moscibroda and Mutlu, “Memory performance attacks: Denial of memory service

in multi-core systems,” USENIX Security 2007.

问题

• 如果你不知道处理器是如何执行程序的,你是否

有可能找出性能下降差异的原因?

• 你能在不知道底层发生了什么的情况下解决问题

吗?

10

为什么性能下降会有这么大的差异?

11

CORE 1 CORE 2

L2

CACHE

L2

CACHE

DRAM MEMORY CONTROLLER

DRAM

Bank 0

DRAM

Bank 1

DRAM

Bank 2

共享的DRAM

存储系统

多核芯片

不公平性

INTERCONNECT

matlab

gcc

DRAM

Bank 3

DRAM Bank的操作

12

Row Buffer

(Row 0, Column 0)

Row decoder

Column mux

Row address 0

Column address 0

Data

Row 0Empty

(Row 0, Column 1)

Column address 1

(Row 0, Column 85)

Column address 85

(Row 1, Column 0)

HITHIT

Row address 1

Row 1

Column address 0

CONFLICT !

Columns

Rows

访问地址:

9 10

11 12

剩余14页未读,继续阅读

茶啊冲的小男孩

- 粉丝: 25

- 资源: 326

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0