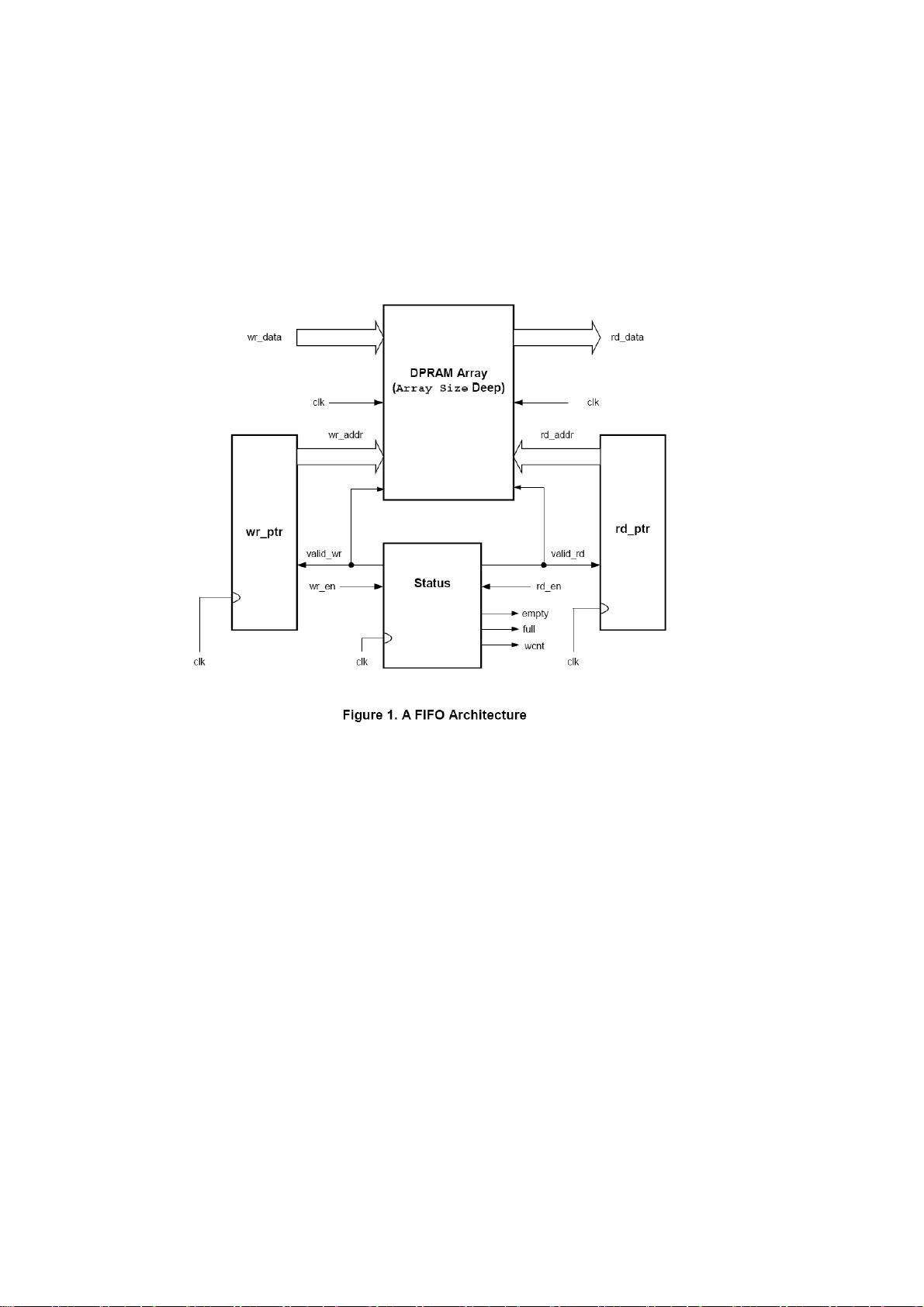

### 基于VERILOG的异步FIFO结构详解 #### 引言 异步FIFO(First In First Out)结构是集成电路设计中的常见需求,尤其在处理不同时钟域之间的数据传输时。FIFO的基本功能是按照先进先出的原则存储和提取数据,其在异步环境下工作时,需在不同的时钟频率或相位间无缝衔接数据流。本文旨在深入探讨基于Verilog的异步FIFO设计,从简单的单时钟结构出发,逐步过渡到更为复杂的双时钟异步FIFO设计。 #### 单时钟FIFO结构 单时钟FIFO作为入门级模型,虽在实际应用中较为罕见,但却是理解异步FIFO设计的基础。这类FIFO工作在一个统一的时钟域内,简化了同步问题,便于初学者理解和实践。 **组件分析**: 1. **RAM存储器**:采用具有独立读写端口的RAM,便于独立控制读写操作。若使用单端口RAM,则需引入仲裁机制确保同一时间只执行读或写操作。 2. **读写指针**:由两个计数器分别产生,宽度为`log2(array_size)`,指示读写位置。读指针(read pointer)指向待读取数据的位置,写指针(write pointer)指向待写入数据的位置。 3. **状态模块**:负责监控FIFO的“空”、“满”状态,提供外部电路决策依据,避免数据溢出或欠载。 #### 双时钟异步FIFO结构 异步FIFO的核心在于处理不同时钟域间的数据传递,避免数据冲突和亚稳态问题。设计上,双时钟FIFO结构分为多个阶段,每一步都在提升对时钟域差异的适应性和数据完整性。 **关键概念**: 1. **时钟域跨越**:数据在进入和离开FIFO时,需要从源时钟域转换至目标时钟域,这涉及到跨时钟域同步技术的应用。 2. **读写分离**:保持读写操作在时间和空间上的独立性,防止数据竞争。 3. **状态检测**:“满”、“空”信号的生成更为复杂,需考虑双时钟环境下的指针比较和同步策略。 **设计步骤**: 1. **双时钟结构1**:初步引入异步读写逻辑,解决基本的时钟域跨越问题。 2. **双时钟结构2**:优化读写同步机制,增强数据稳定性和系统可靠性。 3. **双时钟结构3**:综合前两步经验,实现高效稳定的异步数据传输。 4. **脉冲模式FIFO**:适用于特定场景,如需要快速响应的系统,采用脉冲触发方式控制读写操作。 #### 深度解析:DPRAM在异步FIFO中的角色 DPRAM(Dual Port Random Access Memory)在异步FIFO设计中承担核心存储角色。根据是否寄存读出信号,DPRAM的使用方式有所不同,直接影响到读写逻辑的设计: 1. **无寄存输出**:读操作在FIFO输出数据有效之前发送,读指针需在读操作完成时立即更新。这种情况下,状态信号的判断和数据的有效性依赖于严格的时序控制。 2. **寄存输出**:DPRAM自动保留读出数据,读指针可以在数据有效后更新,简化了读操作的同步要求。 #### 结语 异步FIFO设计不仅考验设计师对Verilog语言的掌握,更是对时钟域同步、数据完整性以及系统架构深刻理解的体现。从单时钟到双时钟结构的演变,展现了从理论到实践,从简单到复杂的完整学习路径,为IC设计者提供了宝贵的参考资料和实践经验。通过深入研究和实践,设计师能够灵活应对各种复杂场景,设计出高性能、高可靠性的异步FIFO系统。

剩余17页未读,继续阅读

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功