Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device des-

ignations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and

service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Al-

tera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants

performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the ap-

plication or use of any information, product, or service described herein except as expressly agreed to in writing by Altera

Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in-

formation and before placing orders for products or services.

ii MegaCore Version 2.2.1 Altera Corporation

FFT MegaCore Function User Guide

UG-FFT-2.0

Altera Corporation iii

Contents

About This User Guide ............................................................................. v

Revision History ........................................................................................................................................ v

How to Contact Altera .............................................................................................................................. v

Typographic Conventions ...................................................................................................................... vi

Chapter 1. About This MegaCore Function

Release Information ............................................................................................................................... 1–1

Device Family Support ......................................................................................................................... 1–1

New in Version 2.2.1 ............................................................................................................................. 1–2

Features ................................................................................................................................................... 1–2

General Description ............................................................................................................................... 1–3

OpenCore Plus Evaluation .............................................................................................................. 1–3

DSP Builder Support ........................................................................................................................ 1–3

Performance ............................................................................................................................................ 1–4

Chapter 2. Getting Started

Design Flow ............................................................................................................................................ 2–1

FFT Walkthrough .................................................................................................................................. 2–2

Create a New Quartus II Project .................................................................................................... 2–2

Launch IP Toolbench ....................................................................................................................... 2–3

Step 1: Parameterize ......................................................................................................................... 2–5

Step 2: Set Up Simulation ................................................................................................................ 2–8

Step 3: Generate .............................................................................................................................. 2–10

Simulate the Design ............................................................................................................................. 2–14

Simulate in the MATLAB Software ............................................................................................. 2–14

Simulate with IP Functional Simulation Models ....................................................................... 2–15

Simulate in the ModelSim Software ............................................................................................ 2–15

Compile the Design ............................................................................................................................. 2–16

Program a Device ................................................................................................................................ 2–16

Set Up Licensing .................................................................................................................................. 2–17

Chapter 3. Specifications

Functional Description .......................................................................................................................... 3–1

OpenCore Plus Time-Out Behavior ............................................................................................... 3–3

FFT Processor Engine Architectures ................................................................................................... 3–3

Quad-Output FFT Engine Architecture ........................................................................................ 3–3

Single-Output FFT Engine Architecture ....................................................................................... 3–4

I/O Data Flow Architectures ............................................................................................................... 3–6

Streaming ........................................................................................................................................... 3–6

Buffered Burst ................................................................................................................................... 3–8

iv MegaCore Version 2.2.1 Altera Corporation

FFT

Contents

Burst ................................................................................................................................................. 3–10

Performance & Resource Usage ........................................................................................................ 3–10

Parameters ............................................................................................................................................ 3–15

Signals ................................................................................................................................................... 3–17

Appendix A. FFT/IFFT Exponent Scaling Values

Calculating Possible Exponent Values .............................................................................................. A–1

Implementing Scaling .......................................................................................................................... A–2

Altera Corporation MegaCore Version 2.2.1 v

FFT

About This User Guide

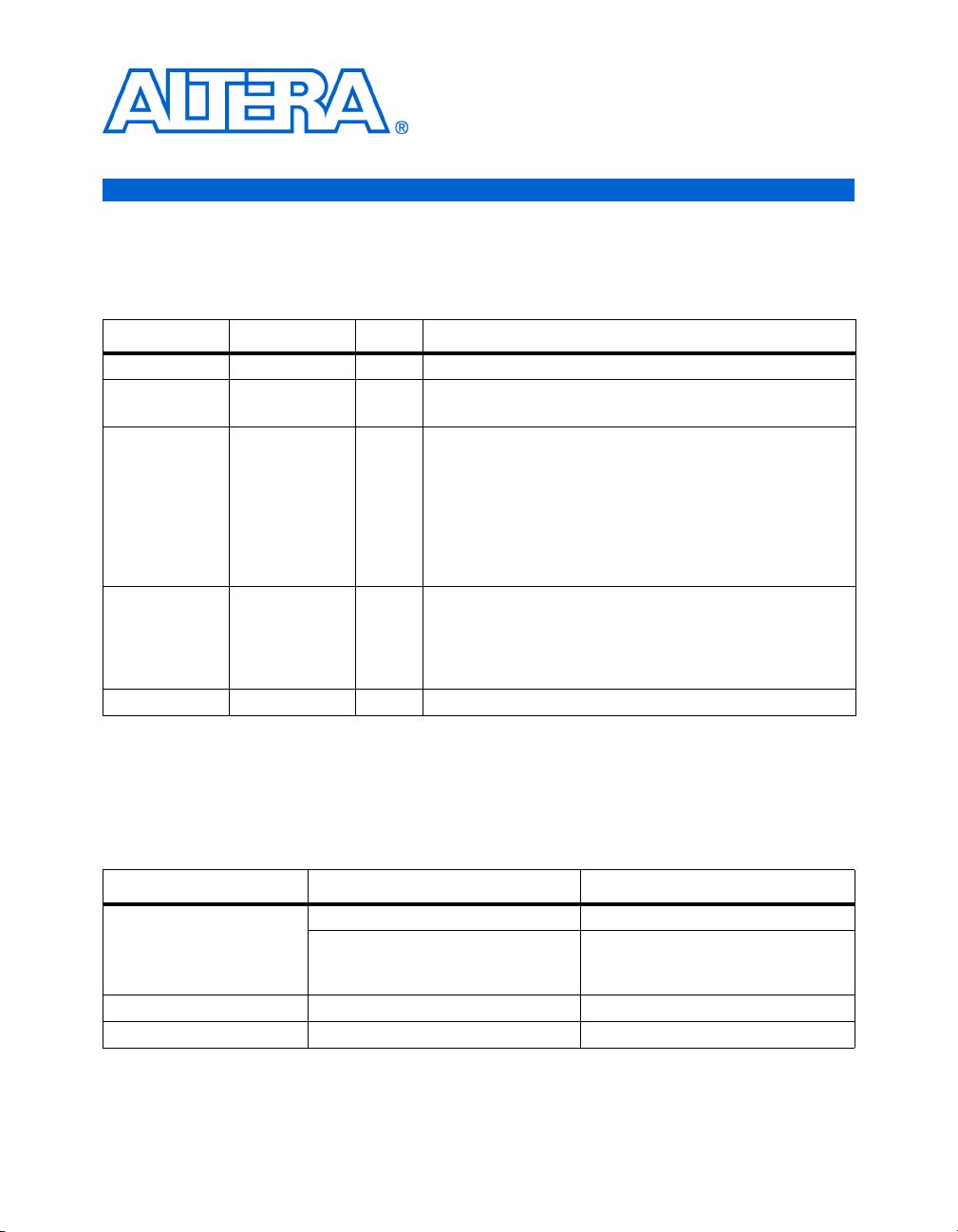

Revision History

The table below displays the revision history for chapters in this user

guide.

How to Contact

Altera

For technical support or other information about Altera

®

products, go to

the Altera world-wide web site at www.altera.com. You can also contact

Altera through your local sales representative or any of the sources listed

below..

Chapter Date Version Changes Made

All April 2006 2.2.1 ● Updated format..

All October 2005 2.2.0

● Added HardCopy

®

II support

● Miscellaneous updates to fix bugs

1 June 2004 2.1.0

● Updated release information and device family support

tables

● Updated the features

● Added OpenCore

®

Plus description

● Added DSP Builder support information

● Updated the performance information

● Enhancements include support for Cyclone

™

II devices; bit-

accurate MATLAB models; DSP Builder ready

2 June 2004 2.1.0

● Updated system requirements

● Updated tutorial instructions and screenshots

● Added MATLAB output files names to output file table

● Added MATLAB simulation and IP functional simulation

model information

3 June 2004 2.1.0

● Updated the performance information

Information Type USA & Canada All Other Locations

Technical support www.altera.com/mysupport/ www.altera.com/mysupport/

800-800-EPLD (3753)

(7:00 a.m. to 5:00 p.m. Pacific Time)

+1 408-544-8767

7:00 a.m. to 5:00 p.m. (GMT -8:00)

Pacific Time

Product literature www.altera.com www.altera.com

Altera literature services literature@altera.com literature@altera.com

- 1

- 2

前往页