没有合适的资源?快使用搜索试试~ 我知道了~

MPC8347中文手册 第4章 复位、时钟同步和初始化

需积分: 9 1 下载量 124 浏览量

2012-09-29

23:02:34

上传

评论

收藏 1.1MB DOC 举报

温馨提示

试读

38页

powerpc的芯片的中文手册非常少见。我这里有一整套mpc8347的中文手册。本来是在豆丁上放着的,现在放到CSDN上。分数高,但是内容还是划算的!本人csdn积分很少,最近急需分数。 陆续将上传其他章节的中文手册。

资源推荐

资源详情

资源评论

第四章 复位、时钟同步和初始化

本章介绍复位、时钟同步和 MPC8349E 设备的整体初始化,包括复位配置信号的定义及其选项。

此外还介绍配置、控制和状态寄存器。注意,本书的每一章都介绍了一个部件额外的具体的初始化

过程。

4.1 概述

复位、时钟同步和控制信号为设备的操作提供很多选项。可以在硬复位或上电复位期间配置不

同的模式和特性。大多数可配置特性由复位配置字装入设备,只有很少一部分信号用作复位序列期

间的复位配置输入。

4.2 外部信号说明

下面几节详细说明复位和时钟信号。

4.2.1 复位信号

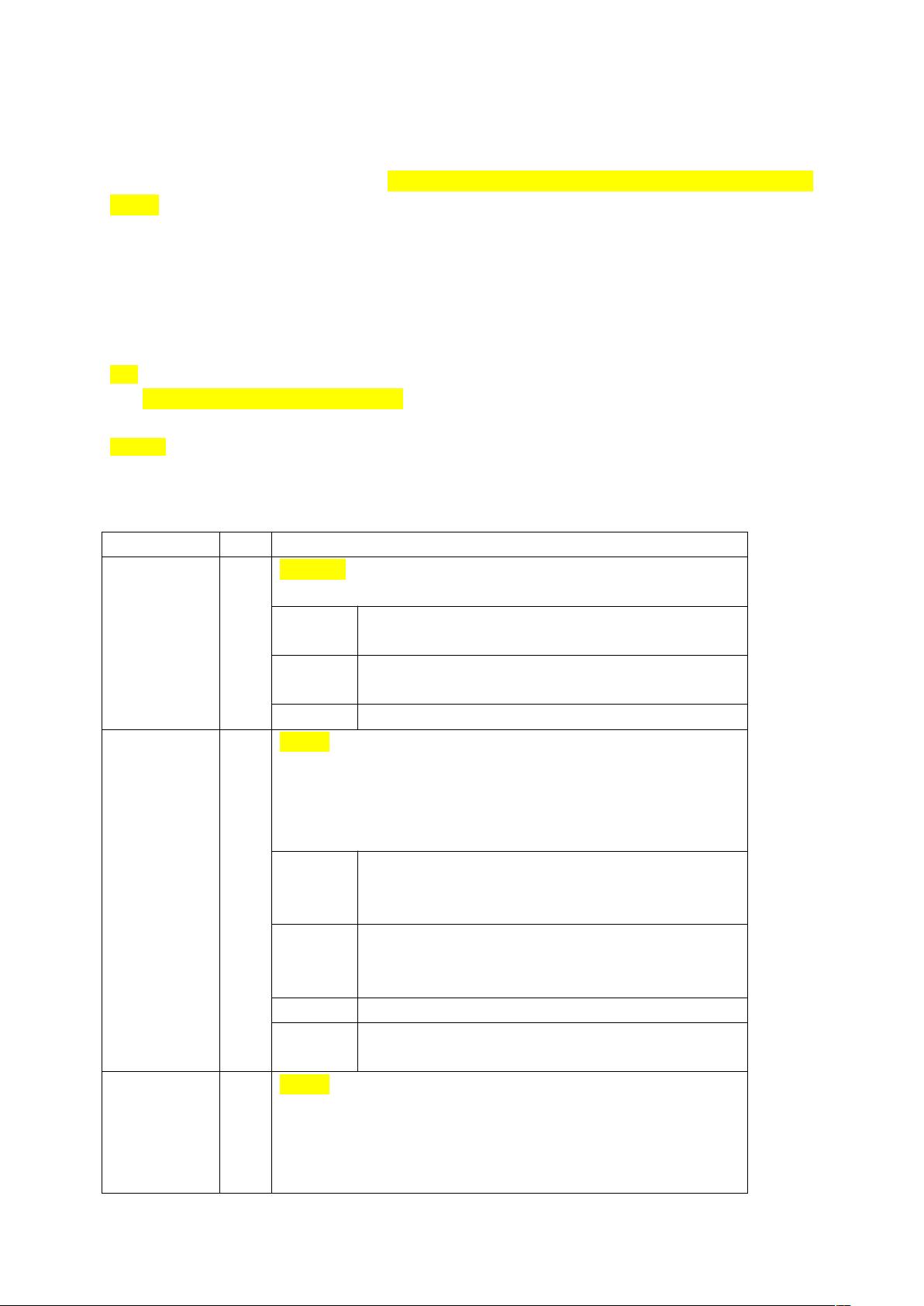

表 4-1 说明了 MPC8349E 的复位信号。4.4.2 节“复位配置字”介绍了还作为复位配置信号的信号。

表 4-1 系统控制信号——详细信号说明

信号

I/O

说明

/PORESET I

上电复位。该信号有效时启动上电复位流,初始化设备,配置设

备的各种属性,包括它的时钟模式。

状态含义 有效——外部代理触发了一个上电复位序列。

无效——指示无上电复位。

时序 关于该信号 的具体时序信息见 MPC8349E

硬件规

范

。

复位状态 始终输入。

/HDRESET I/O

硬复位。使设备终止所有当前内部和外部事务,并将大部分寄存

器设置为它们的缺省值。/HRESET 可以完全与所有其他信号异

步有效。设备不在硬复位状态时,才能检测到外部的硬复位请

求。在/HRESET 有效期间,/SRESET 有效。/HRESET 是一个漏

极开路信号。

状态含义 有效——外部代理或内部硬件触发了一个硬复位序

列。内部硬件一直驱动/HRESET,直到序列完成。

无效——指示无硬复位。

时序 有效——可以随时出现,异步于任何时钟。

无效——必须有效(保持)至少 32 个 CLKIN(PCI

主机模式)或 PCI_CLK(PCI 代理模式)个周期。

要求 这是一个漏极开路信号,需要一个外部上拉电阻。

复位状态 输出,在上电和硬复位流期间驱动低电平。复位流

完成后为高阻。

/SRESET I/O

软复位。使设备终止所有当前内部事务,将大部分寄存器设置为

它们的缺省值,并让 e300c1 核进入复位状态。I/O 信号的功能和

方向,以及存贮器控制器操作不受/SRESET 的影响。/SRESET 可

以完全与所有其他信号异步有效。设备不在硬复位或软复位状态

时才能检测到外部软复位请求。/SRESET 是一个漏极开路信号。

1

状态含义 有效——外部代理或内部硬件触发了一个软复位序

列。内部硬件一直驱动/SRESET,直到序列完成。

时序 有效——可以随时出现,异步于任何时钟。

无效——必须有效(保持)至少 32 个 CLKIN(PCI

主机模式)或 PCI_CLK(PCI 代理模式)个周期。

要求 这是一个漏极开路信号,需要外部一个上拉电阻。

复位状态 输出,在上电和硬复位流期间驱动为低电平。复位

流完成后为高阻。

CFG_RESET_

SOURCE[0:2]

I

复位配置字源选择。这些复位配置输入信号位于这样一些设备引

脚上,当设备未处于复位状态时,这些引脚具有其他功能。在/

PORESET 有效期间对这些输入信号进行采样,以确定从哪一个

接口装入复位控制字。

状态含义 详细说明见 4.4.1.1 节“复位控制字源”

时序 在/PORESET 有效期间、提供的时钟稳定之后( /

PORESET 流 )对 这 些输 入 信号 进 行采 样, 一 旦 /

HRESET 有效,就必须由外部电阻将其拉高或拉

低。

要求 在/POREST 和/HREEST 流期间,所有连接到这些信

号的其他信号驱动器必须为高阻状态。关于用于拉

高或拉低复位配置信号的合适的电阻值见 MPC8349E

硬件规范

。

复位状态 在上电和硬复位流期间为输入信号,在复位流完成

后为功能信号。

CFG_CLKIN_

DIV

I

时钟分配选择。该复位配置输入信号位于这样一个设备引脚上,

当设备未处于复位状态时,该引脚具有其他功能。在/PORESET

有效期间对该输入信号进行采样,以确定 CLKIN 是否为倍频

(除以 2)。

状态含义 见 4.4.1.2 节“时钟分配”

时序 在/PORESET 有效期间、提供的时钟稳定之后( /

PORESET 流 )对 这 些输 入 信号 进 行采 样, 一 旦 /

HRESET 有效,就必须由外部电阻将其拉高或拉

低。

要求 在/POREST 和/HRESET 流期间,所有连接到这些信

号的其他信号驱动器必须为高阻状态。关于用于拉

高或拉低复位配置信号的合适的电阻值见 MPC8349E

硬件规范

。

复位状态 在上电和硬复位流期间驱动为输入信号,在复位流

完成后为功能信号。

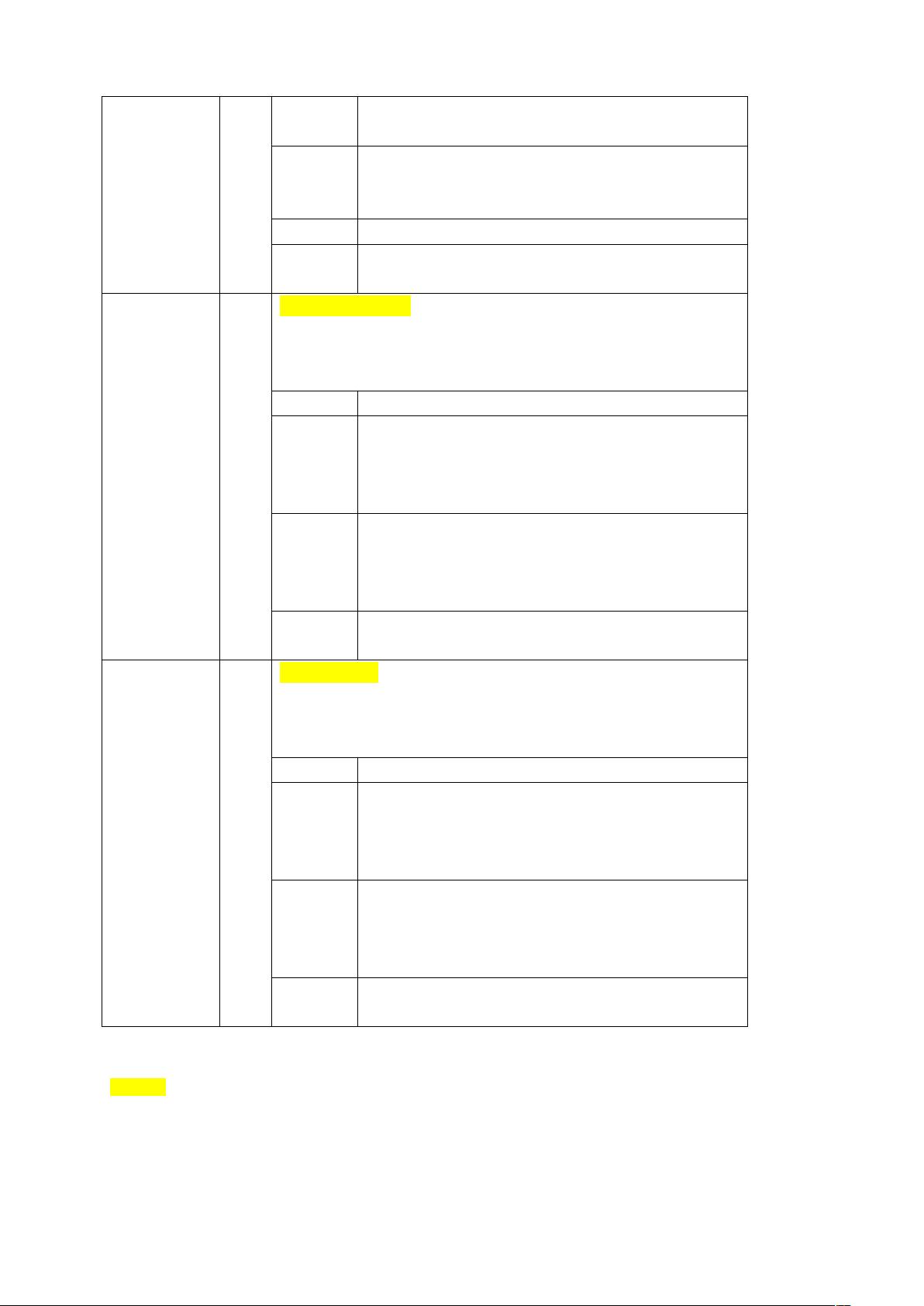

4.2.2 时钟信号

表 4-2 说明了 MPC8349E 的外部时钟信号。注意,某些信号对设备内的某些部件来说是特定的 ,

虽然 4.5 节“时钟同步”介绍了它们的某些功能,但分别在各章中对它们进行了详细定义。

表 4-2 时钟信号——详细信号说明

2

信号

I/O

说明

/CLKIN I

系统时钟。若 MPC8349E 为 PCI 主机设备,则 CLKIN 就是它的

主输入时钟。CLKIN 直接馈送给 PCI 输出时钟分配器,还作为

无时滞外部 PCI 时钟通路的信号驱动输出。若 MPC8349E 为 PCI

代理设备,则应将该信号连到 GND。

时序 有 效 / 无 效 — — 关 于 该 信 号 的 具 体 时 序 信 息 见

MPC8349E

硬件规范

。

要求 在 PCI 代理模式时应连到低

复位状态 始终输入。

PCI_CLK/

PCI_SYNC_I

N

I

PCI 时钟/PCI 同步时钟(PCI_CLK/PCI_SYNC_IN)。 当设备处

于 PCI 代理模式时,PCI_CLK 就是到该设备的主时钟输入。当

设 备 处 于 PCI 主 机 模 式 时 , 将 PCI_SYNC_IN 连 接 到 外 部

PCI_SYNC_OUT。

时序 有 效 / 无 效 — — 关 于 该 信 号 的 具 体 时 序 信 息 见

MPC8349E

硬件规范

。

复位状态 始终输入。

PCI_SYNC_O

UT

O

参考 PCI 输出同步时钟(PCI_SYNC_OUT)。当 MPC8349E 为

PCI 主 机 设 备 时 , 为 消 除 外 部 PCI 时 钟 通 路 的 时 滞 , 将

PCI_SYNC_OUT 连 接 到 外 部 的 PCI_SYNC_IN 信

号。PCI_SYNC_OUT 的频率与 CLKIN 或 CLKIN/2 相同,它与复

位 时 CFG_CLKIN_DIV 的 状 态 有 关 。 更 多 信 息 见 4.4.1.2 节

“CLKIN 分配”。当 MPC8349E 为 PCI 主机设备时,一般不使用该

信号。

时序 有 效 / 无 效 — — 关 于 该 信 号 的 具 体 时 序 信 息 见

MPC8349E

硬件规范

。

复位状态 始终输出,在 PCI 主机模式时触发。

PCI_CLK_OU

T[0:7]

O

PCI 输出时钟集。当 MPC8349E 为 PCI 主机设备时,它提供八路

独立的时钟输出信号,馈送给 PCI 代理设备。

时序 有 效 / 无 效 — — 关 于 该 信 号 的 具 体 时 序 信 息 见

MPC8349E

硬件规范

。

复位状态 始终输出。在上电复位期间和之后为高阻。由内存

映射寄存器启用。

复位状态 在上电和硬复位流期间驱动为输入信号,在复位流

完成后为功能信号。

4.3 功能说明

本节介绍复位设备的各种方法、上电复位配置和设备的时钟同步。

4.3.1 复位操作

设备有数个到复位逻辑的输入:

上电复位(/PORESET)

外部硬复位(/HRESET)

外部软复位(/SRESET)

软件看门狗复位

3

系统总线监控器复位

检查停止(checkstop)复位

JTAG 复位

软件硬复位

所有这些复位源都被馈送到复位控制器,并根据复位源的不同采取不同的行动。4.6.1.3 节“复

位状态寄存器(RSR)”中介绍的复位状态寄存器指示引起复位的最后的复位源。

4.3.1.1 复位原因

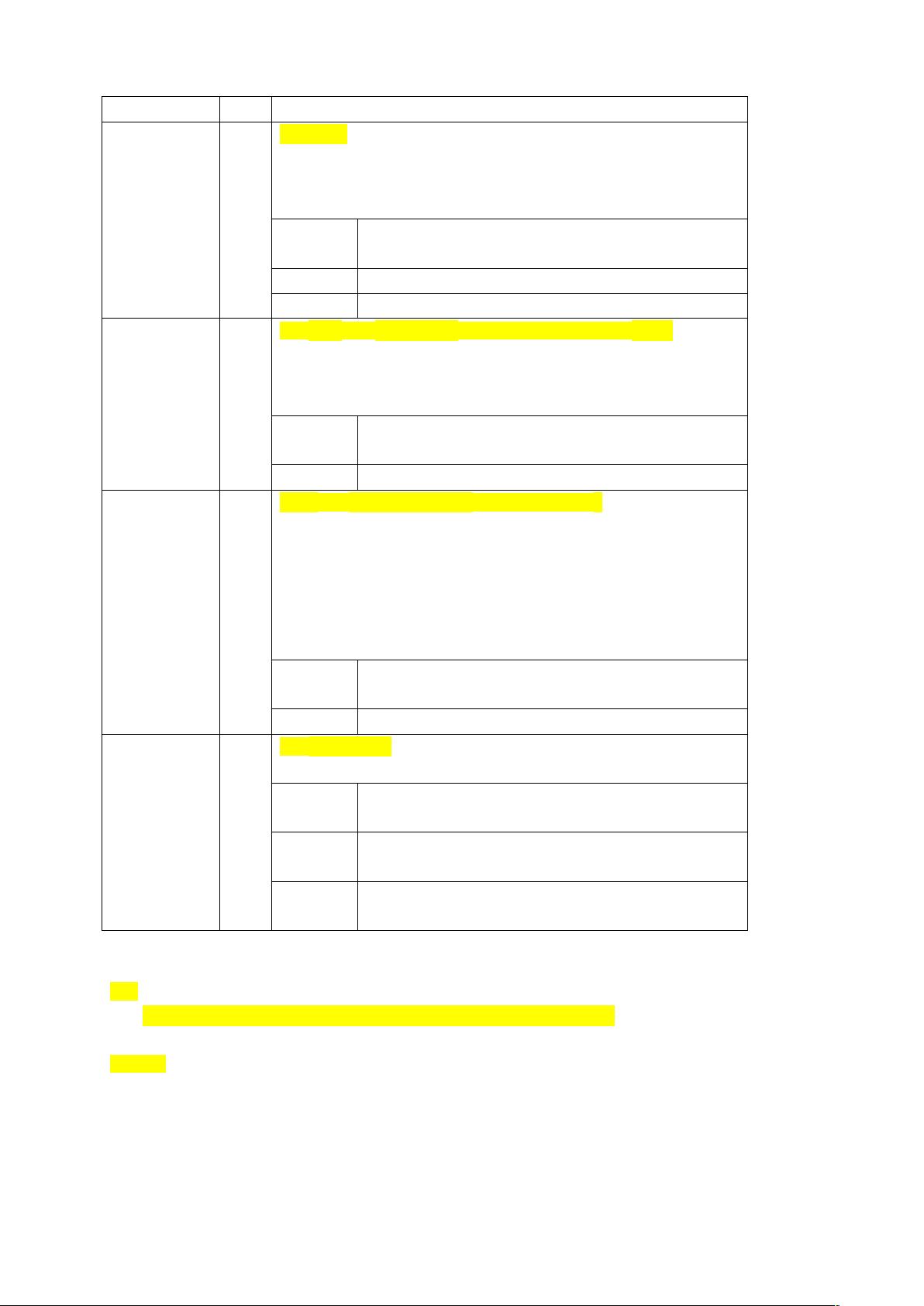

表 4-3 介绍了复位原因。

表 4-3 复位原因

名称 说明

上 电 复 位 ( /

PORESET)

输入信号。该信号有效时启动上电复位流,它复位所有的设

备并配置设备的各种属性,包括其时钟模式。

硬复位(/HRESET) 这是一个双向 I/O 信号。只有在设备未宣告硬复位但出现该

信号时,设备才能检测到外部/RESET 有效。在/HDRESET 有

效期间,/SRESET 有效。/HDRESET 是一个漏极开路信号。

软复位(/SRESET) 双向 I/O 信号。只有在设备未宣告硬或软复位但出现该信号

时,设备才能检测到外部有效的/SRESET。/SRESET 是一个

漏极开路信号。

软件看门狗复位 在设备的看门狗计数值到零以后,发出软件看门狗复位。然

后允许的软件看门狗事件产生内部硬复位序列。

系统总线监控器复位 在设备的 CSB 总线监控器到达超时状态时,总线复位有效。

然后允许的总线监控器事件产生内部硬复位序列。

检查停止复位 如 果 核 进 入 检 查 停 止 状 态 , 且 允 许 检 查 停 止 复 位

(RMR[CSRE]=1),则检查停止复位有效。然后允许的检

查停止事件产生内部硬复位序列。

JTAG 复位 当 JTAG 逻辑宣告 JTAG 软复位信号有效时,产生内部软复位

序列。

软件硬复位 写入内存映射寄存器(RCR)可以初始化硬复位序列。

软件软复位 写入内存映射寄存器(RCR)可以初始化软复位序列。

4.3.1.2 复位操作

复位控制逻辑确定复位的原因,必要时对其进行同步,并复位适当的内部硬件。每个复位流对

设备有不同的影响:

上电复位的影响最大,它复位整个设备,包括时钟逻辑和错误捕获寄存器。

硬复位复位整个设备,但不包括时钟逻辑和错误捕获寄存器。

软复位则初始化内部逻辑,但保持系统的配置。

所有复位类型都产生到 e300c1 核的复位。/PORESET、/HRESET 和/SRESET 对给定应用的影

响是核将 MSR[IP]的值复位为复位寄存器字高端的 BMS 字段中的值。参见 4.4.2.12 节“引导内存空

间(BMS)”。

存贮器控制器、系统保护逻辑、中断控制器和 I/O 信号仅在硬复位时初始化。软复位初始化内

部逻辑,但保持系统的配置。外部/SRESET 有效向核和其余的设备产生硬复位。表 4-4 标识了每个

4

复位源的复位操作。

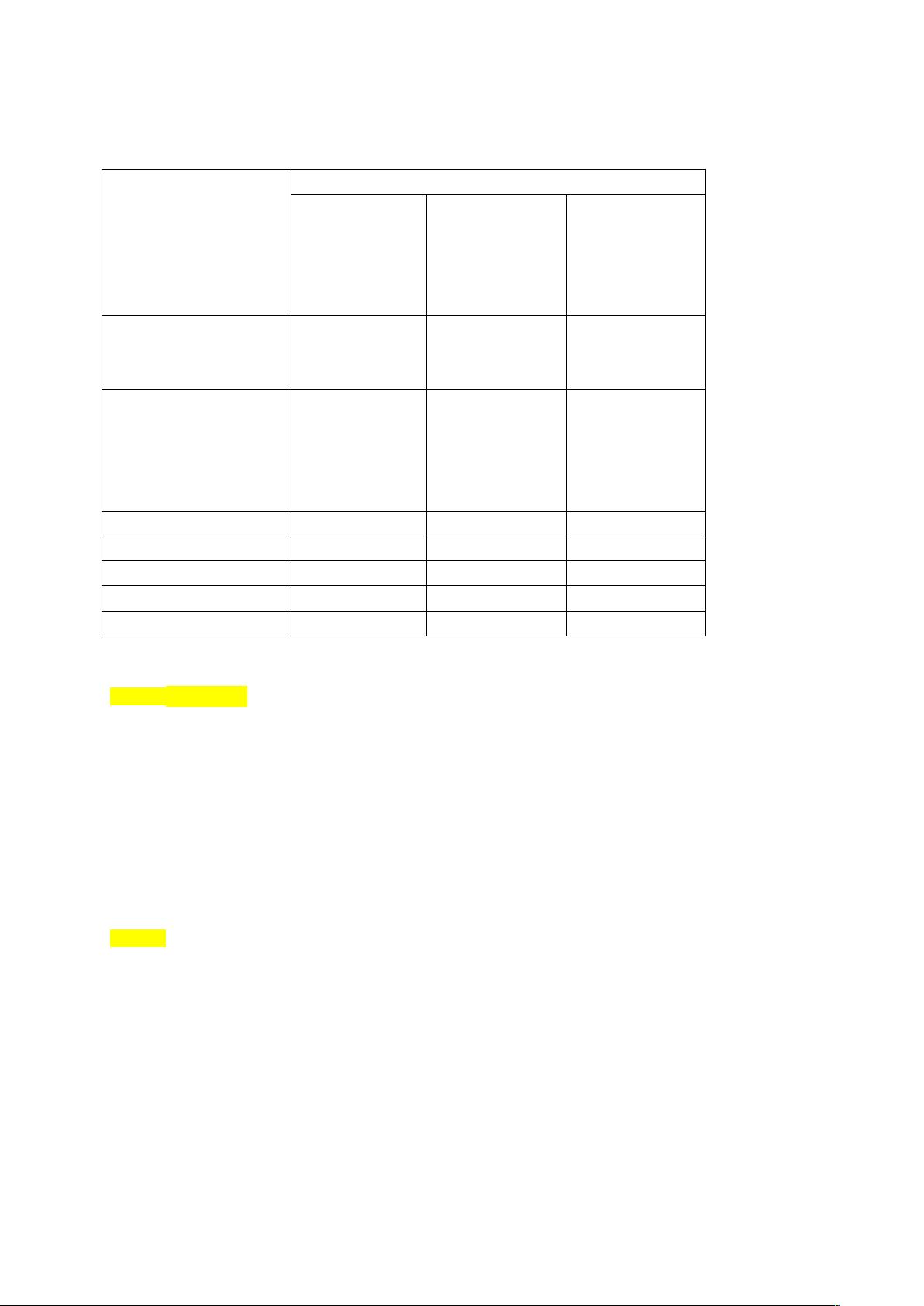

表 4-4 复位操作

动作 复位源

上电复位 外部硬复位

软件看门狗

总线监控器

检查停止

软件硬复位

JTAG 复位

外部软复位

复位:

PLL 、时钟、RTC 单元

和错误捕获寄存器

是 否 否

复位:

DDR 、 LBC 、 I/O 复 用

器、GTM、PIT、GPIO

、系统配置和本地存取

窗口

是 是 否

复位其他内部逻辑 是 是 是

复位装入的配置字 是 是 否

/HRESET 驱动 是 是 否

/SRESET 驱动 是 是 是

到 e300c1 核的硬复位 是 是 是

4.3.2 上电复位流

/PORESET 外部信号有效启动上电复位流。在设备的外部供电稳定之后,应保持 /PORESET 外

部有效至少 32 个输入时钟周期。在/PORESET 无效之后,设备立即开始配置过程。设备在整个上

电复位 过 程 期间,包 括 配 置期间, 宣告 /HRESET 和/SRESET 有效。配 置 时 间根 据 配 置源 和

CLKIN(PCI 主机模式)或 PCI_CLK(PCI 代理模式)频率的不同而变化。首先对复位配置输入进

行采样,确定配置源和输入时钟的分配模式。然后设备开始装入复位配置字。系统 PLL 根据复位配

置字低端中的时钟模式值开始锁定。当系统 PLL 锁时序,时钟单元开始在设备中分配时钟信号。在

这 个 阶 段 , e300c1 核 的 PLL 开 始 锁 定 。 当 它 被 锁 定 并 完 成 了 复 位 配 置 字 的 装 入时 , 释 放 /

HRESET,在 4 个时钟之后释放/SRESET。

4.3.2.1 详细上电复位流程

MPC8349E 的详细上电复位(POR)流程如下:

1. 加电,满足 MPC8349E

硬件规范

的要求。

2. 系统宣告/PORESET(以及可选的/HRESET)和/TRST 有效,让所有寄存器初始化到它们的缺

省状态,让大部分 I/O 驱动器释放为高阻(某些时钟、时钟允许和系统控制信号仍保持有效)

状态。

3. 系统施加稳定的 CLKIN(PCI 主机模式)或 PCI_CLK(PCI 代理模式)信号和稳定的复位配置

输入信号(CFG_RESET_SOURCE 和 CFG_CLKIN_DIV)。

4. 在至少 32 个稳定的 CLKIN(PCI 主机模式)或 PCI_CLK(PCI 代理模式)时钟周期之后,系

统将/PORESET 置为无效。

5. 设备对复位配置输入信号进行采样,确时时钟分配和复位配置源。

5

剩余37页未读,继续阅读

资源评论

DJYOS都江堰操作系统

- 粉丝: 412

- 资源: 7

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功