1646 IEEE TRANSACTIONS ON INSTRUMENTATION AND MEASUREMENT, VOL. 54, NO. 4, AUGUST 2005

Modeling of Switched-Capacitor Delta–Sigma

Modulators in SIMULINK

Hashem Zare-Hoseini, Izzet Kale, and Omid Shoaei, Member, IEEE

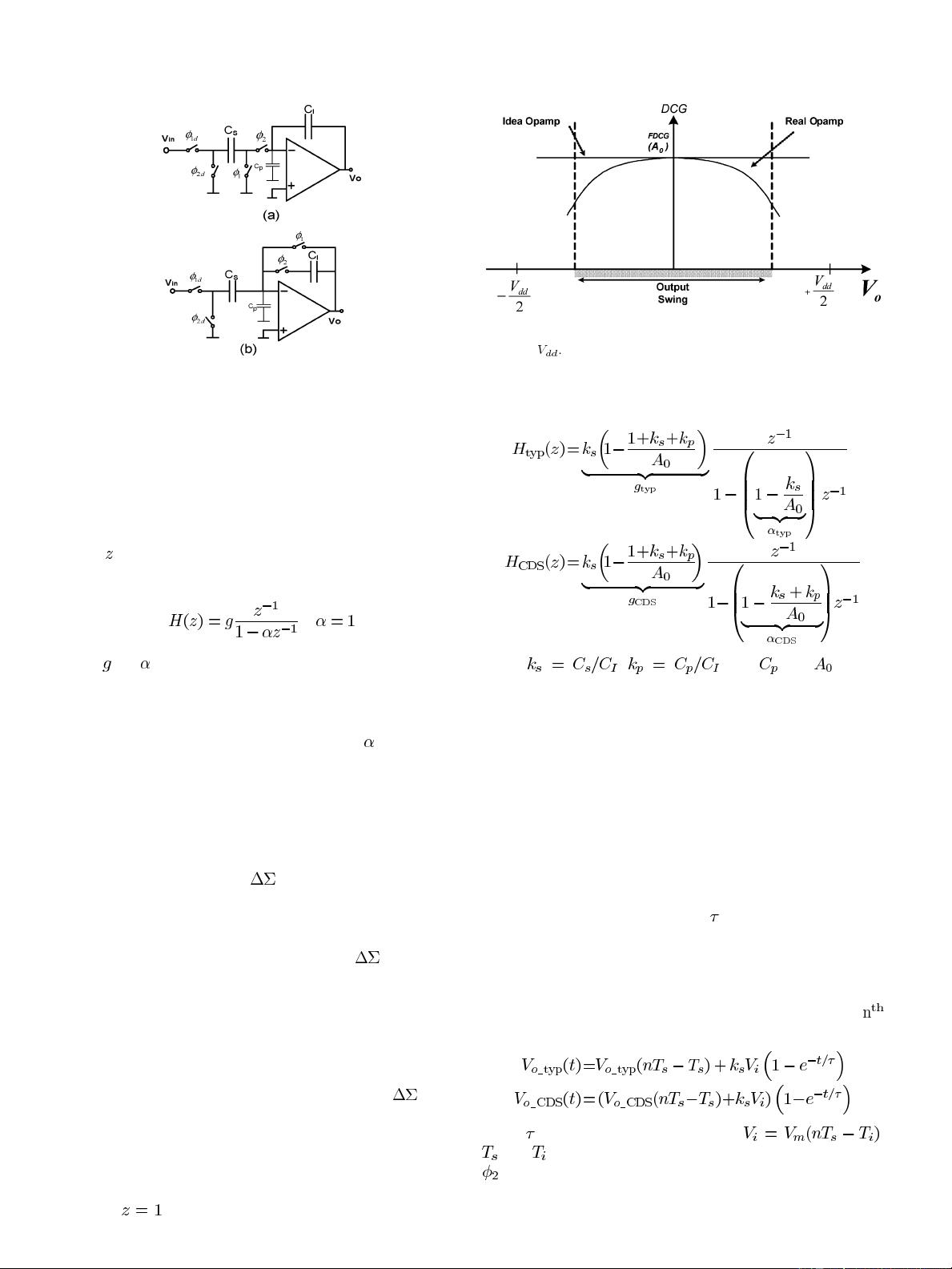

Abstract—Precise behavioral modeling of switched-capacitor

16

modulators is presented. Considering noise (switches’ and

op-amps’ thermal noise), clock jitter, nonidealities of integrators

and op-amps including finite dc-gain (DCG) and unity gain band-

width, slew-limiting, DCG nonlinearities and the input parasitic

capacitance, quantizer hysteresis, switches’ clock-feedthrough,

and charge injection, exhaustive behavioral simulations that are

close models of the transistor-level ones can be performed. The

DCG nonlinearity of the integrators, which is not considered in

many

16

modulators’ modeling attempts, is analyzed, estimated,

and modeled. It is shown that neglecting this parameter would

lead to a significant underestimation of the modulators’ behavior

and increase the noise floor as well as the harmonic distortion

at the output of the modulator. Evaluation and validation of the

models were done via behavioral and transistor-level simulations

for a second-order modulator using SIMULINK and HSPICE

with a generic 0.35-

m CMOS technology. The effects of the

nonidealities and nonlinearities are clearly seen when compared

to the ideal modulator in the behavioral and actual modulator in

the circuit-level environment.

Index Terms—Charge injection, clock feedthrough, correlated

double sampling, delta–sigma modulators, hysteresis, nonideality,

nonlinearity, SIMULINK, switched capacitor.

I. INTRODUCTION

A

MONG the oversampling converters, ones have

achieved the most attraction recently in high-resolution

applications due to their noise shaping behavior that leads

them to inherent superior linearity, simple realization, and low

sensitivity to circuit imperfections [1]. Such converters reduce

the need for complex analog circuit implementation and, due to

their oversampling nature, act as the most suitable architectures

for accurate low to moderately high frequency applications.

modulators can be realized in either the continuous-time

(CT) or switched-capacitor (SC) approach. While CT modula-

tors have the advantages of lower power consumption, higher

speed, and intrinsic anti-aliasing filtering, they suffer from the

difficulty of designing, sensitivity to clock jitter, and also excess

loop delay [2]. As far as the implementation technique is con-

cerned, SC modulators are preferred to CT modulators because

they can be more efficiently realized in standard CMOS tech-

nology [1], [3]. Moreover, they provide a highly controllable

Manuscript received June 15, 2004; revised April 15, 2005.

H. Zare-Hoseini and I. Kale are with the Applied DSP and VLSI Research

Group, Department of Electronic Systems, University of Westminster, London,

W1W 6UW, U.K. (e-mail: h.zhoseini@wmin.ac.uk)

O. Shoaei is with the IC Design Laboratory, Electrical and Computer Engi-

neering Department, University of Tehran, Tehran, Iran.

Digital Object Identifier 10.1109/TIM.2005.851085

design as well as being more robust to clock jitter and feed-

back delay problems. In this paper, the SC

modulators are

considered.

Although

modulators have relatively straightforward

realizations, the appropriate architecture selection, including

single loop or MASH, loop filter type, order and coefficients,

and the number of bits of the quantizer, would be a difficult

task. Also, the requirements of the building blocks such as

integrators’ bandwidth, dc-gain (DCG), slew rate and output

swings, the quantizer threshold, the digital-to-analog con-

verter (DAC), the switches, and the clock and power supply

accuracy cannot be easily estimated. Several techniques have

been used for time-domain analysis of these modulators listed

and discussed briefly in [3], such as SPICE, SWITCAP, and

table-lookup models. For instance, the SPICE simulations are

precise, but they take extremely long times especially for very

high-resolution narrow-band modulators because of both long

period cycles and the high accuracy needed. Hence, choosing

the optimized architecture and estimating the requirements of

building blocks is a very time-consuming procedure in tran-

sistor-level design and simulation (SPICE). There is a need for

a time-efficient and accurate simulation environment. To this

effect, the user friendly, versatile SIMULINK tool was chosen

to develop detailed models of the modulators’ building blocks.

The popular SIMULINK simulator proved to be an excellent

time-efficient candidate for this initial task.

In this paper, detailed analytical models of the basic building

blocks (integrators and op-amps) and also the nonidealities of

a typical modulator are presented, followed by SIMULINK

models of them. Most previous

modulator models have

not considered the effect of DCG nonlinearity in integrators,

leading to a significant underestimation of the modulators’ be-

havior and harmonic distortion. In this paper, this is analyzed,

estimated, and modeled in SIMULINK, as well as other blocks

of a typical

modulator. Moreover, several behavioral and

transistor-level simulations were performed in SIMULINK

and HSPICE using a generic 0.35-

m CMOS technology to

validate the analyses and models. Since in the first stage of very

high-resolution modulators correlated-double-sampled (CDS)

integrators are routinely used to attenuate the effect of offset

and flicker noise, for comparison purposes, both typical and

CDS integrators are discussed in this paper.

In Section II, the integrator characteristics such as finite

DCG, nonlinear DCG, and settling behavior are presented.

Section III presents noise contributors such as sampling and

op-amp thermal noise. Switch nonidealities are considered next

following with a discussion about clock jitter. In Section VI, a

brief review of quantizer nonidealities are discussed. Then the

0018-9456/$20.00 © 2005 IEEE

Authorized licensed use limited to: Harbin Institute of Technology. Downloaded on June 28,2010 at 08:50:00 UTC from IEEE Xplore. Restrictions apply.

hahahahaaaaaaaaaa2017-11-25应该对我有帮助

hahahahaaaaaaaaaa2017-11-25应该对我有帮助 我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功