没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

DDR3 的 datasheet资料,200多页,......................................................................................................................................................................................................................................................................................................................................................................

资源推荐

资源详情

资源评论

DDR3L SDRAM

MT41K2G4 – 256 Meg x 4 x 8 banks

MT41K1G8 – 128 Meg x 8 x 8 banks

MT41K512M16 – 64 Meg x 16 x 8 banks

Description

DDR3L (1.35V) SDRAM is a low voltage version of the

DDR3 (1.5V) SDRAM. Refer to a DDR3 (1.5V) SDRAM

data sheet specifications when running in 1.5V com-

patible mode.

Features

•V

DD

= V

DDQ

= 1.35V (1.283–1.45V)

• Backward compatible to V

DD

= V

DDQ

= 1.5V ±0.075V

– Supports DDR3L devices to be backward com-

patible in 1.5V applications

• Differential bidirectional data strobe

•8n-bit prefetch architecture

• Differential clock inputs (CK, CK#)

• 8 internal banks

• Nominal and dynamic on-die termination (ODT)

for data, strobe, and mask signals

• Programmable CAS (READ) latency (CL)

• Programmable posted CAS additive latency (AL)

• Programmable CAS (WRITE) latency (CWL)

• Fixed burst length (BL) of 8 and burst chop (BC) of 4

(via the mode register set [MRS])

• Selectable BC4 or BL8 on-the-fly (OTF)

• Self refresh mode

•T

C

of 95°C

– 64ms, 8192-cycle refresh up to 85°C

– 32ms, 8192-cycle refresh at >85°C to 95°C

• Self refresh temperature (SRT)

• Automatic self refresh (ASR)

• Write leveling

• Multipurpose register

• Output driver calibration

Options Marking

• Configuration

– 2 Gig x 4 2G4

– 1 Gig x 8 1G8

– 512 Meg x 16 512M16

• FBGA package (Pb-free) – x4, x8

– 78-ball (9mm x 13.2mm) SN

• FBGA package (Pb-free) – x16

– 96-ball (9mm x 14mm) HA

• Timing – cycle time

– 1.25ns @ CL = 11 (DDR3-1600) -125

– 1.07ns @ CL = 13 (DDR3-1866) -107

• Operating temperature

– Commercial (0°C ื T

C

ื +95°C) None

– Industrial (–40°C ื T

C

ื +95°C) IT

• Revision :A

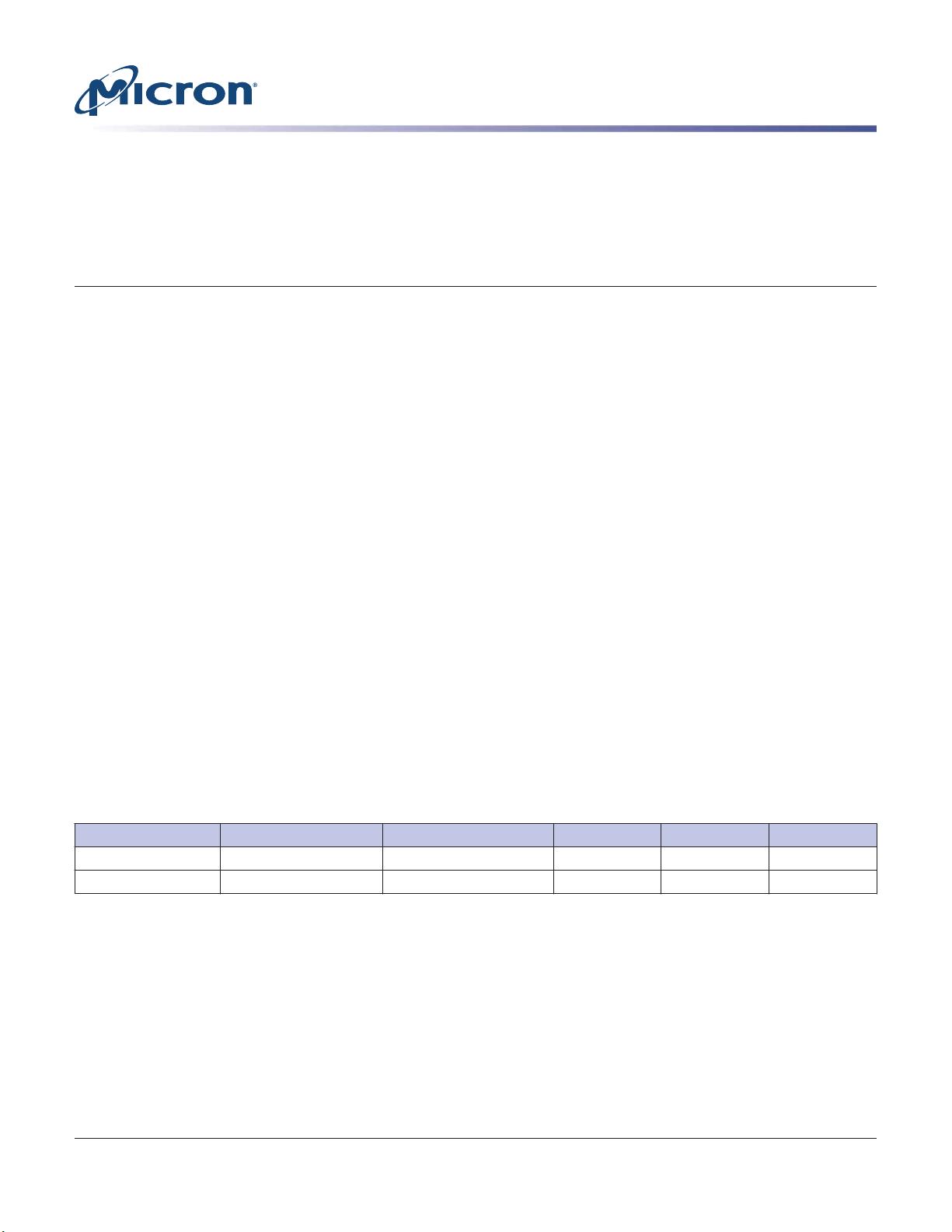

Table 1: Key Timing Parameters

Speed Grade Data Rate (MT/s) Target

t

RCD-

t

RP-CL

t

RCD (ns)

t

RP (ns) CL (ns)

-107

1

1866 13-13-13 13.91 13.91 13.91

-125 1600 11-11-11 13.75 13.75 13.75

Note:

1. Backward compatible to 1600, CL = 11 (-125).

8Gb: x4, x8, x16 DDR3L SDRAM

Description

09005aef8591dc1f

8Gb_DDR3L.pdf - Rev. D 8/17 EN

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are subject to change by Micron without notice.

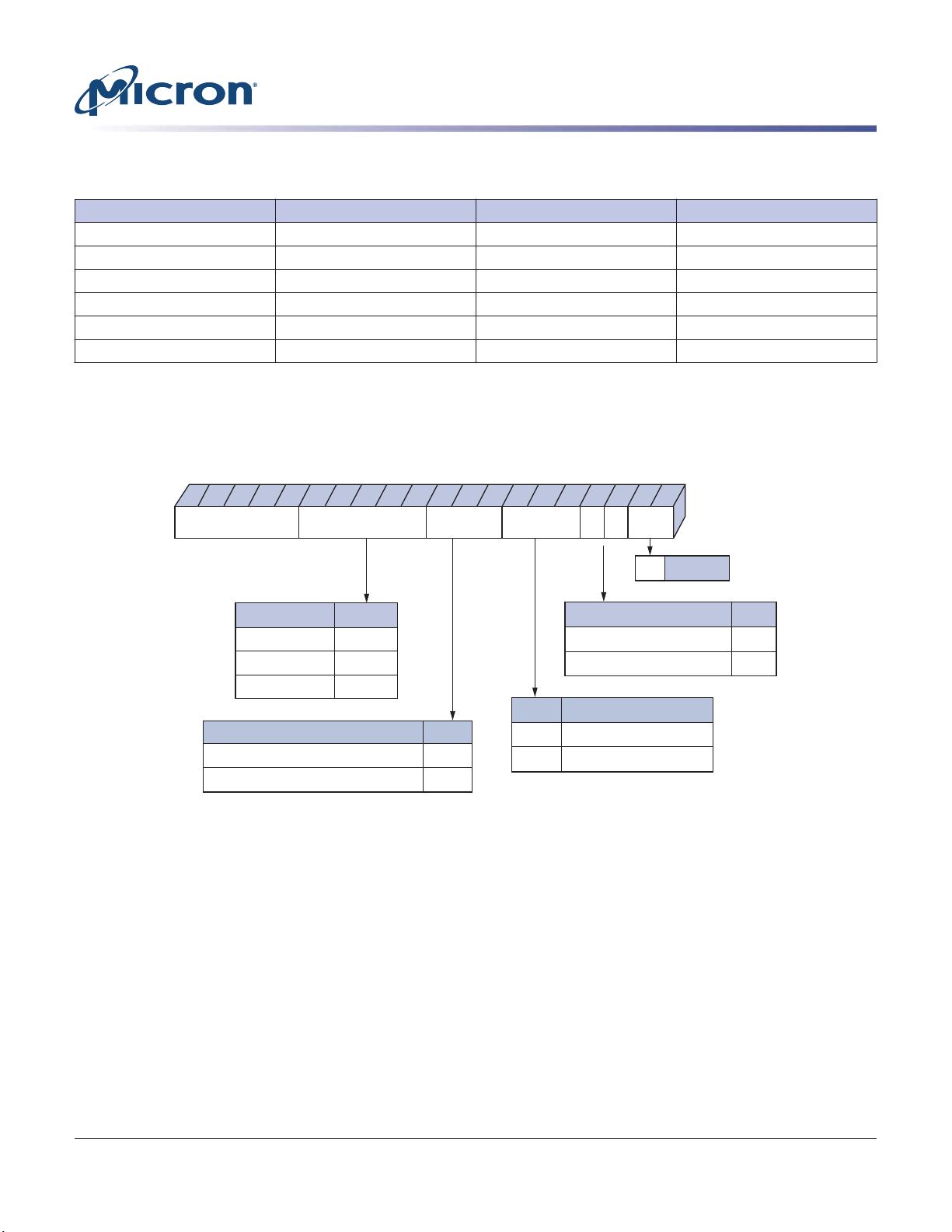

Table 2: Addressing

Parameter 2 Gig x 4 1 Gig x 8 512 Meg x 16

Configuration 256 Meg x 4 x 8 banks 128 Meg x 8 x 8 banks 64 Meg x 16 x 8 banks

Refresh count 8K 8K 8K

Row address 64K (A[15:0]) 64K (A[15:0]) 64K (A[15:0])

Bank address 8 (BA[2:0]) 8 (BA[2:0]) 8 (BA[2:0])

Column address 4K (A[13,11, 9:0]) 2K (A[11,9:0]) 1K (A[9:0])

Page size 2KB 2KB 2KB

Figure 1: DDR3L Part Numbers

Example Part Number: MT41K1G8SN-125:A

Configuration

2 Gig x 4

1 Gig x 8

512 Meg x 16

2G4

1G8

512M16

-

Configuration

MT41K

Package Speed

Revision

Revision

:A

:

Commercial

Industrial temperature

^

None

IT

Package

96-ball 9.0mm x 14.0mm FBGA

Mark

HA

78-ball 9.0mm x 13.2mm FBGA

SN

Speed Grade

t

CK = 1.07ns, CL = 13

t

CK = 1.25ns, CL = 11

-107

-125

Temperature

Note:

1. Not all options listed can be combined to define an offered product. Use the part catalog search on

http://www.micron.com for available offerings.

FBGA Part Marking Decoder

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the

part number. For a quick conversion of an FBGA code, see the FBGA Part Marking Decoder on Micron’s Web site:

http://www.micron.com.

8Gb: x4, x8, x16 DDR3L SDRAM

Description

09005aef8591dc1f

8Gb_DDR3L.pdf - Rev. D 8/17 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

Contents

State Diagram ................................................................................................................................................ 11

Functional Description ................................................................................................................................... 12

Industrial Temperature ............................................................................................................................... 12

General Notes ............................................................................................................................................ 12

Functional Block Diagrams ............................................................................................................................. 14

Ball Assignments and Descriptions ................................................................................................................. 16

Package Dimensions ....................................................................................................................................... 22

Electrical Specifications .................................................................................................................................. 24

Absolute Ratings ......................................................................................................................................... 24

Input/Output Capacitance .......................................................................................................................... 25

Thermal Characteristics .................................................................................................................................. 26

Electrical Specifications – I

DD

Specifications and Conditions ........................................................................... 27

Electrical Characteristics – 1.35V/1.5V I

DD

Specifications ................................................................................. 38

Electrical Specifications – DC and AC .............................................................................................................. 39

DC Operating Conditions ........................................................................................................................... 39

Input Operating Conditions ........................................................................................................................ 40

DDR3L 1.35V AC Overshoot/Undershoot Specification ................................................................................ 44

DDR3L 1.35V Slew Rate Definitions for Single-Ended Input Signals .............................................................. 47

DDR3L 1.35V Slew Rate Definitions for Differential Input Signals ................................................................. 49

ODT Characteristics ....................................................................................................................................... 50

1.35V ODT Resistors ................................................................................................................................... 51

ODT Sensitivity .......................................................................................................................................... 52

ODT Timing Definitions ............................................................................................................................. 52

Output Driver Impedance ............................................................................................................................... 56

34 Ohm Output Driver Impedance .............................................................................................................. 57

DDR3L 34 Ohm Driver ................................................................................................................................ 58

DDR3L 34 Ohm Output Driver Sensitivity .................................................................................................... 59

DDR3L Alternative 40 Ohm Driver ............................................................................................................... 60

DDR3L 40 Ohm Output Driver Sensitivity .................................................................................................... 60

Output Characteristics and Operating Conditions ............................................................................................ 62

Reference Output Load ............................................................................................................................... 65

Slew Rate Definitions for Single-Ended Output Signals ................................................................................. 65

Slew Rate Definitions for Differential Output Signals .................................................................................... 67

Speed Bin Tables ............................................................................................................................................ 68

Electrical Characteristics and AC Operating Conditions ................................................................................... 72

Command and Address Setup, Hold, and Derating ........................................................................................... 90

Data Setup, Hold, and Derating ....................................................................................................................... 97

Commands – Truth Tables ............................................................................................................................. 105

Commands ................................................................................................................................................... 108

DESELECT ................................................................................................................................................ 108

NO OPERATION ........................................................................................................................................ 108

ZQ CALIBRATION LONG ........................................................................................................................... 108

ZQ CALIBRATION SHORT .......................................................................................................................... 108

ACTIVATE ................................................................................................................................................. 108

READ ........................................................................................................................................................ 108

WRITE ...................................................................................................................................................... 109

PRECHARGE ............................................................................................................................................. 110

REFRESH .................................................................................................................................................. 110

SELF REFRESH .......................................................................................................................................... 111

DLL Disable Mode ..................................................................................................................................... 112

8Gb: x4, x8, x16 DDR3L SDRAM

Description

09005aef8591dc1f

8Gb_DDR3L.pdf - Rev. D 8/17 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

Input Clock Frequency Change ...................................................................................................................... 116

Write Leveling ............................................................................................................................................... 118

Write Leveling Procedure ........................................................................................................................... 120

Write Leveling Mode Exit Procedure ........................................................................................................... 122

Initialization ................................................................................................................................................. 123

Voltage Initialization / Change ....................................................................................................................... 125

V

DD

Voltage Switching ............................................................................................................................... 126

Mode Registers .............................................................................................................................................. 127

Mode Register 0 (MR0) ................................................................................................................................... 128

Burst Length ............................................................................................................................................. 128

Burst Type ................................................................................................................................................. 129

DLL RESET ................................................................................................................................................ 130

Write Recovery .......................................................................................................................................... 130

Precharge Power-Down (Precharge PD) ...................................................................................................... 131

CAS Latency (CL) ....................................................................................................................................... 131

Mode Register 1 (MR1) ................................................................................................................................... 132

DLL Enable/DLL Disable ........................................................................................................................... 132

Output Drive Strength ............................................................................................................................... 133

OUTPUT ENABLE/DISABLE ...................................................................................................................... 133

TDQS Enable ............................................................................................................................................. 133

On-Die Termination .................................................................................................................................. 134

WRITE LEVELING ..................................................................................................................................... 134

POSTED CAS ADDITIVE Latency ................................................................................................................ 134

Mode Register 2 (MR2) ................................................................................................................................... 135

CAS Write Latency (CWL) ........................................................................................................................... 136

AUTO SELF REFRESH (ASR) ....................................................................................................................... 136

SELF REFRESH TEMPERATURE (SRT) ........................................................................................................ 136

SRT vs. ASR ............................................................................................................................................... 137

DYNAMIC ODT ......................................................................................................................................... 137

Mode Register 3 (MR3) ................................................................................................................................... 137

MULTIPURPOSE REGISTER (MPR) ............................................................................................................ 138

MPR Functional Description ...................................................................................................................... 139

MPR Register Address Definitions and Bursting Order ................................................................................. 140

MPR Read Predefined Pattern .................................................................................................................... 145

MODE REGISTER SET (MRS) Command ........................................................................................................ 145

ZQ CALIBRATION Operation ......................................................................................................................... 146

ACTIVATE Operation ..................................................................................................................................... 147

READ Operation ............................................................................................................................................ 149

WRITE Operation .......................................................................................................................................... 160

DQ Input Timing ....................................................................................................................................... 168

PRECHARGE Operation ................................................................................................................................. 170

SELF REFRESH Operation .............................................................................................................................. 170

Extended Temperature Usage ........................................................................................................................ 172

Power-Down Mode ........................................................................................................................................ 173

RESET Operation ...........................................................................................................................................

181

On-Die Termination (ODT) ............................................................................................................................ 183

Functional Representation of ODT ............................................................................................................. 183

Nominal ODT ............................................................................................................................................ 183

Dynamic ODT ............................................................................................................................................... 185

Dynamic ODT Special Use Case ................................................................................................................. 185

Functional Description .............................................................................................................................. 185

Synchronous ODT Mode ................................................................................................................................ 191

8Gb: x4, x8, x16 DDR3L SDRAM

Description

09005aef8591dc1f

8Gb_DDR3L.pdf - Rev. D 8/17 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

ODT Latency and Posted ODT .................................................................................................................... 191

Timing Parameters .................................................................................................................................... 191

ODT Off During READs .............................................................................................................................. 194

Asynchronous ODT Mode .............................................................................................................................. 196

Synchronous to Asynchronous ODT Mode Transition (Power-Down Entry) .................................................. 198

Asynchronous to Synchronous ODT Mode Transition (Power-Down Exit) ........................................................ 200

Asynchronous to Synchronous ODT Mode Transition (Short CKE Pulse) ...................................................... 202

8Gb: x4, x8, x16 DDR3L SDRAM

Description

09005aef8591dc1f

8Gb_DDR3L.pdf - Rev. D 8/17 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

剩余203页未读,继续阅读

资源评论

页页读

- 粉丝: 664

- 资源: 6

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 金属熔化凝固及多技术下的UDF代码讲解:最强学习资料,深入探索:金属熔凝最强学习资料汇编-涵盖流动传热传质、激光移动热源技术、熔化凝固现象、宏观偏析现象解析及UDF代码精细讲解,fluent金属熔凝

- 船舶电力系统稳定性分析与仿真的Python实现及优化调度(论文复现,含可运行代码及解释)

- 基于Python的渐开线直齿轮动力学与弹流润滑耦合模型仿真及不确定性和敏感性分析

- 基于FPGA的数字电子琴-数电小系统设计【数字电子技术】(使用Vivado中的verilog语言)实验设计代码文件(全)

- 格子玻尔兹曼方法LBM在Matlab中模拟三维多孔介质流动D3Q19的实践研究,格子玻尔兹曼方法LBM在Matlab中模拟三维多孔介质流动D3Q19的实践研究,使用格子玻尔兹曼方法LBM模拟三维多孔介

- 基于COMSOL的三维离散裂隙恒压注浆模型:粘度空间衰减的宾汉姆流体随机圆盘模型研究,基于宾汉姆流体粘度空间衰减的COMSOL三维离散裂隙恒压注浆模型研究,COMSOL 三维离散裂隙注浆模型 基于粘

- 基于双闭环控制与最近电平逼近调制的MMC模块化多电平换流器仿真研究:含技术文档、Matlab-Simulink实现、直流侧11kV交流侧6.6kV电压电流稳态对称仿真分析,基于双闭环控制与最近电平逼近

- chatbox软件压缩包

- 汇川小型机H5U编程特色:伺服驱动器与IO模块配置,梯形图编程直观易懂,卷绕轴速调整与多配方处理,产能统计及数据交互功能强大 ,汇川小型机H5U编程特色:伺服驱动器与IO模块配置,梯形图编程直观易懂

- 磁悬浮轴承MATLAB建模与仿真分析:理论与实践的完美结合,磁悬浮轴承与磁悬浮仿真模型的MATLAB建模与仿真分析,磁悬浮轴承MATLAB模型&磁悬浮仿真模型 ,磁悬浮轴承; MATLAB模型; 磁悬

- 人工智能之深度学习:神经网络分类与回归任务实战资源(源码+数据集+说明)

- numpy-2.2.0-cp312-cp312-win_amd64.whl

- 微信疯传社群测试可用+修复版+免激活去授权版

- 项目实战:Qt图像拼接渐进色图层生成工具v1.0.0(预设四路拼接,多路可通过多图叠层实现)

- numpy-2.2.0-cp312-cp312-win32.whl

- 智能算法在21个工程应用中的全面实践与效能分析:统计指标导出与收敛图可视化 这个标题符合您的要求,既包含了您提供的文字中的主要信息,又简洁明了,易于理解 ,智能算法在21个工程应用中的全面实践与效能

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功