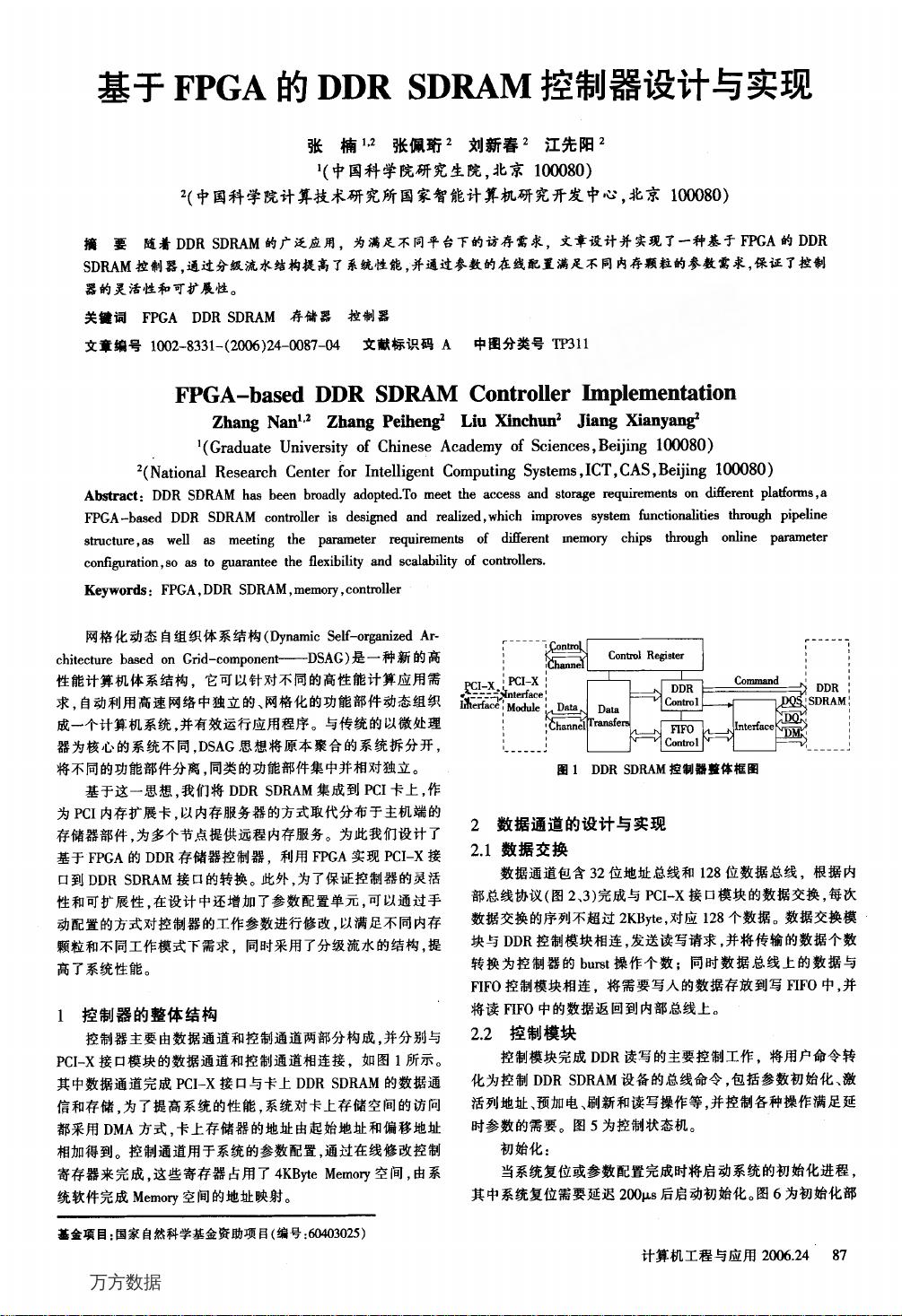

### 基于FPGA的DDR SDRAM控制器设计与实现 #### 概述 随着高性能计算和嵌入式系统对数据处理速度和容量的需求日益增长,DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory)作为高效能内存,其应用范围越来越广。然而,由于DDR SDRAM的工作机制复杂,直接在处理器平台上实现其控制器存在难度,因此,利用FPGA(Field Programmable Gate Array)设计DDR SDRAM控制器成为一种高效且灵活的解决方案。 #### 设计目标与特点 设计并实现的基于FPGA的DDR SDRAM控制器旨在满足不同平台下的内存访问需求。通过采用分级流水结构,该控制器显著提升了系统性能,同时,通过参数的在线配置,能够适应不同内存颗粒的具体参数需求,确保了控制器的灵活性和可扩展性。 #### 技术细节与创新 ##### 控制器整体结构 控制器由数据通道和控制通道组成。数据通道负责PCI-X接口与DDR SDRAM之间的数据通信和存储,采用DMA(Direct Memory Access)方式优化存储访问效率;控制通道则用于参数配置,通过修改控制寄存器实现,这些寄存器占用特定的内存空间,便于软件映射和管理。 ##### 数据通道设计与实现 数据通道采用32位地址总线和128位数据总线,支持内部总线协议,以完成与PCI-X接口模块的数据交换。单次数据交换限制在2KByte以内,以确保数据传输的可控性和稳定性。数据交换模块与DDR控制模块紧密相连,负责发送读写请求,并将数据传输量转换为控制器的突发(Burst)操作次数,以优化内存访问模式。同时,数据总线上的数据与FIFO(First In First Out)控制模块相连接,确保数据的正确顺序和完整性。 ##### 控制通道与参数配置 控制通道是实现控制器灵活性的关键,它允许用户在线修改控制器的工作参数,以适应不同类型的DDR SDRAM芯片和工作模式。通过手动配置或软件更新,可以调整诸如时序、电压、频率等参数,这不仅增强了控制器的适应性,也简化了硬件设计的复杂度。 ##### 分级流水结构 为提升系统性能,设计中采用了分级流水结构。这种结构将复杂的内存访问操作分解为一系列简单步骤,每个步骤可以在不同的硬件模块中并行执行,从而减少了整体延迟,加快了数据处理速度。同时,流水线结构还能有效减少资源冲突,提高资源利用率。 #### 总结与展望 基于FPGA的DDR SDRAM控制器设计,通过结合高级硬件架构与灵活的参数配置机制,为高性能计算和嵌入式系统提供了高效、灵活且可扩展的内存解决方案。未来的研究方向可能包括进一步优化流水线结构,提高数据吞吐量,以及探索更先进的参数配置策略,以应对不断发展的内存技术和计算需求。

剩余6页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于微信小程序校园外卖系统-数据库课程设计全部资料+详细文档+高分项目.zip

- 基于图书馆系统,swing界面,基本数据库操作全部资料+详细文档+高分项目.zip

- 基于图书管理系统(数据库课程设计,原生PHP+Bootstrap+MySQL)全部资料+详细文档+高分项目.zip

- 基于学生信息管理系统 JAVA Mysql 数据库课程设计 简单界面全部资料+详细文档+高分项目.zip

- 基于学生教务信息管理系统:SQL SERVER数据库课程设计全部资料+详细文档+高分项目.zip

- 2024中国数字化年会演讲(脱敏)PPT汇总(9份).zip

- Java+Swing+Mysql实现图书管理系统.zip

- 充电桩通讯协议 CAN标准帧

- 2024年数据治理产业图谱3.0(高清大图).pdf

- Java+Swing+Mysql实现学生信息管理系统.zip

- 吊篮式油菜移栽机sw16可编辑全套技术资料100%好用.zip

- C3传奇3引擎+版本全套 免费分享

- 123swwdqdsqwdqd

- 钢筋滚丝机sw18可编辑全套技术资料100%好用.zip

- 滚筒线体及托盘下料设备sw17全套技术资料100%好用.zip

- 基于java+ssm+mysql的鲜花商城系统开题报告.doc

信息提交成功

信息提交成功