A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

PIQY0 LA6881P

1.0

Cover Page

Custom

1 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

PIQY0 LA6881P

1.0

Cover Page

Custom

1 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

PIQY0 LA6881P

1.0

Cover Page

Custom

1 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

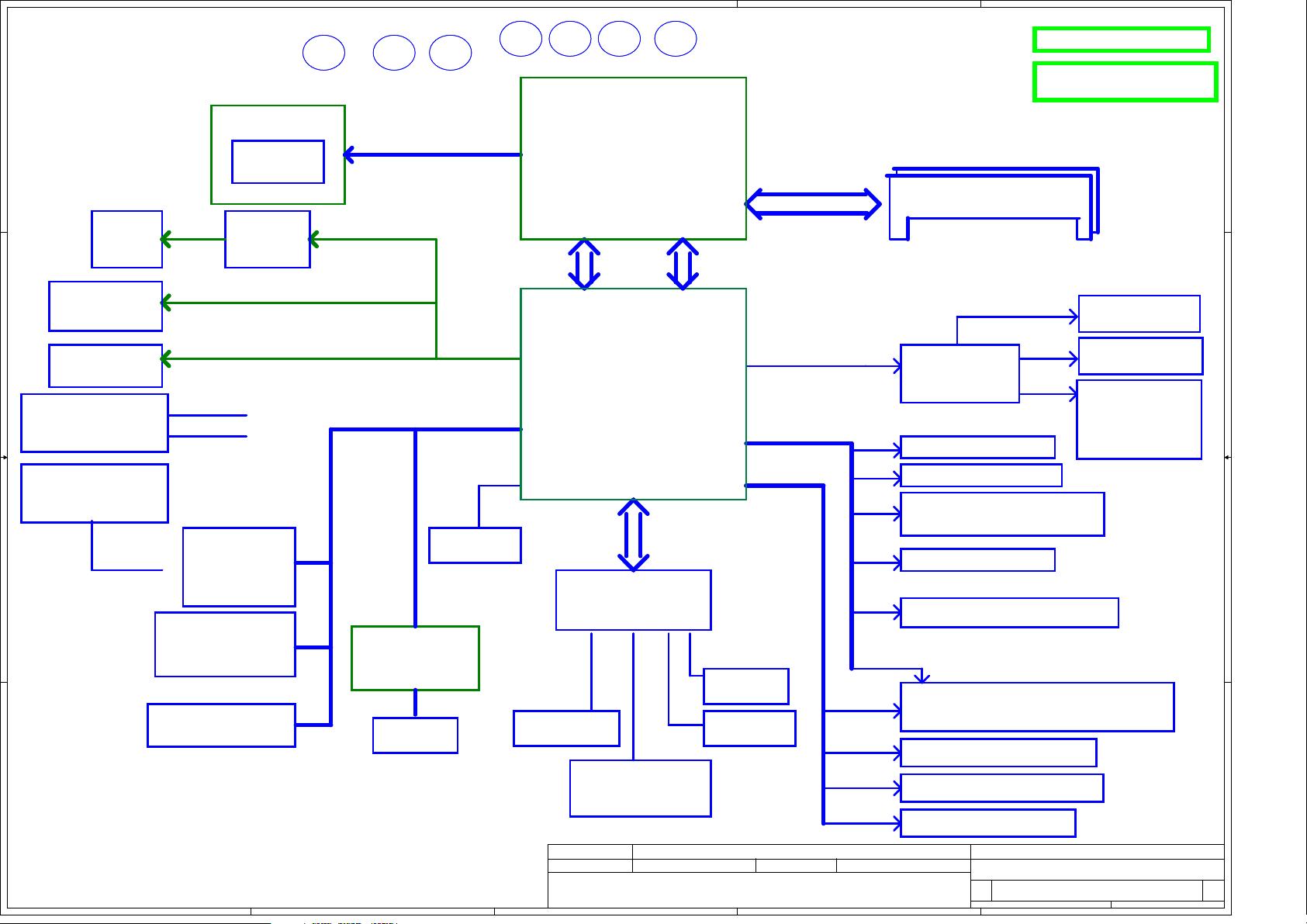

Intel Sandy Bridge Processor with DDRIII + Cougar Point PCH

PIQY0 M/B Schematics Document

REV:1.0

Compal Confidential

2010-12-30

nVIDIA N12P-GT

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1.0

MB Block Diagram

Custom

2 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1.0

MB Block Diagram

Custom

2 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1.0

MB Block Diagram

Custom

2 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

File Name : PIQY0

Compal confidential

SPI ROM

SPI ROM

BIOS

ESATA HDD AND USB CONN

(Right)

HDMI

USB PORT 2.0 x2(Left)

Option3.0 x2

37.5mm*37.5mm

25mm*25mm

SATA3.0 HDD CONN

SATA ODD CONN

DDR3-1333(1.5V)

6*PCI-E BUS

PCI Express

Mini card Slot 1

Passive

level shift

FDI *8

100MHz

2.7GT/s

Intel

6*SATA serial

UP TO 8G

Array Digital MIC

PCI-E X16

POWER & ALS BOARD

BlueTooth CONN

CMOS Camera

RealTek

ALC272/ALC5503

Audio Codec

2Channel Speaker

LPC BUS

CRT Connector

AZALIA

Int.KBD

ENE KB930

Touch Pad

BANK 0, 1, 2, 3

DDR3-SO-DIMM X2

DDR3-1066(1.5V)

Dual Channel

14*USB2.0

LVDS

Connector

EC

Sandy Bridge

Socket-rPGA988B

DMI *4

FCBGA 951

Intel

Cougar Point

CONN

DDR3*8

nVIDIA N12P-GT

VRAM 64*16

Audio Jacks

Stereo

HeadPhone Output

Microphone Input

CAP SENSOR & Slid bar

BOARD

optimus 1.0

optimus 1.0

USB PORT 2.0 x1(Right)

(port0,1

support SATA3)

Card Reader

Jmicro JMB389

SD/MMC/MS/XD

SATA3.0 HDD (SSD)

BCM57781/57780

Broadcom

10/100/1G LAN

RJ45 CONN

USB3.0

EMC1403

WLAN/WiMAX

Thermal Sensor

WLAN/WiMAX

PCI-E(WLAN)

USB(WiMAX)

WLAN/WiMAX

RENESAS

UPD720200

PCI Express

Mini card Slot 2

SATA(SSD)

SSD

ZZZ5

LS6882P

DAZ@

ZZZ5

LS6882P

DAZ@

ZZZ7

LA6881P

DAZ@

ZZZ7

LA6881P

DAZ@

ZZZ6

LS6883P

DAZ@

ZZZ6

LS6883P

DAZ@

ZZZ2

X7625738L01

X761G@

ZZZ2

X7625738L01

X761G@

ZZZ3

X7625738L03

X762G@

ZZZ3

X7625738L03

X762G@

ZZZ4

LS6881P

DAZ@

ZZZ4

LS6881P

DAZ@

ZZZ1

DAZ0HA00100

ZZZ1

DAZ0HA00100

A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

PIQY0 LA6881P

1.0

Notes List

B

3 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

PIQY0 LA6881P

1.0

Notes List

B

3 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

PIQY0 LA6881P

1.0

Notes List

B

3 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

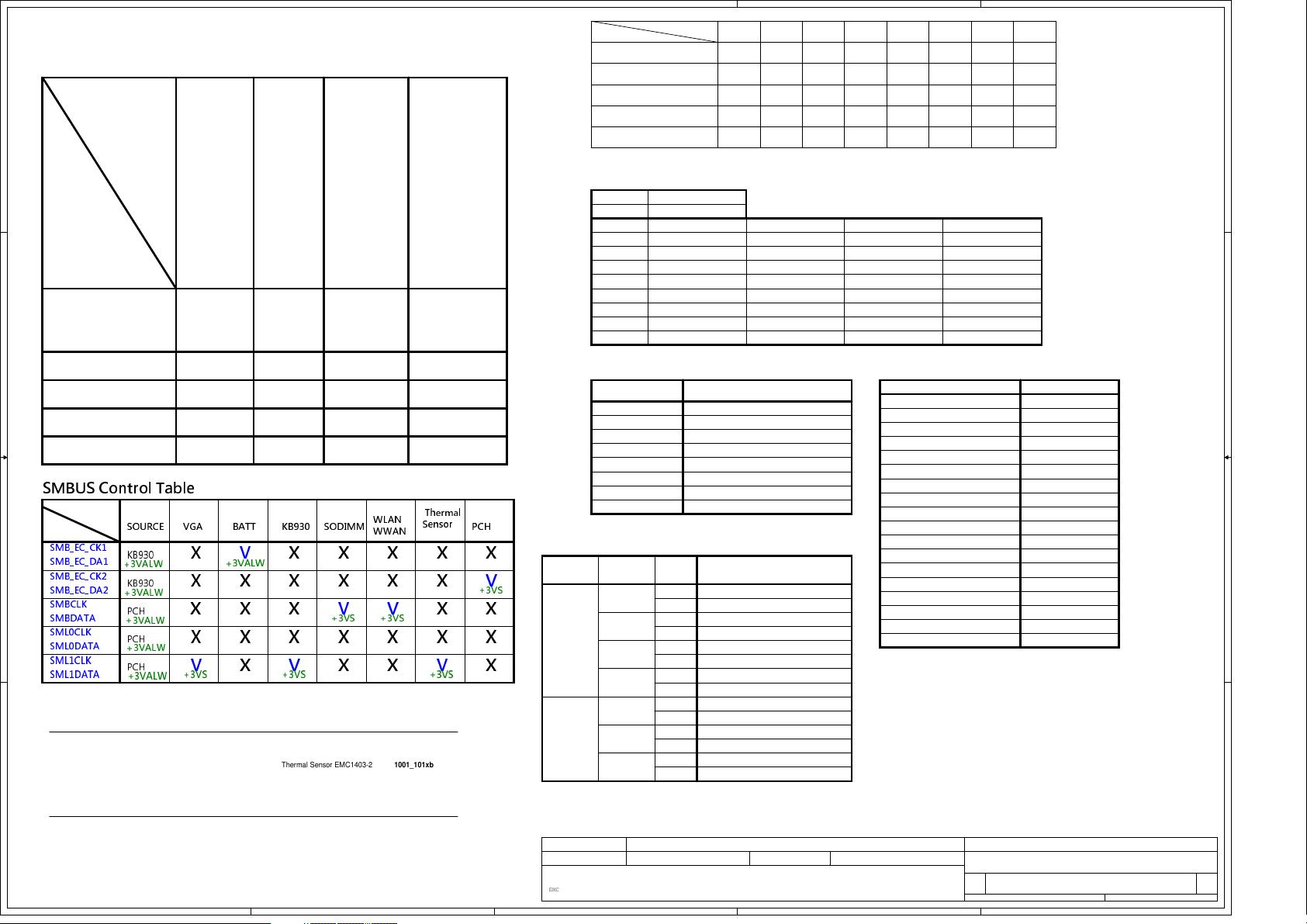

USB 2.0 USB 1.1 Port

3 External

USB Port

USB Port (Right Side COMBO)

Camera

USB/Cable (Right Side)

Blue Tooth

0

1

2

3

4

5

6

7

8

9

10

11

12

13

UHCI0

UHCI1

UHCI2

UHCI3

UHCI4

UHCI5

UHCI6

EHCI1

EHCI2

USB Port Table

Board ID / SKU ID Table for AD channel

BOARD ID Table

EC SM Bus1 address

Device

DDR DIMM0

1001 000Xb

DDR DIMM2

1001 010Xb

STATE

SIGNAL

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

Vcc 3.3V +/- 5%

100K +/- 5%Ra/Rc/Re

Board ID

Rb / Rd / Rf V min

0

1

2

3

0

8.2K +/- 5%

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

0.503 V

0.819 V

0.538 V

0.875 V

AD_BID

V typ

AD_BID

V

AD_BID

max

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

3.300 V

0 V 0 V

4

5

6

7 NC

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

2.341 V

1.185 V 1.264 V

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

PCH SM Bus address

Device Address

Address Address

Voltage Rails

BOM Structure Table

Unpop

BTO Item BOM Structure

ON

ON

ON

ON

ON

ON

ON ON

ON

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

LOW

LOW LOW LOW LOW

LOWLOWLOW

LOW

LOW

LOW

HIGH HIGH HIGH HIGH

HIGHHIGHHIGH

HIGH

HIGH

HIGH

EC SM Bus2 address

Device

Smart Battery

0001 011X b

VRAM

UMA_ONLY@

UMA

OPTI@Optimus

Blue Tooth BT@

@

USB/B (Left Side)

Mini Card(WLAN)

HDMI HDMI@

UMA Only

X761G@:

Sub:

VRAM BOM Config

X762G@:

Sub:

Samsung 1GB

Hynix 1GB

Samsung 2GB

Hynix 2GB

GPU BOM Config

N12P SKU:

OPTI@

X7625738L01

X7625738L02

X7625738L03

X7625738L04

X76@

USB/B (Left Side)

USB3.0 USB30@

ESATA ESATA@

USB Charger USB_CHG@

No USB Charger NO_CHG@

Codec ALC272 272@

5503@Codec ALC5503

LAN 57781 57781@

LAN 57780 57780@

Ventura Feature VENTURA@

Camera CMOS@

GS SKU:

GS@

GT SKU:

GT@

O

X

S3

+3VS

X

X

+3VALW

+5VS

O

+CPU_CORE

OO

X

X X

+VCCP

power

plane

O

O

O

O

X

S5 S4/ Battery only

X X X

+B

State

+1.5VS

+1.5V

S5 S4/AC & Battery

don't exist

S5 S4/AC

+5VALW

S0

O

O

+GFX_CORE

+1.8VS

+0.75VS

+1.05VS

+VGA_CORE

+3VALW

V

X

+3VALW

+3VALW

+3VALW

+3VALW

+3VALW

V

V

X X

+3VS

X X

X

X

X

Thermal

Sensor

PCH

PCH

SML0DATA

SML0CLK

X

SOURCE

SMB_EC_CK2

SODIMMKB930BATTVGA

KB930

SMBUS Control Table

SMBDATA

SMBCLK

SMB_EC_DA1

SMB_EC_CK1

SMB_EC_DA2

WLAN

WWAN

PCH

V

VX

X

X

X

X

X X

X

X

X

X

SML1DATA

SML1CLK

KB930

X

X

X

X

XX X

PCH

X

V

+3VS+3VS

+3VS +3VS

V

+3VS

Thermal Sensor EMC1403-2

1001_101xb

EMC

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1.0

VGA Notes List

4 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

PIQY0 LA6881P

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1.0

VGA Notes List

4 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

PIQY0 LA6881P

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

1.0

VGA Notes List

4 63Wednesday, January 05, 2011

2010/11/30 2011/08

Compal Electronics, Inc.

PIQY0 LA6881P

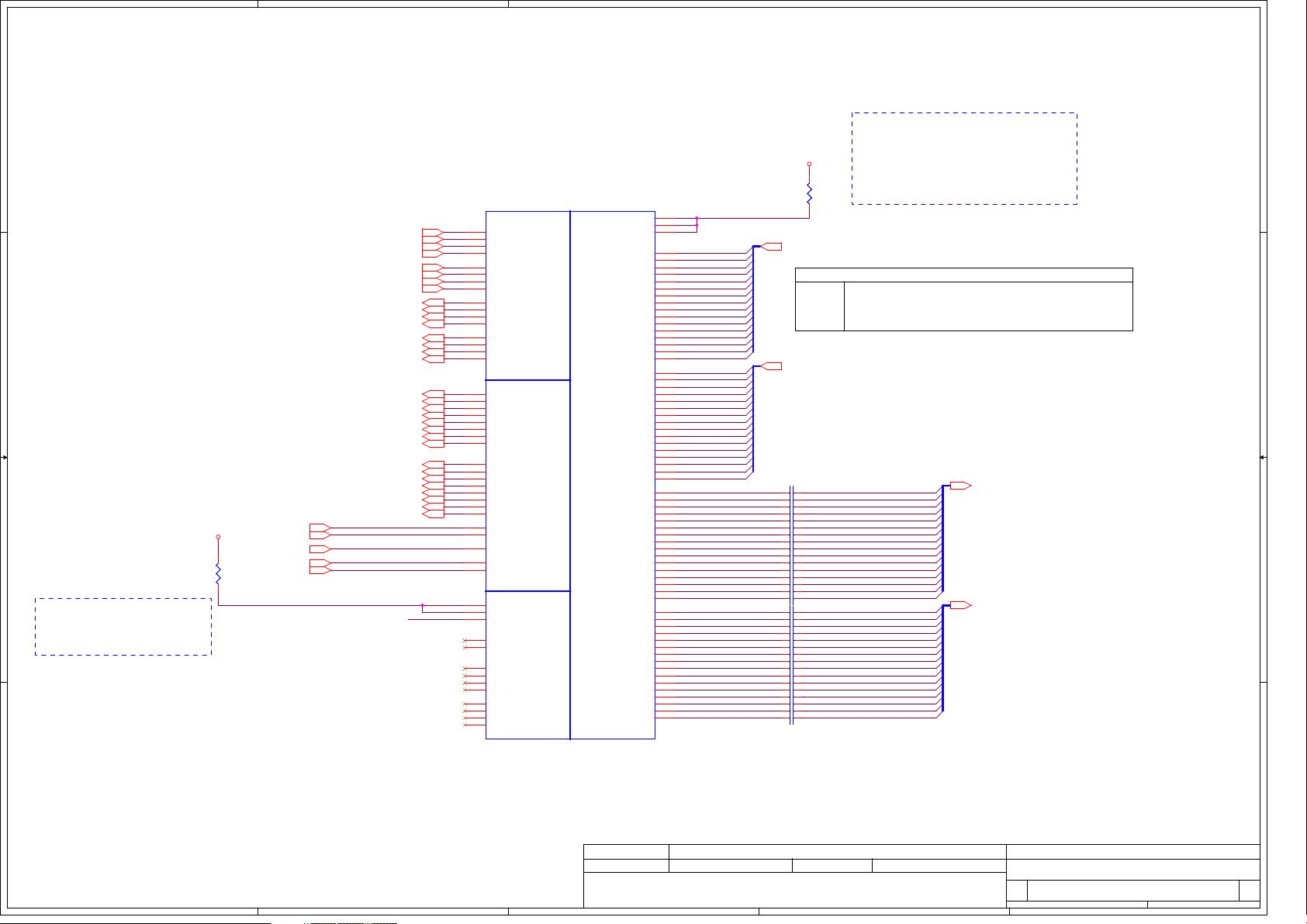

+1.5VS_VGA

tNVVDD >0

tNV-IFPAB_IOVDD >0

tNV-FBVDDQ >0

1. The ramp rate for any rail must be more than 40us.

2. +VGA_CORE <= +3VS_VGA +0.5V

3. +1.5VS_VGA <= +3VS_VGA +0.5V

4. Optimus follows power sequencing rules

specified in discrete GPU design guide.

+3VS_VGA

+1.05VS_VGA

+VGA_CORE

+1.8VS_VGA

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

FDI_FSYNC0

FDI_LSYNC0

FDI_LSYNC1

FDI_FSYNC1

FDI_INT

EDP_COMP

PEG_COMP

PCIE_CRX_GTX_N15

PCIE_CRX_GTX_N10

PCIE_CRX_GTX_N14

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_N8

PCIE_CRX_GTX_N6

PCIE_CRX_GTX_N7

PCIE_CRX_GTX_N4

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_N9

PCIE_CRX_GTX_N12

PCIE_CRX_GTX_N13

PCIE_CRX_GTX_N5

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_N1

PCIE_CRX_GTX_N11

PCIE_CRX_GTX_P15

PCIE_CRX_GTX_P14

PCIE_CRX_GTX_P8

PCIE_CRX_GTX_P4

PCIE_CRX_GTX_P0

PCIE_CRX_GTX_P10

PCIE_CRX_GTX_P7

PCIE_CRX_GTX_P9

PCIE_CRX_GTX_P13

PCIE_CRX_GTX_P6

PCIE_CRX_GTX_P3

PCIE_CRX_GTX_P12

PCIE_CRX_GTX_P5

PCIE_CRX_GTX_P11

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_P2

PCIE_CTX_GRX_C_P0

PCIE_CTX_GRX_C_P10

PCIE_CTX_GRX_C_P15

PCIE_CTX_GRX_C_P14

PCIE_CTX_GRX_C_P8

PCIE_CTX_GRX_C_P6

PCIE_CTX_GRX_C_P4

PCIE_CTX_GRX_C_P13

PCIE_CTX_GRX_C_P7

PCIE_CTX_GRX_C_P1

PCIE_CTX_GRX_C_P9

PCIE_CTX_GRX_C_P12

PCIE_CTX_GRX_C_P3

PCIE_CTX_GRX_C_P5

PCIE_CTX_GRX_C_P2

PCIE_CTX_GRX_C_P11

PCIE_CTX_GRX_C_N14

PCIE_CTX_GRX_C_N15

PCIE_CTX_GRX_C_N0

PCIE_CTX_GRX_C_N10

PCIE_CTX_GRX_C_N6

PCIE_CTX_GRX_C_N8

PCIE_CTX_GRX_C_N13

PCIE_CTX_GRX_C_N4

PCIE_CTX_GRX_C_N9

PCIE_CTX_GRX_C_N5

PCIE_CTX_GRX_C_N2

PCIE_CTX_GRX_C_N12

PCIE_CTX_GRX_C_N7

PCIE_CTX_GRX_C_N1

PCIE_CTX_GRX_C_N11

PCIE_CTX_GRX_C_N3

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_P15

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_P12

eDP_HPD

DMI_CTX_PRX_P0<16>

DMI_CRX_PTX_P0<16>

DMI_CTX_PRX_N1<16>

DMI_CRX_PTX_N1<16>

DMI_CTX_PRX_P3<16>

DMI_CRX_PTX_P3<16>

DMI_CTX_PRX_P2<16>

DMI_CTX_PRX_N0<16>

DMI_CRX_PTX_N3<16>

DMI_CRX_PTX_P2<16>

DMI_CTX_PRX_N3<16>

DMI_CTX_PRX_P1<16>

DMI_CRX_PTX_N0<16>

DMI_CRX_PTX_N2<16>

DMI_CRX_PTX_P1<16>

DMI_CTX_PRX_N2<16>

FDI_CTX_PRX_N0<16>

FDI_CTX_PRX_N1<16>

FDI_CTX_PRX_N2<16>

FDI_CTX_PRX_N3<16>

FDI_CTX_PRX_N4<16>

FDI_CTX_PRX_N5<16>

FDI_CTX_PRX_N6<16>

FDI_CTX_PRX_N7<16>

FDI_CTX_PRX_P0<16>

FDI_CTX_PRX_P1<16>

FDI_CTX_PRX_P2<16>

FDI_CTX_PRX_P3<16>

FDI_CTX_PRX_P4<16>

FDI_CTX_PRX_P5<16>

FDI_CTX_PRX_P6<16>

FDI_CTX_PRX_P7<16>

FDI_FSYNC0<16>

FDI_FSYNC1<16>

FDI_INT<16>

FDI_LSYNC0<16>

FDI_LSYNC1<16>

PCIE_CRX_GTX_N[0..15] <23>

PCIE_CTX_GRX_P[0..15] <23>

PCIE_CTX_GRX_N[0..15] <23>

PCIE_CRX_GTX_P[0..15] <23>

+1.05VS

+1.05VS

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

PIQY0 LA6881P

1.0

PROCESSOR(1/7) DMI,FDI,PEG

Custom

5 63Wednesday, January 05, 2011

2010/11/30 2011/08

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

PIQY0 LA6881P

1.0

PROCESSOR(1/7) DMI,FDI,PEG

Custom

5 63Wednesday, January 05, 2011

2010/11/30 2011/08

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

PIQY0 LA6881P

1.0

PROCESSOR(1/7) DMI,FDI,PEG

Custom

5 63Wednesday, January 05, 2011

2010/11/30 2011/08

PEG_ICOMPI and RCOMPO signals should be

shorted and routed

with - max length = 500 mils - typical

impedance = 43 mohms

PEG_ICOMPO signals should be routed with -

max length = 500 mils

- typical impedance = 14.5 mohms

eDP_COMPIO and ICOMPO signals

should be tied together, then

connected to the VCCIO rail

via a single 24.9ohm resistor.

Compal Electronics, Inc.

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

0:Lane Reversed

1: Normal Operation; Lane # definition matches

socket pin map definition

*

C18 0.1U_0402_10V6K

OPTI@

C18 0.1U_0402_10V6K

OPTI@

1 2

C19 0.1U_0402_10V6K

OPTI@

C19 0.1U_0402_10V6K

OPTI@

1 2

C3 0.1U_0402_10V6K

OPTI@

C3 0.1U_0402_10V6K

OPTI@

1 2

C28 0.1U_0402_10V6K

OPTI@

C28 0.1U_0402_10V6K

OPTI@

1 2

C11 0.1U_0402_10V6K

OPTI@

C11 0.1U_0402_10V6K

OPTI@

1 2

C14 0.1U_0402_10V6K

OPTI@

C14 0.1U_0402_10V6K

OPTI@

1 2

R7

24.9_0402_1%

R7

24.9_0402_1%

12

C2 0.1U_0402_10V6K

OPTI@

C2 0.1U_0402_10V6K

OPTI@

1 2

C32 0.1U_0402_10V6K

OPTI@

C32 0.1U_0402_10V6K

OPTI@

1 2

R1

24.9_0402_1%

R1

24.9_0402_1%

12

C20 0.1U_0402_10V6K

OPTI@

C20 0.1U_0402_10V6K

OPTI@

1 2

C30 0.1U_0402_10V6K

OPTI@

C30 0.1U_0402_10V6K

OPTI@

1 2

C12 0.1U_0402_10V6K

OPTI@

C12 0.1U_0402_10V6K

OPTI@

1 2

PCI EXPRESS* - GRAPHICS

DMI

Intel(R) FDI

eDP

JCPU1A

Sandy Bridge_rPGA_Rev1p0

ME@

PCI EXPRESS* - GRAPHICS

DMI

Intel(R) FDI

eDP

JCPU1A

Sandy Bridge_rPGA_Rev1p0

ME@

DMI_RX#[0]

B27

DMI_RX#[1]

B25

DMI_RX#[2]

A25

DMI_RX#[3]

B24

DMI_RX[0]

B28

DMI_RX[1]

B26

DMI_RX[2]

A24

DMI_RX[3]

B23

DMI_TX#[0]

G21

DMI_TX#[1]

E22

DMI_TX#[2]

F21

DMI_TX#[3]

D21

DMI_TX[0]

G22

DMI_TX[1]

D22

DMI_TX[3]

C21

DMI_TX[2]

F20

FDI0_TX#[0]

A21

FDI0_TX#[1]

H19

FDI0_TX#[2]

E19

FDI0_TX#[3]

F18

FDI1_TX#[0]

B21

FDI1_TX#[1]

C20

FDI1_TX#[2]

D18

FDI1_TX#[3]

E17

FDI0_TX[0]

A22

FDI0_TX[1]

G19

FDI0_TX[2]

E20

FDI0_TX[3]

G18

FDI1_TX[0]

B20

FDI1_TX[1]

C19

FDI1_TX[2]

D19

FDI1_TX[3]

F17

FDI0_FSYNC

J18

FDI1_FSYNC

J17

FDI_INT

H20

FDI0_LSYNC

J19

FDI1_LSYNC

H17

PEG_ICOMPI

J22

PEG_ICOMPO

J21

PEG_RCOMPO

H22

PEG_RX#[0]

K33

PEG_RX#[1]

M35

PEG_RX#[2]

L34

PEG_RX#[3]

J35

PEG_RX#[4]

J32

PEG_RX#[5]

H34

PEG_RX#[6]

H31

PEG_RX#[7]

G33

PEG_RX#[8]

G30

PEG_RX#[9]

F35

PEG_RX#[10]

E34

PEG_RX#[11]

E32

PEG_RX#[12]

D33

PEG_RX#[13]

D31

PEG_RX#[14]

B33

PEG_RX#[15]

C32

PEG_RX[0]

J33

PEG_RX[1]

L35

PEG_RX[2]

K34

PEG_RX[3]

H35

PEG_RX[4]

H32

PEG_RX[5]

G34

PEG_RX[6]

G31

PEG_RX[7]

F33

PEG_RX[8]

F30

PEG_RX[9]

E35

PEG_RX[10]

E33

PEG_RX[11]

F32

PEG_RX[12]

D34

PEG_RX[13]

E31

PEG_RX[14]

C33

PEG_RX[15]

B32

PEG_TX#[0]

M29

PEG_TX#[1]

M32

PEG_TX#[2]

M31

PEG_TX#[3]

L32

PEG_TX#[4]

L29

PEG_TX#[5]

K31

PEG_TX#[6]

K28

PEG_TX#[7]

J30

PEG_TX#[8]

J28

PEG_TX#[9]

H29

PEG_TX#[10]

G27

PEG_TX#[11]

E29

PEG_TX#[12]

F27

PEG_TX#[13]

D28

PEG_TX#[14]

F26

PEG_TX#[15]

E25

PEG_TX[0]

M28

PEG_TX[1]

M33

PEG_TX[2]

M30

PEG_TX[3]

L31

PEG_TX[4]

L28

PEG_TX[5]

K30

PEG_TX[6]

K27

PEG_TX[7]

J29

PEG_TX[8]

J27

PEG_TX[9]

H28

PEG_TX[10]

G28

PEG_TX[11]

E28

PEG_TX[12]

F28

PEG_TX[13]

D27

PEG_TX[14]

E26

PEG_TX[15]

D25

eDP_AUX

C15

eDP_AUX#

D15

eDP_TX[0]

C17

eDP_TX[1]

F16

eDP_TX[2]

C16

eDP_TX[3]

G15

eDP_TX#[0]

C18

eDP_TX#[1]

E16

eDP_TX#[2]

D16

eDP_TX#[3]

F15

eDP_COMPIO

A18

eDP_HPD

B16

eDP_ICOMPO

A17

C1 0.1U_0402_10V6K

OPTI@

C1 0.1U_0402_10V6K

OPTI@

1 2

C24 0.1U_0402_10V6K

OPTI@

C24 0.1U_0402_10V6K

OPTI@

1 2

C4 0.1U_0402_10V6K

OPTI@

C4 0.1U_0402_10V6K

OPTI@

1 2

C21 0.1U_0402_10V6K

OPTI@

C21 0.1U_0402_10V6K

OPTI@

1 2

C16 0.1U_0402_10V6K

OPTI@

C16 0.1U_0402_10V6K

OPTI@

1 2

C29 0.1U_0402_10V6K

OPTI@

C29 0.1U_0402_10V6K

OPTI@

1 2

C6 0.1U_0402_10V6K

OPTI@

C6 0.1U_0402_10V6K

OPTI@

1 2

C5 0.1U_0402_10V6K

OPTI@

C5 0.1U_0402_10V6K

OPTI@

1 2

C31 0.1U_0402_10V6K

OPTI@

C31 0.1U_0402_10V6K

OPTI@

1 2

C15 0.1U_0402_10V6K

OPTI@

C15 0.1U_0402_10V6K

OPTI@

1 2

C13 0.1U_0402_10V6K

OPTI@

C13 0.1U_0402_10V6K

OPTI@

1 2

C7 0.1U_0402_10V6K

OPTI@

C7 0.1U_0402_10V6K

OPTI@

1 2

C9 0.1U_0402_10V6K

OPTI@

C9 0.1U_0402_10V6K

OPTI@

1 2

C23 0.1U_0402_10V6K

OPTI@

C23 0.1U_0402_10V6K

OPTI@

1 2

C26 0.1U_0402_10V6K

OPTI@

C26 0.1U_0402_10V6K

OPTI@

1 2

C17 0.1U_0402_10V6K

OPTI@

C17 0.1U_0402_10V6K

OPTI@

1 2

C25 0.1U_0402_10V6K

OPTI@

C25 0.1U_0402_10V6K

OPTI@

1 2

C22 0.1U_0402_10V6K

OPTI@

C22 0.1U_0402_10V6K

OPTI@

1 2

C8 0.1U_0402_10V6K

OPTI@

C8 0.1U_0402_10V6K

OPTI@

1 2

C10 0.1U_0402_10V6K

OPTI@

C10 0.1U_0402_10V6K

OPTI@

1 2

C27 0.1U_0402_10V6K

OPTI@

C27 0.1U_0402_10V6K

OPTI@

1 2