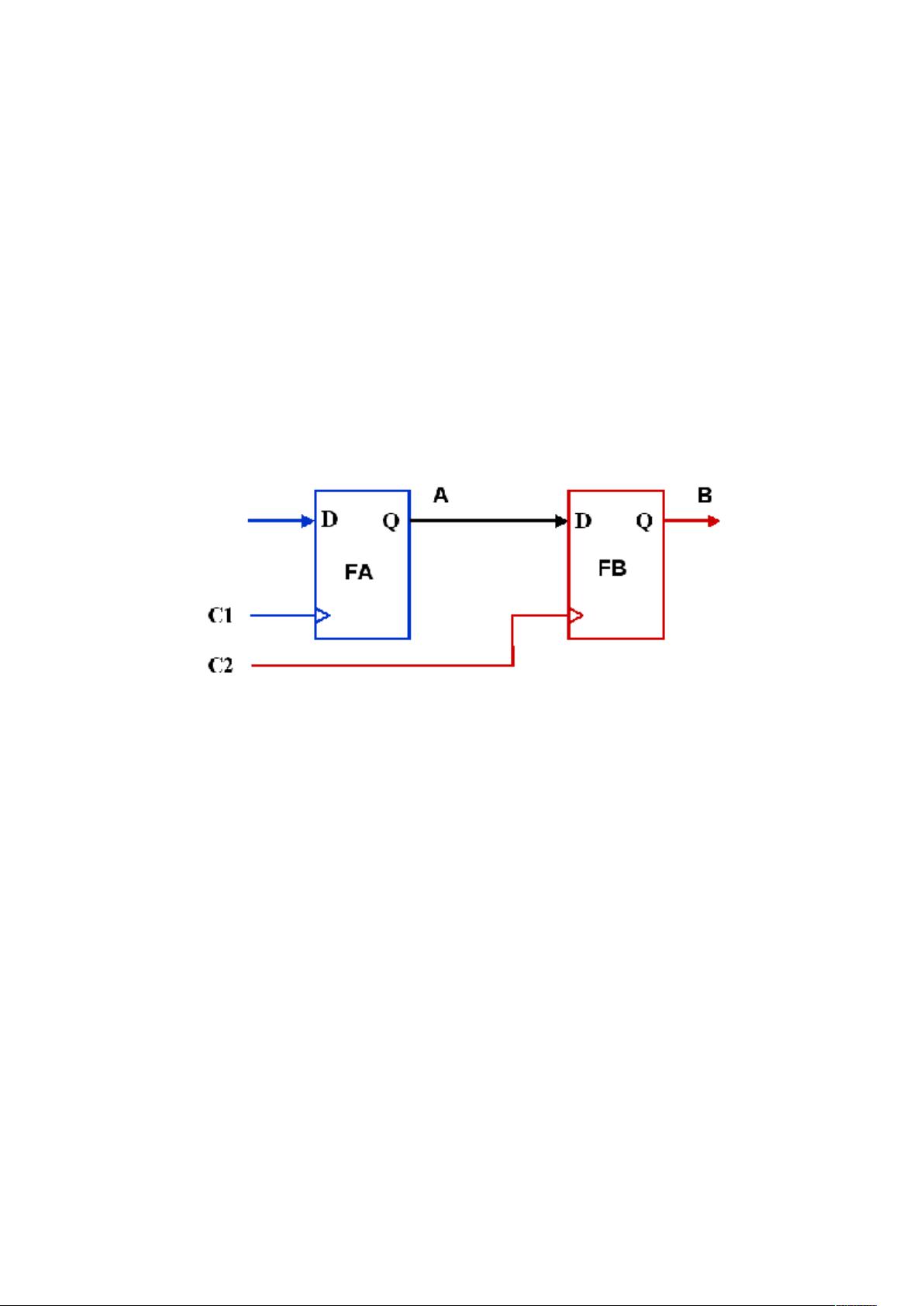

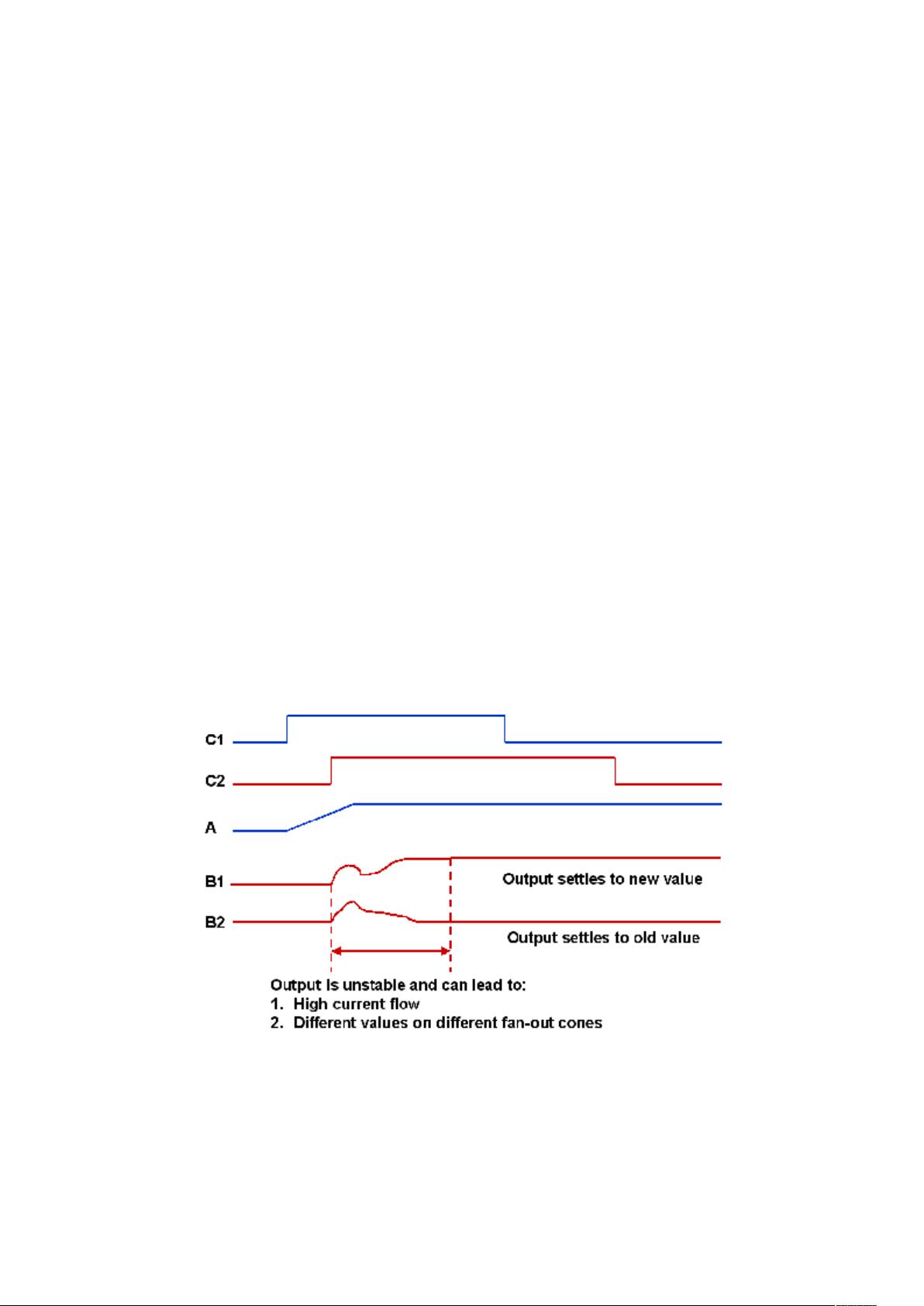

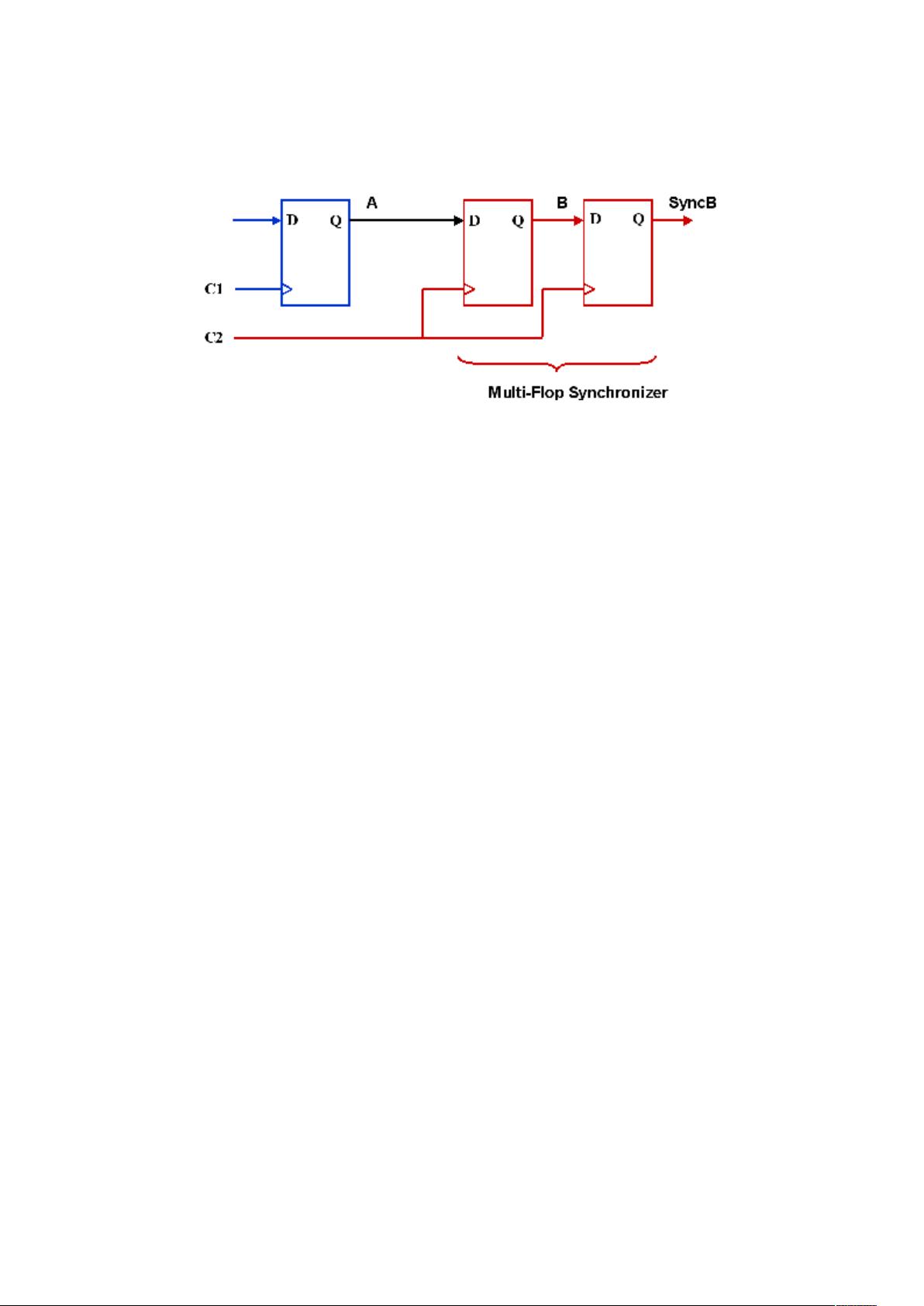

在当前的集成电路设计中,FPGA(Field-Programmable Gate Array)的应用越来越广泛,而随着SoC(System-on-Chip)的复杂度不断提升,数据在不同时钟域之间的传递成为了一个关键的设计挑战。时钟域交叉(Clock Domain Crossing, CDC)正是这种挑战的核心所在。本文由Saurabh Verma和Ashima S. Dabare等人撰写,探讨了时钟域交叉问题及其解决方案。 1. 时钟域交叉的基本概念 时钟域交叉是指数据从由一个时钟驱动的触发器(flip-flop)传输到由另一个时钟驱动的触发器。如图1所示,信号A在C1时钟域中启动,需要被C2时钟域正确捕获。两个时钟之间的关系决定了数据传输可能遇到的问题类型,以及解决这些问题的方法。传统方法如仿真和静态时序分析已不足以确保跨时钟域的数据传输一致性与可靠性。 2. 不同类型的时钟域交叉问题及解决方案 这里主要讨论了三种可能在时钟域交叉中出现的问题: a) 数据丢失(Data Loss):当源时钟C1的边沿到来时,如果目的地时钟C2尚未处于采样状态,信号A可能无法被正确捕获。为解决这个问题,可以使用同步器(synchronizer)或握手协议(handshaking),确保数据在接收端有效时被采样。 b) 潜在竞争/冒险( metastability):两个时钟之间的相位关系可能导致源触发器和目标触发器之间出现不稳定状态。这种不稳定状态可能导致数据错误。解决方法通常包括增加级联触发器的数量,以提高 metastability 的分辨率。 c) 延迟不匹配(Delay Mismatch):由于时钟路径的不同延迟,数据可能会在目标触发器之前或之后到达,导致数据错误。通过精确的时序分析和路径约束管理,可以尽量减少这种不匹配。 3. 新的验证方法 为了确保跨时钟域的数据传输正确性,文章提出了新的验证方法。这种方法可能包括增强型仿真技术,如混合信号仿真,以及形式验证工具,它们能够检测出传统方法可能遗漏的潜在问题。此外,利用约束随机化和覆盖率驱动的测试策略也能更全面地覆盖各种时钟域交叉情况。 4. 实践应用与注意事项 在实际设计中,需要对时钟域交叉进行详尽的分析,包括时钟树的构建、时钟偏移的计算以及边界条件的测试。设计者应遵循最佳实践,例如使用多级同步器,避免在时钟域交叉处使用组合逻辑,并确保充分的测试覆盖。 总结,理解并解决时钟域交叉问题对于FPGA设计至关重要,因为这直接影响到系统的稳定性和可靠性。通过深入研究不同的时钟域交叉问题,结合有效的验证策略,可以显著降低设计风险,确保数据在不同时钟域间安全、准确地传输。

剩余18页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Rainbow 8.1.0.SPC3 迁移工具操作指南

- 水泵反渗透和一拖3恒压供水 1.西门子SMART和海为云触摸屏做的反渗透和恒压供水电气控制系统, 程序注释完善,在山东某养鸡场运行正常 2,有正常制水模式,反洗模式,原水恒压供水和供水恒压供水(1托

- Python 与 MySQL 基础:开发数据管理应用的必备技能 - pdf

- PLC工业超滤净水控制系统(牧场用的比较多) 1.西门子SMART和海为云触摸屏做的超滤控制系统 或者是昆仑同泰触摸屏加远程模块,可以手机远程监控,修改监控程序; 2,包括单套和双套系统(可以清洗超滤

- 癌症数据,癌症患者数据集,涵盖:人口统计学细节、生活方式因素、癌症诊断信息、治疗详情以及结果等

- 全套恒压供水一拖三程序图纸(看描述)恒压供水一拖三图纸程序 1.采用西门子SMART SR20 CPU 加AE04模块; 2.触摸屏采用昆仑通态;同时通讯PLC和变频器; 3.PLC模拟量检测压

- python使用mysql基础教程

- python使用mysql基础教程

- Python 与 MySQL 基础:数据交互与数据库操作-pdf

- python使用mysql基础教程

- 永磁同步电机的谐波注入补偿simulink模型仿真 5次7次电流谐波抑制;

- python使用mysql基础教程

- python使用mysql基础教程

- python使用mysql基础教程

- 西门子1200-1500博途追款锁机软件程序例程,经典程序编程及到期催款锁机,采用SCL语言编程子程序,内含物料运输顺序控制,运料车自动装卸料控制,展厅人数控制,风机运行监控,卫生间定时冲水,冒泡排序

- python使用mysql基础教程

信息提交成功

信息提交成功