没有合适的资源?快使用搜索试试~ 我知道了~

电源管理 1 )只要求两条总线线路一条串行数据线 SDA 一条串行时钟线 SCL , 所以也成为 两线式串行总线。 2 )每个连接到总线的器件都可以通过唯一的地址和一直存在的简单的主机从机 关系软件设定地址主机可以作为主机发送器或主机接收器 3 )它是一个真正的多主机总线如果两个或更多主机同时初始化数据传输可以通 过冲突检测和仲裁防止数据被破坏 * 串行的 8 位双向数据传输位速率在标准模式 下可达 100kbit/s 快速模式下可达 400kbit/s 高速模式下可达 3.4Mbit/s

资源推荐

资源详情

资源评论

1

9

-

4

6

3

5

;

5

/

0

9

DS2782

Stand-Alone Fuel Gauge IC

1 of 28

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata

.

www.maxim-ic.com

GENERAL DESCRIPTION

The DS2782 measures voltage, temperature and

current, and estimates available capacity for

rechargeable lithium ion and lithium-ion polymer

batteries. Cell characteristics and application

parameters used in the calculations are stored in on-

chip EEPROM. The available capacity registers

report a conservative estimate of the amount of

charge that can be removed given the current

temperature, discharge rate, stored charge and

application parameters. Capacity estimation reported

in mAh remaining and percentage of full.

APPLICATIONS

Digital Still Cameras

Sub-Notebook Computers

Handheld PC Data Terminals

3G Multimedia Wireless Handsets

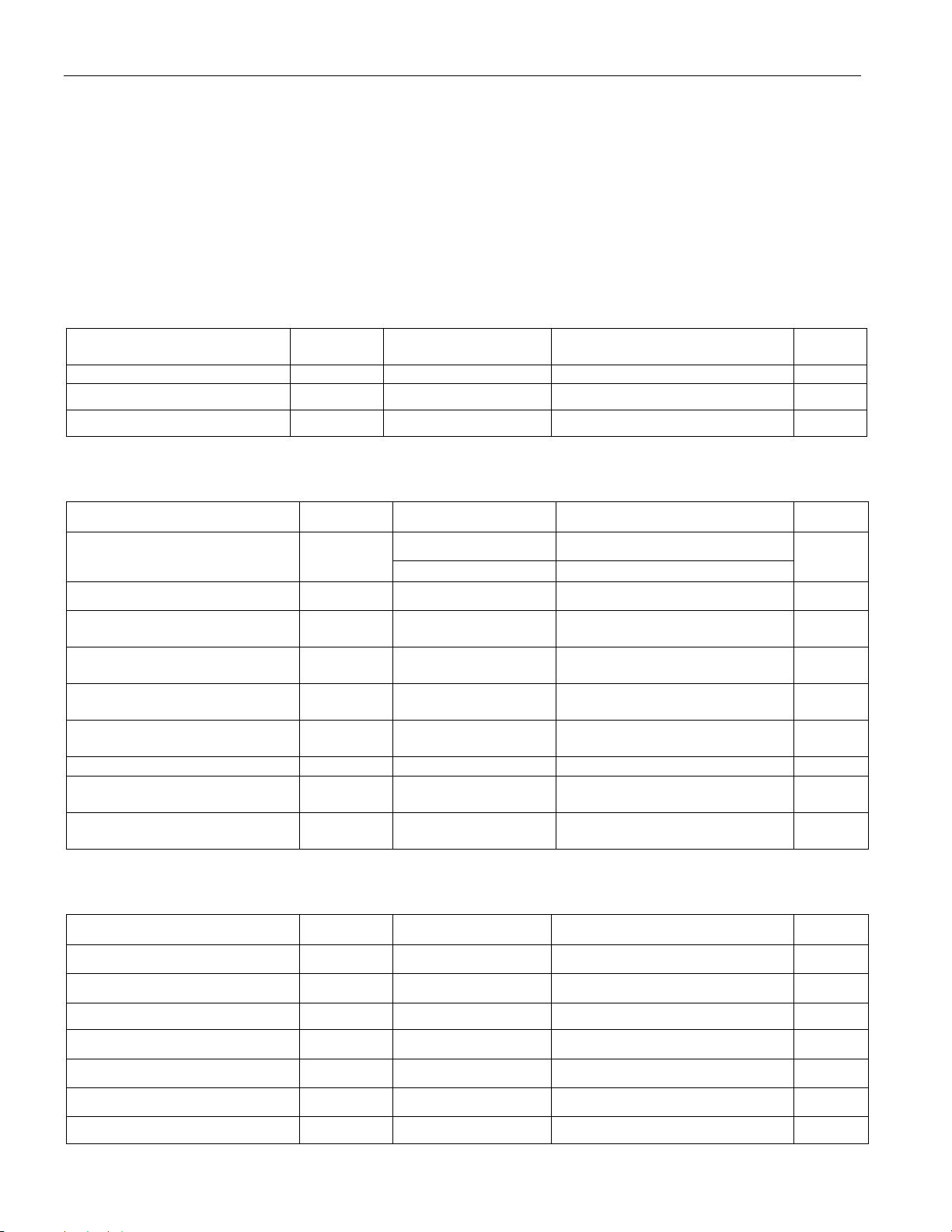

TYPICAL OPERATING CIRCUIT

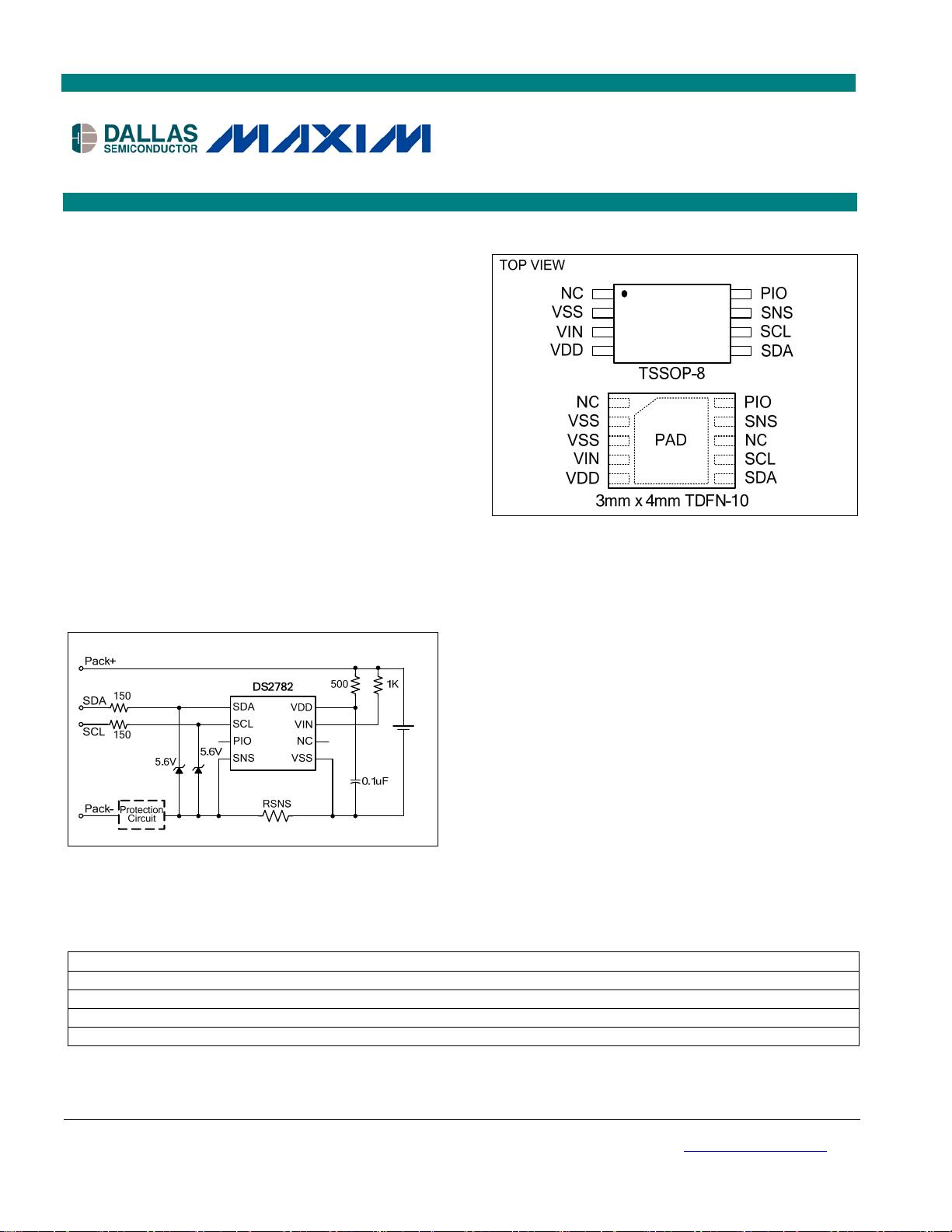

PIN CONFIGURATIONS

FEATURES

Precision Voltage, Temperature, and Current

Measurement System

Accurate Stable Internal Time Base

Absolute and Relative Capacity Estimated from

Coulomb Count, Discharge Rate, Temperature

and Battery Cell Characteristics

Accurate Warning of Low Battery Conditions

Automatic Backup of Coulomb Count and Age

Estimation to Nonvolatile (NV) EEPROM

Gain and Tempco Calibration Allows the Use of

Low-Cost Sense Resistors

24-Byte User EEPROM or 16-Byte User

EEPROM and Unique 64-Bit ID

Industry 2-Wire Interface with Programmable

Slave Address

Tiny 8-Pin TSSOP and 10-TDFN Packages

Embed Easily in Thin Prismatic Cell Packs

ORDERING INFORMATION

PART PIN-PACKAGE TOP MARK

DS2782E+ 8 TSSOP 2782+

DS2782E+T&R 8 TSSOP 2782+

DS2782G+ 10 TDFN-EP* 2782+

DS2782G+T&R 10 TDFN-EP* 2782+

Note: To order devices with the unique 64-bit ID option, contact Maxim sales.

+Denotes a lead(Pb)-free/RoHS-compliant package.

T&R = Tape and reel.

*EP = Exposed pad.

测量电压,温度和 电流,

DS2782

2 of 28

ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Pin Relative to V

SS

-0.3V to +6.0V

Voltage Range on V

IN

Relative to V

SS

-0.3V to (V

DD

+ 0.3V)

Operating Temperature Range

-40°C to +85°C

Storage Temperature Range

-55°C to +125°C

Soldering Temperature

Refer to the IPC/JEDEC J-STD-020 Specification.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is

not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

RECOMMENDED DC OPERATING CHARACTERISTICS

(V

DD

= 2.5V to 4.5V; T

A

= -20°C to +70°C, unless otherwise noted. Typical values are at T

A

= +25°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Supply Voltage V

DD

(Note 1) +2.5 +4.5 V

SCL, VIN Voltage Range (Note 1) -0.3 +4.5 V

SDA, PIO Voltage Range (Note 1) -0.3 +5.5 V

DC ELECTRICAL CHARACTERISTICS

(V

DD

= 2.5V to 4.5V; T

A

= -20°C to +70°C, unless otherwise noted. Typical values are at T

A

= +25°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

2.5V ≤ V

DD

≤ 4.2V 65 95

ACTIVE Current I

ACTIVE

105

A

SLEEP Mode Current I

SLEEP

2.5V ≤ V

DD

≤ 4.2V 1 3

A

Input Logic-High:

SDA, SCL, PIO

V

IH

(Note 1) 1.5 V

Input Logic-Low:

SDA, SCL, PIO

V

IL

(Note 1) 0.6 V

Output Logic-Low:

SDA, PIO

V

OL

I

OL

= 4mA (Note 1) 0.4 V

Pulldown Current:

SDA, SCL, PIO

I

PD

V

SDA

, V

SCL

, V

PIO

=

0.4V

0.2

A

V

IN

Input Resistance R

IN

15

M

Bus Low to Sleep Time t

SLEEP

SDA, SCL < V

IL

(Note 2)

2.2 s

Undervoltage SLEEP

Threshold

V

SLEEP

(Note 1) 2.40 2.45 2.50 V

ELECTRICAL CHARACTERISTICS: TEMPERATURE, VOLTAGE, CURRENT

(V

CC

= 2.5V to 4.5V; T

A

= -20°C to +70°C, unless otherwise noted. Typical values are at T

A

= +25°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Temperature Resolution T

LSB

0.125 °C

Temperature Error T

ERR

±3 °C

Voltage Resolution V

LSB

4.88 mV

Voltage Full-Scale V

FS

0 4.5 V

Voltage Error V

ERR

±50 mV

Current Resolution I

LSB

1.56

V

Current Full-Scale I

FS

±51.2 mV

DS2782

3 of 28

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Current Gain Error I

GERR

(Note 3) ±1

% Full-

Scale

Current Offset Error I

OERR

0°C ≤ T

A

≤ +70°C,

2.5V ≤ V

DD

≤ 4.2V

(Note 5)

-7.82 +12.5

V

Accumulated Current Offset q

OERR

0°C ≤ T

A

≤ +70°C,

2.5V ≤ V

DD

≤ 4.2V

V

SNS

= V

SS

(Notes 4, 5)

-188 +0

Vhr/

day

V

DD

= 3.8V,

T

A

= +25°C

±1

0°C ≤ T

A

≤ +70°C,

2.5V ≤ VDD ≤ 4.2V

±2

Time-Base Error t

ERR

±3

%

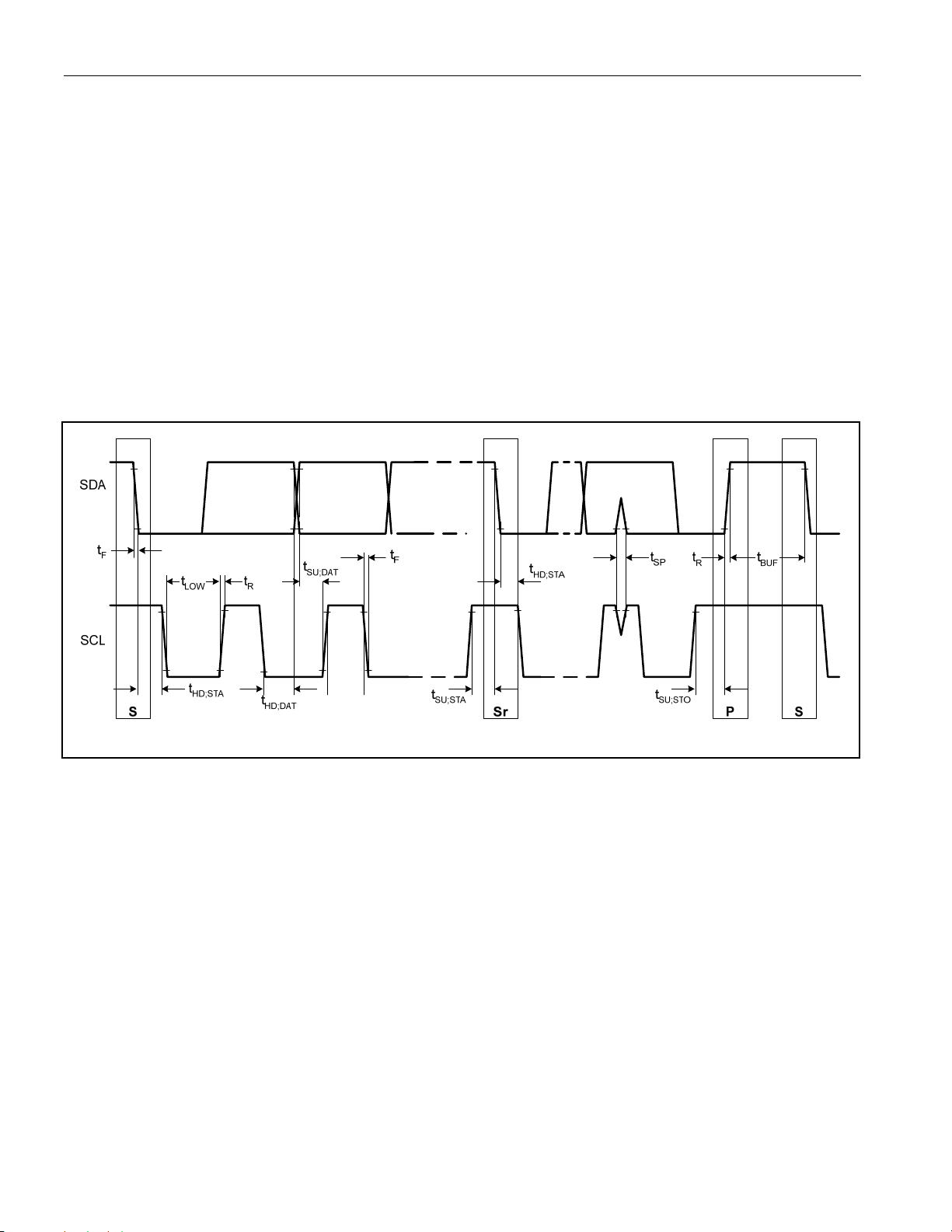

ELECTRICAL CHARACTERISTICS: 2-WIRE INTERFACE

(2.5V V

DD

4.5V, T

A

= -20C to +70C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SCL Clock Frequency

f

SCL

(Note 6) 0 400 kHz

Bus Free Time Between a

STOP and START Condition

t

BUF

1.3

s

Hold Time (Repeated)

START Condition

t

HD:STA

(Note 7) 0.6

s

Low Period of SCL Clock

t

LOW

1.3

s

High Period of SCL Clock

t

HIGH

0.6

s

Setup Time for a Repeated

START Condition

t

SU:STA

0.6

s

Data Hold Time

t

HD:DAT

(Note 8, 9) 0 0.9

s

Data Setup Time

t

SU:DAT

(Note 8) 100 ns

Rise Time of Both SDA and

SCL Signals

t

R

20 +

0.1C

B

300 ns

Fall Time of Both SDA and

SCL Signals

t

F

20 +

0.1C

B

300 ns

Setup Time for STOP

Condition

t

SU:STO

0.6

s

Spike Pulse Widths

Suppressed by Input Filter

t

SP

(Note 10) 0 50 ns

Capacitive Load for Each Bus

Line

C

B

(Note 11) 400 pF

SCL, SDA Input Capacitance C

BIN

60 pF

EEPROM RELIABILITY SPECIFICATION

(V

CC

= 2.5V to 4.5V; T

A

= -20°C to +70°C, unless otherwise noted. Typical values are at T

A

= +25°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

EEPROM Copy Time t

EEC

10 ms

EEPROM Copy Endurance N

EEC

T

A

= +50°C 50,000 cycles

DS2782

4 of 28

Note 1: All voltages are referenced to V

SS

.

Note 2: To properly enter sleep mode the application should hold the bus low for longer than the maximum t

SLEEP

.

Note 3: Factory calibrated accuracy. Higher accuracy can be achieved by in-system calibration by the user.

Note 4: Accumulation bias register set to 00h.

Note 5: Parameters guaranteed by design.

Note 6: Timing must be fast enough to prevent the DS2782 from entering sleep mode due to bus low for period >

t

SLEEP

.

Note 7: f

SCL

must meet the minimum clock low time plus the rise/fall times.

Note 8: The maximum t

HD:DAT

has only to be met if the device does not stretch the LOW period (t

LOW

) of the SCL

signal.

Note 9: This device internally provides a hold time of at least 300 ns for the SDA signal (referred to the VIHmin of

the SCL signal) to bridge the undefined region of the falling edge of SCL.

Note 10: Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

Note 11: C

B

– total capacitance of one bus line in pF.

Figure 1. I

2

C Bus Timing Diagram

DS2782

5 of 28

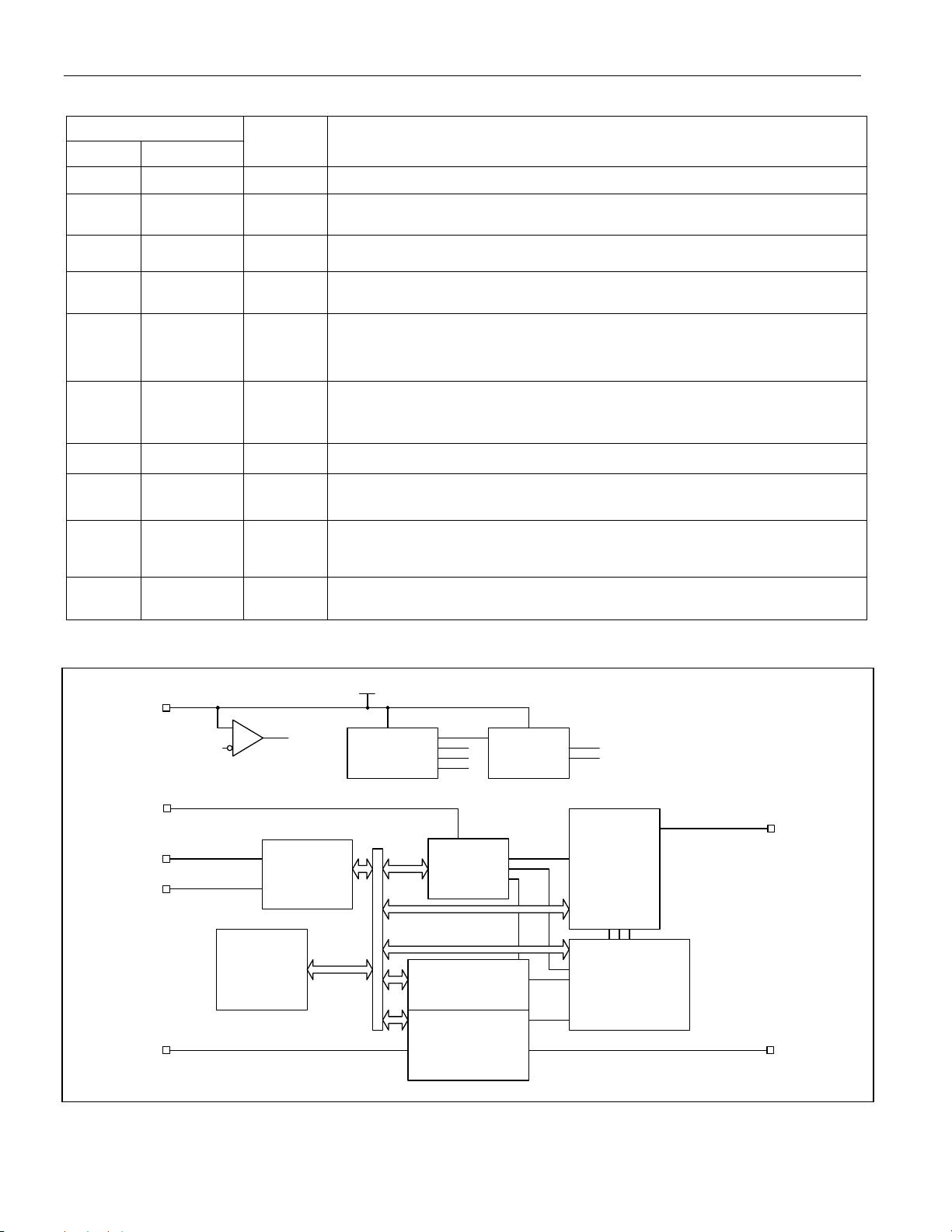

PIN DESCRIPTION

PIN

TSSOP TDFN-EP

NAME

FUNCTION

1 1 N.C. Not Connected. Pin not connected internally, float or connect to VSS.

2 2, 3 VSS

Device Ground. Connect directly to the negative terminal of the battery

cell. Connect the sense resistor between VSS and SNS.

3 4 VIN

Voltage Sense Input. The voltage of the battery cell is monitored through

this input pin.

4 5 V

DD

Power-Supply Input. Connect to the positive terminal of the battery cell

through a decoupling network.

5 6 SDA

Serial Data Input/Output. 2-Wire data line. Open-drain output driver.

Connect this pin to the DATA terminal of the battery pack. Pin has an

internal pull-down (I

PD

) for sensing disconnection.

6 7 SCL

Serial Clock Input. 2-Wire clock line. Input only. Connect this pin to the

CLOCK terminal of the battery pack. Pin has an internal pull-down (I

PD

) for

sensing disconnection.

— 8 N.C.

No Connection

7 9 SNS

Sense Resistor Connection. Connect to the negative terminal of the

battery pack. Connect the sense resistor between VSS and SNS.

8 10 PIO

Programmable I/O Pin. Can be configured as input or output to monitor or

control user-defined external circuitry. Output driver is open drain. This pin

has a weak internal pulldown (I

PD

).

— EP EP Exposed Pad. Connect to VSS or leave floating.

Figure 2. Block Diagram

VPOR

SDA

2-Wire

Interface

BIAS/VREF Timebase

Temp

&

Voltage

ADC

Current ADC

15 bit + sign

Rate,

Temperature

Compensation

EEPROM

Status

&

Control

Accumulated

Current

EN

SNS VSS

VDD

SCL

PIO

VIN

剩余27页未读,继续阅读

资源评论

benq0000g

- 粉丝: 0

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 使用Java语言编写的九格拼游戏,找寻下曾经小时候的记忆.zip

- gakataka课堂管理系统

- 一个简单ssh(spring springMVC hibernate)游戏网站,在网上找的html模板,没有自己写UI,重点放在java后端上.zip

- 一个采用MVC架构设计、Java实现的泡泡堂游戏.zip

- 一个简易的对对碰游戏软件,运用Java、Java FX技术.zip

- 通过binder实现进程间通讯 ,可以使用service的binder或者 AIDL生成的Stub返回binder 实现demo

- 44f2abdbd6faa9938f9d8e4cace85309.JPG

- 一个简易的躲避子弹飞机小游戏,基于最简单的java ui.zip

- 一个西洋跳棋小游戏,写成桌面Java程序,实现了人机对战,对博弈树的遍历进行了极大极小值的alpha-beta剪枝算法进行优化.zip

- 一些java的小游戏项目,贪吃蛇啥的.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功