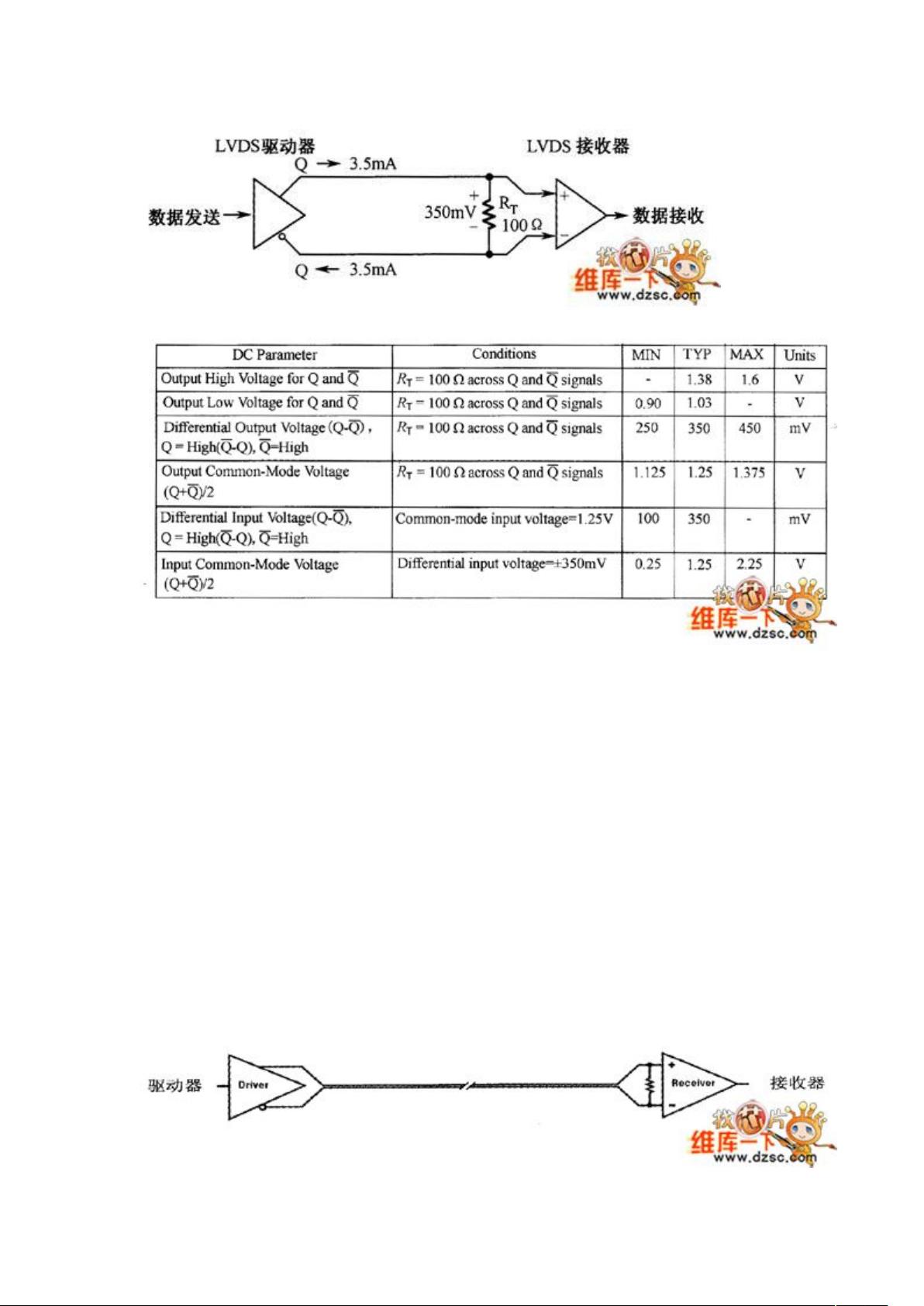

设计高速电路的开发人员对差分线并不陌生,在本章中提到的高速数据通信接口应用的信号线是由差分对组成的,前面几节是从逻辑的角度来说明高速数据通信接口应用。为了让读者更加熟悉高速通信并行接口的差分对信号设计技术,本节从信号的物理特性角度及其PCB设计来说明高速通信并行接口的差分对信号LVDS(Low Voltage Differential Signaling)的原理及应用。 LVDS(Low Voltage Differential Signaling)是一种高速、低功耗的信号传输技术,广泛应用于现代电子设备中的高速数据通信接口。这种技术的核心在于利用一对差分对进行信号传输,即两个极性相反的信号线,它们同时携带信号的正负极性。这种差分模式的传输方式具有诸多优势。 差分传输能够显著增强抗干扰能力。由于信号在一对线上同时传输,外部干扰同时影响两条线路,但接收端关注的是两条线间的电压差,因此干扰被有效地抵消,提高了信号的稳定性。由于差分对的电磁场相互抵消,LVDS产生的电磁干扰(EMI)较低,这对于减少设备间的互相干扰和满足电磁兼容性(EMC)标准至关重要。再者,差分模式还能减少开关噪声的影响,因为每个信号都有独立的返回路径,避免了信号在经过接插件或封装时受到噪声干扰。LVDS在低信号电平下仍能保持良好的接收能力,因为它通过计算差分对的电压差来决定信号,相当于单端信号的两倍,增强了信号的信噪比。 LVDS的DC参数是其性能的重要指标。典型的LVDS信号电压范围在1.125V至1.375V之间,每个驱动器驱动一条传输线。差分阻抗Zdiff是LVDS设计的关键,通常需要根据布线类型(如微带线或带状线)进行定制,以确保信号完整性。匹配电路也是LVDS系统中不可或缺的部分,通常在接收端添加与传输线阻抗相等的终端电阻RT,以消除信号反射。 在实际应用中,LVDS的PCB布线需要遵循特定的设计规则,例如保持差分线对的等长以减少相位偏移(Skew),避免差分线之间的垂直交叉以减小串扰,限制过孔的使用以防止信号质量下降,以及选择合适的线宽和线间距以实现预设的差分阻抗。 LVDS广泛应用于各种高速应用,如视频和数据传输、网络设备、高性能计算机和嵌入式系统。它的低电压和低电流驱动使其在高数据速率下实现了低功耗和低噪声,成为现代高速电路设计中的首选信号传输技术。随着技术的发展,LVDS继续在推动高速通信接口的进步中发挥着重要作用。

剩余7页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功