没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

目 录

第一章 VHDL 简介 ................................................................................................................... 1

1.1 VHDL 的特点 ..................................................................................................................... 1

1.2 VHDL 的设计流程 ............................................................................................................. 1

1.3 VHDL 的基本语法 ............................................................................................................. 2

1.3.1 VHDL 程序的结构 .................................................................................................. 2

1.3.2 数据类型 ................................................................................................................. 3

1.3.3 数据操作 ................................................................................................................. 4

1.3.4 并行赋值语句 ......................................................................................................... 5

1.3.5 进程语句 ................................................................................................................. 5

1.3.6 元件例化 ................................................................................................................. 6

1.3.7 注释 ......................................................................................................................... 7

1.4 结构体描述的三种方法 .................................................................................................... 7

1.4.1 行为描述法设计举例 ............................................................................................. 7

1.4.2 数据流描述法设计举例 ......................................................................................... 8

1.4.3 结构描述法设计举例 ............................................................................................. 9

1.5 VHDL 的电路设计举例 ................................................................................................... 12

1.5.1 组合逻辑电路 ....................................................................................................... 12

1.5.2 触发器(D 触发器) ........................................................................................... 12

1.5.3 分频器电路 ........................................................................................................... 13

1.5.4 锁存器(Latch) .................................................................................................. 14

1.5.5 RAM/ROM 的设计 ............................................................................................. 15

1.6 状态机设计 ...................................................................................................................... 15

1.6.1 概述 ....................................................................................................................... 15

1.6.2 程序举例 ............................................................................................................... 16

第二章 Quartus II 的使用............................................................................................................ 21

2.1 Quartus II 概述 .................................................................................................................. 21

2.1.1 设计的主要环节 ................................................................................................... 21

2.1.2 Quartus II 的主界面 ............................................................................................... 22

2.2 Quartus II 的 VHDL 输入设计流程 ................................................................................. 23

2.2.1 新建工程 ............................................................................................................... 23

2.2.2 新建 VHDL 设计文件 .......................................................................................... 25

2.2.3 功能仿真 ............................................................................................................... 27

2.2.4 编译前的一些设置及全编译 ................................................................................ 30

1

2.2.5 时序仿真 ............................................................................................................... 33

2.2.6 引脚锁定和下载 ................................................................................................... 35

2.3 Quartus II 的原理图输入设计流程 .................................................................................. 37

2.3.1 新建工程和生成元件符号 ................................................................................... 37

2.3.2 新建原理图设计文件 ........................................................................................... 37

2.3.3 全编译和时序仿真 ............................................................................................... 40

1

第一章 VHDL 简介

1.1 VHDL 的特点

随着电子设计技术的高速发展,电路的复杂度越来越高,产品的更新速度越来越快,原

理图输入的方法已经不能满足工业界对设计能力的要求。VHDL(Very High Speed Integrated

Circuit Hardware Description Language)是美国国防部 1983 年提出的一种硬件描述语言,它

可以描述硬件的结构和行为,通过采用 EDA 工具自动综合出电路结构,极大地提高了设计

能力。VHDL 设计方法有以下几个优点:

1. 可以直接描述电路的行为,由 EDA 工具综合出电路,设计速度快。

2. 工艺无关性。设计人员不必过多关心具体的工艺,由 EDA 工具自动针对具体的工

艺综合出电路。同时设计具有非常高的可移植性,这是原理图输入法不可比拟的。

3. 设计文件可读性好

1.2 VHDL 的设计流程

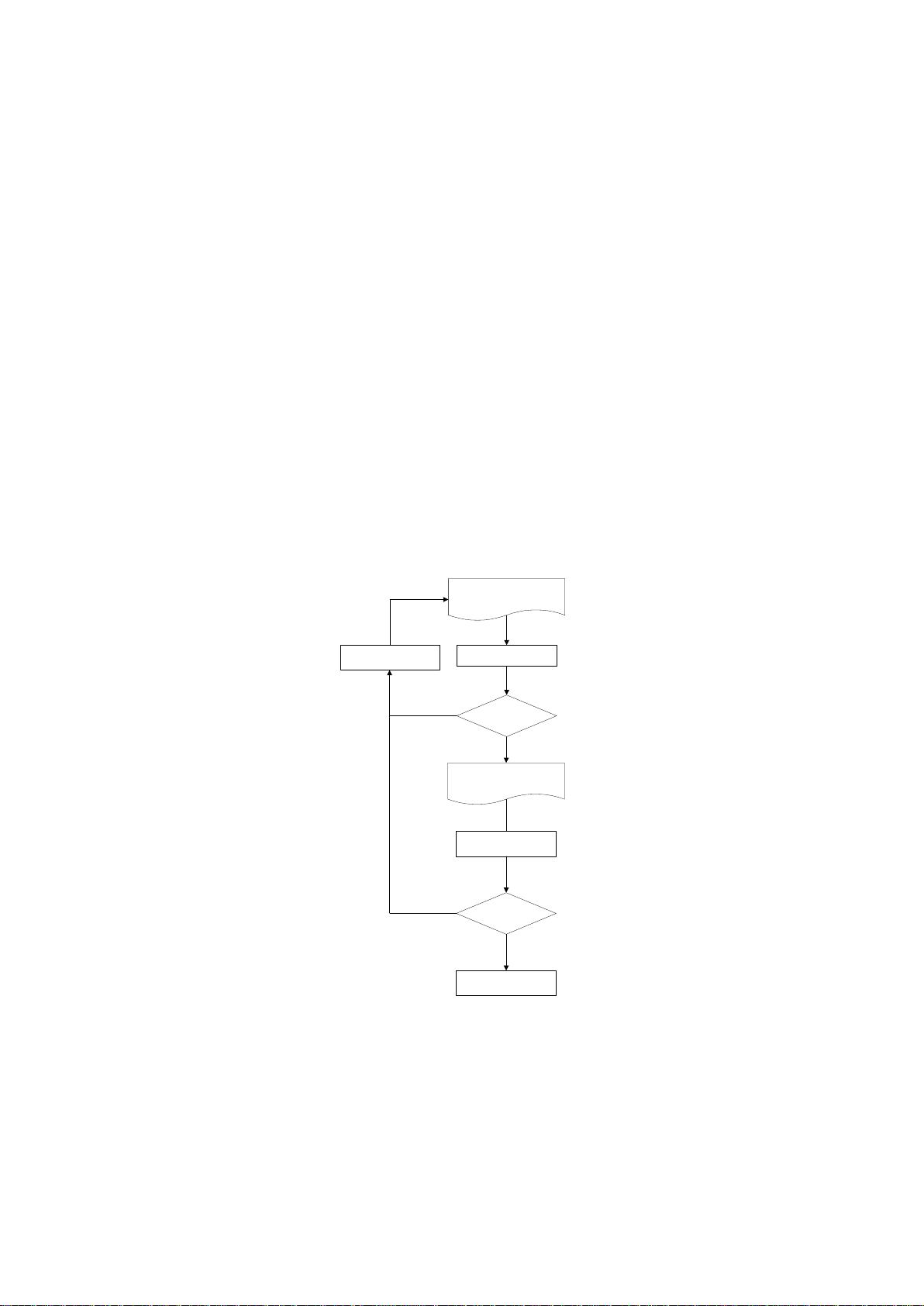

CPLD/FPGA 的 VHDL 设计流程如图 1.2.1 所示。

行为级/RTL级

VHDL代码

综合、布局布线

正确 ?

改正错误

否

仿真

正确 ?

电路拓扑

否

下载到CPLD验证

图 1.2.1 CPLD/FPGA 设计流程

设计流程主要包括以下几步:

1. 写设计文件。按照自顶向下的方法将系统分解为不同的模块,采用行为描述或结构

描述的方法设计各个模块。

2. 综合、布局布线。由 EDA 工具根据具体的 CPLD 工艺,编译设计文件,产生电路

2

结构,并完成布局布线,最后产生可下载到 CPLD 的数据文件。

3. 仿真。在计算机上对 EDA 工具产生的电路进行模拟,验证电路的功能、时序是否

达到设计要求。

4. 下载到 CPLD 验证。仿真验证了设计的功能正确后,最后下载到 CPLD 芯片中,配

合外围电路验证整个系统的功能。

1.3 VHDL 的基本语法

VHDL 语言是一种比较复杂的语言,它可以在不同的抽象层次描述一个电路,这里仅介

绍实验所需要的最基本的语法。

1.3.1 VHDL 程序的结构

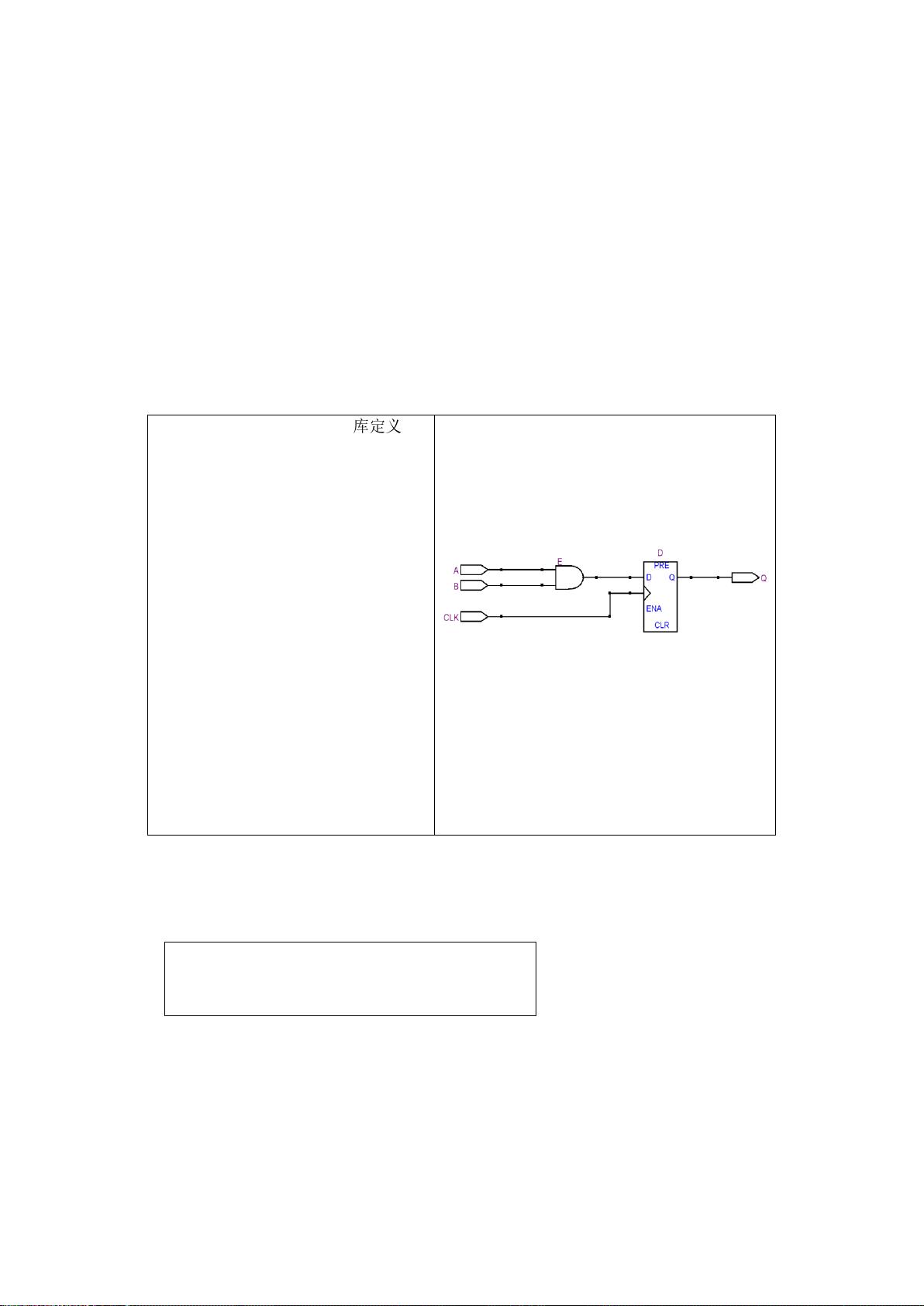

程序举例:

LIBRARY ieee; -- 库定义

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY counter IS -- 实体定义

PORT (

A,B,CLK : in std_logic;

Q : out std_logic );

END;

ARCHITECTURE behav OF counter IS

-- 结构体定义

SIGNAL D, E: std_logic;

BEGIN

E <= A and B;

PROCESS (CLK)

BEGIN

IF CLK‟event and CLK=‟1‟ THEN

D <= E;

END IF;

Q <= D;

END PROCESS;

END behav ;

图 1.3.1 VHDL 程序对应原理图

上例是一个基本的 VHDL 程序,它包括三个基本部分:

1. 库

库类似 C 语言的头文件,在库里定义了一些常用的数据类型、函数等,一般使用以下的

库就够了:

2. 实体

实体定义了电路的端口和输入输出信号的名称、类型、宽度等,语法如下:

LIBRARY ieee; --标准库资源

use ieee.std_logic_1164.all; --标准逻辑程序包

use ieee.std_logic_unsigned.all;

3

实体描述

PORT 端口

说明

ENTITY cout ( ) IS

PORT( A , B : in std_logic;

C : out std_logic_vector(7 downto 0);

Q : inout std_logic );

END;

电路名称

实体描述语句以“ENTITY IS”语句开头“END”语句结尾,中间包含 PORT 端口说

明部分。

关键词解释:

in:输入端口。

out:输出端口。

inout:输入输出双向端口。

std_logic:标准逻辑位数据类型。

std_logic_vector:标准逻辑矢量数据类型。括号内的语句是定义位宽用的,推荐将

位宽写成(M downto N)的方式,用下标 M、N 指明位序。上例中信号 C 就是一个 8 位位

宽的总线端口信号。

3. 结构体

结构体定义了电路的内部结构,包括电路内部的信号,各个模块的结构描述和行为描述,

语法如下:

ARCHITECTURE behave (结构名) OF cout (实体名) IS

SIGNAL E (内部信号) : std_logic;

BEGIN

模块 1

模块 2

……

END;

结构体名由设计者自由命名, OF 后面的实体名称表明该结构体属于那个设计实

体,在同一个设计实体中可能包含多个结构体,用不同的结构体名区分。设计时可以根据结

构体的特色来为每一个命名。例如:

ARCHITECTURE behave OF cout IS 突出结构体的行为特色

ARCHITECTURE dataflow OF cout IS 突出结构体的数据流特色

ARCHITECTURE structural OF cout IS 突出结构体的组织结构特色

ARCHITECTURE bool OF cout IS 突出结构体的数学表达方式特色

„„

结构体中内部信号的定义方式和端口的定义方式类似。比如 1.3.1 节程序中的——

SIGNAL D, E : std_logic ; 语句,两者的区别在于是否有端口定义。

结构体中的模块,实现各种功能。例 1.3.1 节中程序一个是结构描述类型的与门模

块,一个是行为描述类型的 D 触发器模块。

1.3.2 数据类型

VHDL 支持多种数据类型,常用类型有:

1. 9 值逻辑 std_logic

剩余41页未读,继续阅读

资源评论

spenglu

- 粉丝: 26

- 资源: 19

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 足球数据集,10714张图片,pasical voc xml格式 标注,可识别 裁判员,足球,守门员和球员 89.8%的正确识别率

- 基于java+ssm+mysql的课程管理系统 源码+数据库+论文(高分毕设项目).zip

- Java毕业设计-基于SpringBoot+Vue的的农商对接系统的设计与实现(附源码,部署教程).zip

- Java毕业设计-基于SpringBoot+Vue的的失物招领平台的设计与实现(附源码,部署教程).zip

- 基于阶梯式碳交易机制与电制氢的综合能源系统热电优化调度研究:低碳性与经济性并提升购能成本与碳排放成本的综合评估,MATLAB代码 考虑阶梯式碳交易机制与电制氢的综合能源系统热电优化 关键词:碳交易 电

- Java毕业设计-基于SpringBoot+Vue的的论坛系统设计与实现(附源码,部署教程).zip

- Java毕业设计-基于SpringBoot+Vue的物流管理系统(附源码,部署教程).zip

- 基于web的哈密特色展示平台+JavaWeb+哈密瓜宣传、哈密宣传

- 基于java+ssm+mysql的理财通系统 源码+数据库+论文(高分毕设项目).zip

- 基于java+ssm+mysql的课堂管理系统 源码+数据库+论文(高分毕设项目).zip

- 二手摩托车转让合同(修订

- Java毕业设计-基于SpringBoot+Vue的鲜牛奶订购系统的设计与实现(附源码,部署教程).zip

- Java毕业设计-基于SpringBoot+Vue的鲜牛奶订购系统的设计与实现2(附源码,部署教程).zip

- 足球数据集,10714张图片,coco json格式 标注,可识别 裁判员,足球,守门员和球员 89.8%的正确识别率

- 基于java+ssm+mysql的课程在线教学平台 源码+数据库+论文(高分毕设项目).zip

- “锂电池全自动Degas机:EtherCAT总线控制+威纶通触摸屏智能操作,多功能块集成与智能控制解决方案”,锂电池欧姆龙NJ501-1500,威纶通触摸屏程序 全自动锂电池Degas机(抽气封口)

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功