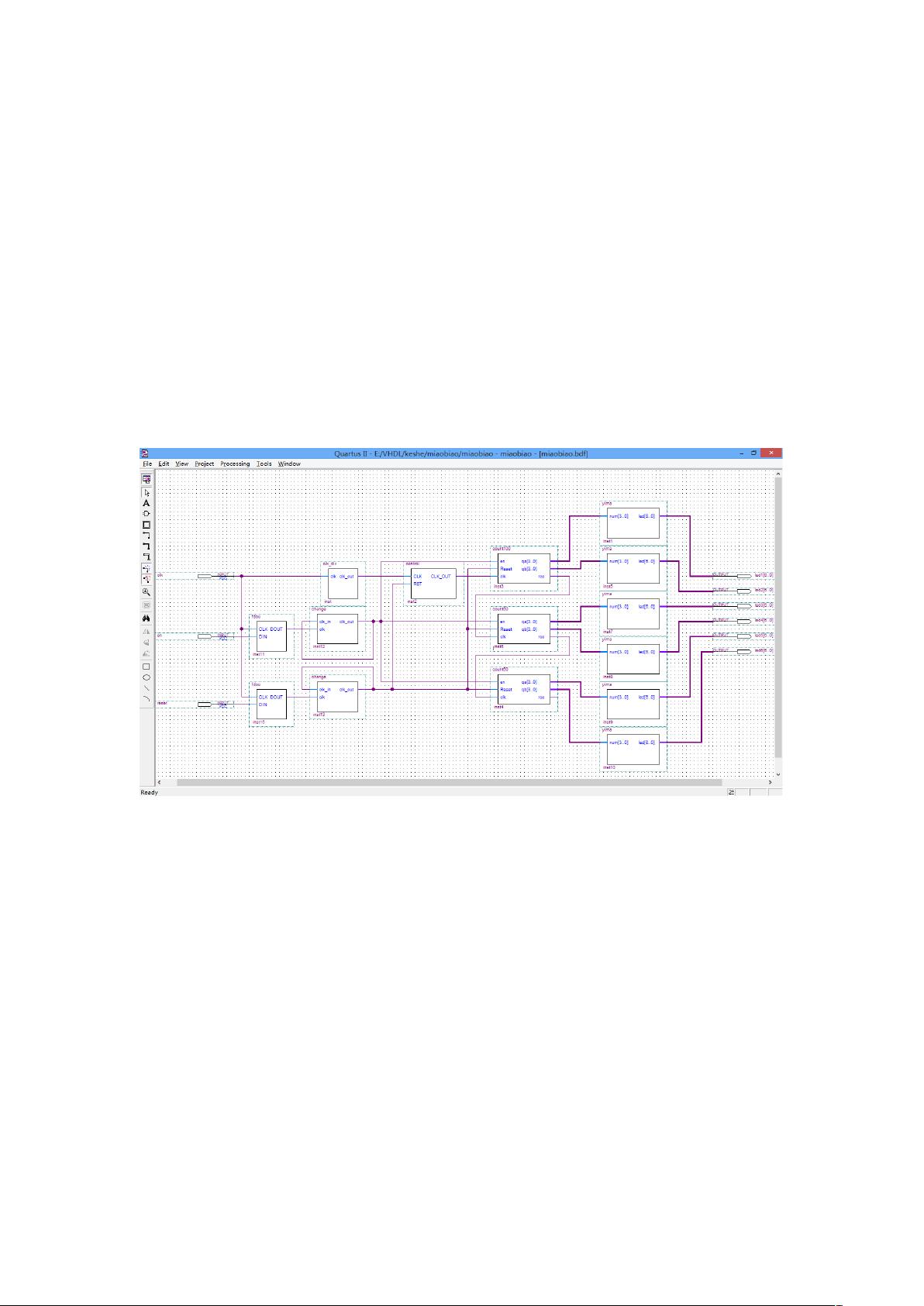

EDA数字秒表的设计 本文旨在介绍EDA数字秒表的设计,包括仿真截图和波形校准。数字秒表是电子设计自动化(EDA)中一个常见的设计项目,旨在设计一个能够精确反映计时时间的数字秒表。 一、系统功能要求 数字秒表的设计主要目标是设计一个能够精确反映计时时间的数字秒表,包括复位、计时功能。秒表1计时的最大范围为 1 小时,精度为 0.01 秒,并可显示计时时间的分、秒、0.1 秒等度量。 1.1 系统功能要求 数字秒表系统功能要求包括: * 显示功能:用6个数码管分别显示分、秒、0.01秒。 * 计时范围:00:00:00 ~ 59:59:99。 * 计时精度:0.01s。 * 启/停开关:具有启/停开关和复位开关功能。 二、总体框图 系统的底层设计主要由六十进制计数器模块、二十四进制计数器模块、分频模块、LED显示模块组成。系统顶层设计图如图所示: 图中左边为三个输入信号en、clk、reset;分为启/停开关、时钟信号和复位开关。主要模块有: * 模60计数器(count60) * 模100计数器(count100) * 分频器(clk_div) * 复位控制(control) * 译码器(yima) * 防抖模块(fdou) * 状态变换模块(change) 右边是六个LED显示输出信号。 三、模块功能设计 模块功能设计包括: * 模60计数器模块与模100计数器模块进行计数。 * 实验室仪器可产生标准2的1kHz的时钟信号,通过分频器模块产生所需的100Hz的时钟信号。 * 复位模块可进行计数器复位操作。 * 译码器是为了将四位二进制信号转换为LED所需的七位二进制编码。 * 防抖模块用于消除用户按键时的抖动消除。 * 状态变换模块是为了用户按键后信号的变换及保持。 四、VHDL 源程序 模60计数器的VHDL 源程序如下: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY count60 IS PORT( en, Reset, clk: in STD_LOGIC; qa: out STD_LOGIC_VECTOR(3 DOWNTO 0); qb: out STD_LOGIC_VECTOR(3 DOWNTO 0); rco: OUT STD_LOGIC); END count60; ARCHITECTURE a OF count60 IS BEGIN process(clk) variable tma: STD_LOGIC_VECTOR(3 DOWNTO 0); variable tmb: STD_LOGIC_VECTOR(3 DOWNTO 0); begin If Reset ='0' then tma:="0000"; tmb:="0000"; elsif clk'event and clk='1' then if en='1' then rco<=tmb(2) and tmb(0) and tma(3) and tma(0); if tma="1001" then tma:="0000"; if tmb="0101" then tmb:="0000"; else tmb:=tmb+1; end if; else tma:=tma+1; end if; end if; qa<=tma; qb<=tmb; end process; END a; 模100计数器的VHDL 源程序如下: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY count100 IS PORT( en, Reset, clk: in STD_LOGIC; qa: out STD_LOGIC_VECTOR(3 DOWNTO 0); qb: out STD_LOGIC_VECTOR(3 DOWNTO 0); rco: OUT STD_LOGIC); END count100; ARCHITECTURE a OF count100 IS ...

剩余15页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Pygame库实现新年烟花效果的Python代码

- 浪漫节日代码 - 爱心代码、圣诞树代码

- 睡眠健康与生活方式数据集,睡眠和生活习惯关联分析()

- 国际象棋检测10-YOLO(v5至v9)、COCO、CreateML、Paligemma数据集合集.rar

- 100个情侣头像,唯美手绘情侣头像

- 自动驾驶不同工况避障模型(perscan、simulink、carsim联仿),能够避开预设的(静态)障碍物

- 使用Python和Pygame实现圣诞节动画效果

- 数据分析-49-客户细分-K-Means聚类分析

- 车辆轨迹自适应预瞄跟踪控制和自适应p反馈联合控制,自适应预苗模型和基于模糊p控制均在simulink中搭建 个人觉得跟踪效果相比模糊pid效果好很多,轨迹跟踪过程,转角控制平滑自然,车速在36到72

- 企业可持续发展性数据集,ESG数据集,公司可持续发展性数据(可用于多种企业可持续性研究场景)

信息提交成功

信息提交成功