GAL16V8

高性能E

2

CMOS PLD

通用阵列逻辑

特性

• 高性能E

2

CMOS®工艺

—最大传输延迟3.5ns

—Fmax=250MHz

—时钟输入到数据输出最大3.0ns

—UltraMOS®先进的CMOS工艺

• 功耗比双极型减少50%到75%

—低功率器件上的Icc典型值为75mA

—1/4功率器件上的Icc典型值为45mA

•对所有引脚有效上拉

• E

2

CEEL工艺

—可重组合逻辑电路

—可重编程单元

—100%测试/100%合格率

—高速电可擦 (<100ms)

—数据保留20年

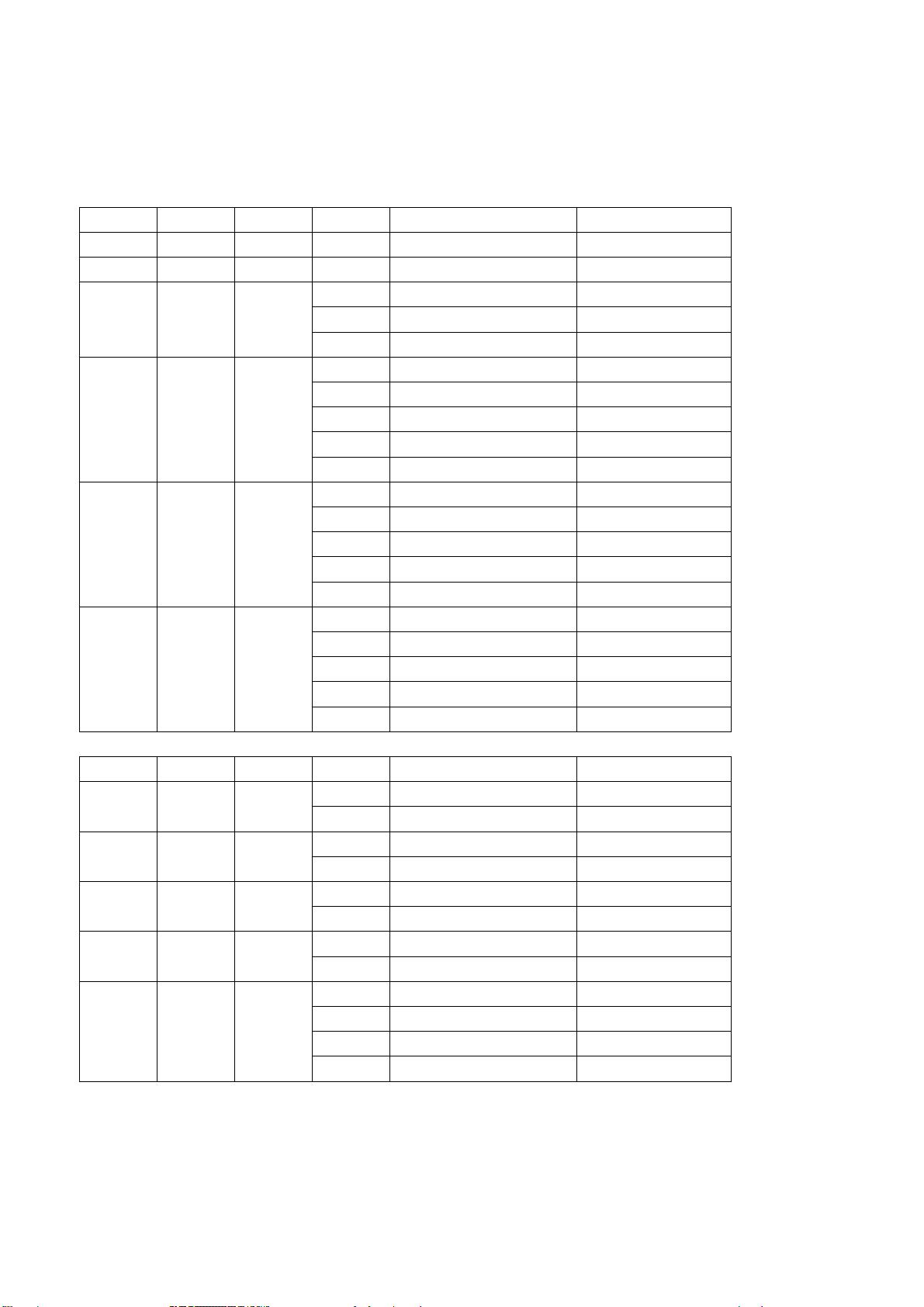

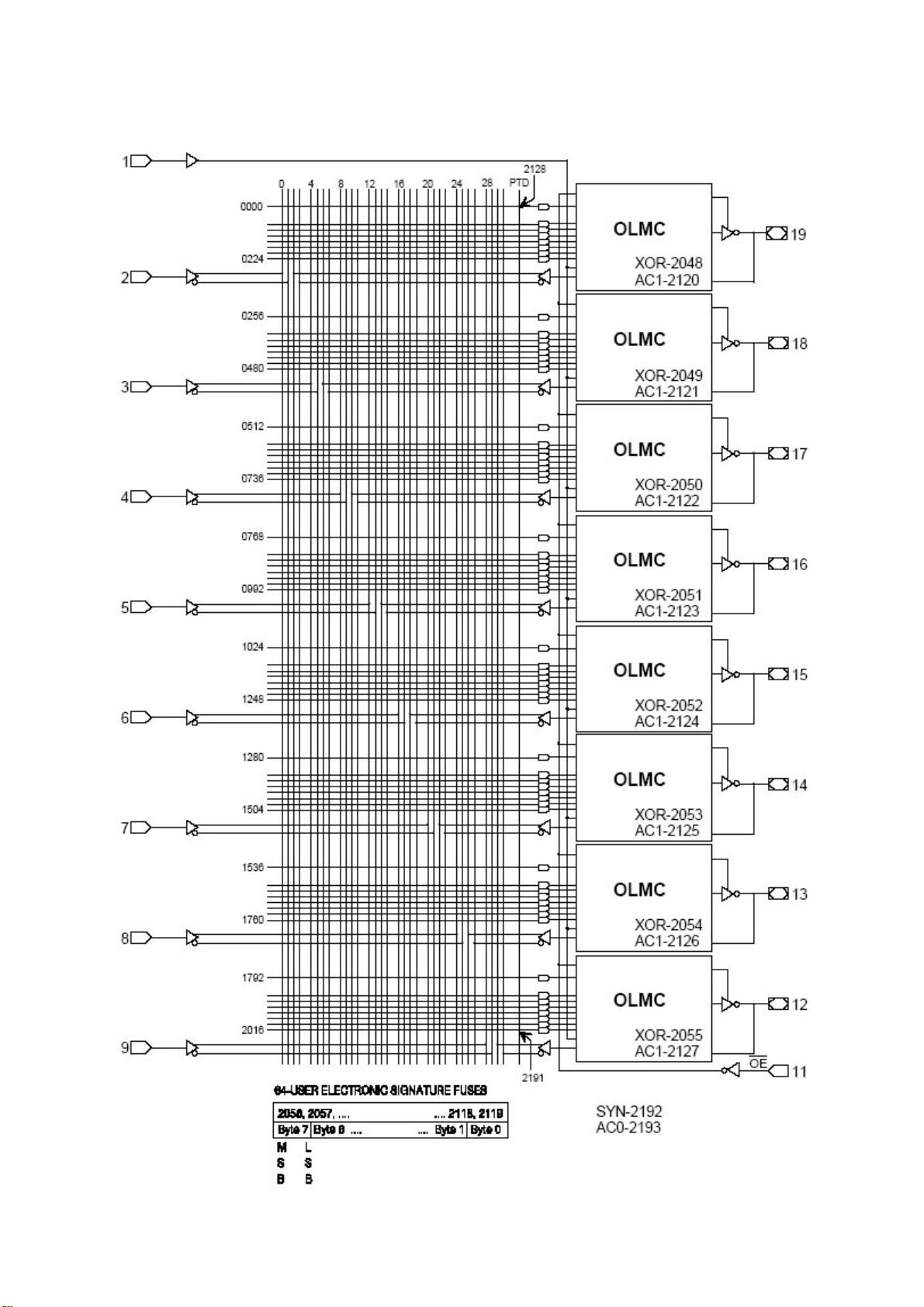

• 8个输出逻辑宏单元

—复杂逻辑设计的最大灵活性

—可编程输出极性

—具有全部功能、熔丝图、参数兼容性的仿真20引

线的PAL®设备

• 所有寄存器的预载和开电源复位

—100%的功能可测性

• 应用包括:

—DMA控制

—状态机控制

—高速图形处理

—标准逻辑速度提升

• 用于识别的电子签名

概述

GAL16V8 以最大 3.5ns的传输延迟时间,结合

高性能的CMOS工艺与电可擦(E

2

)悬浮栅工艺可

为PLD市场提供最高速度的性能。高速擦写时间(<

100ns)允许快速和有效的重复编程。

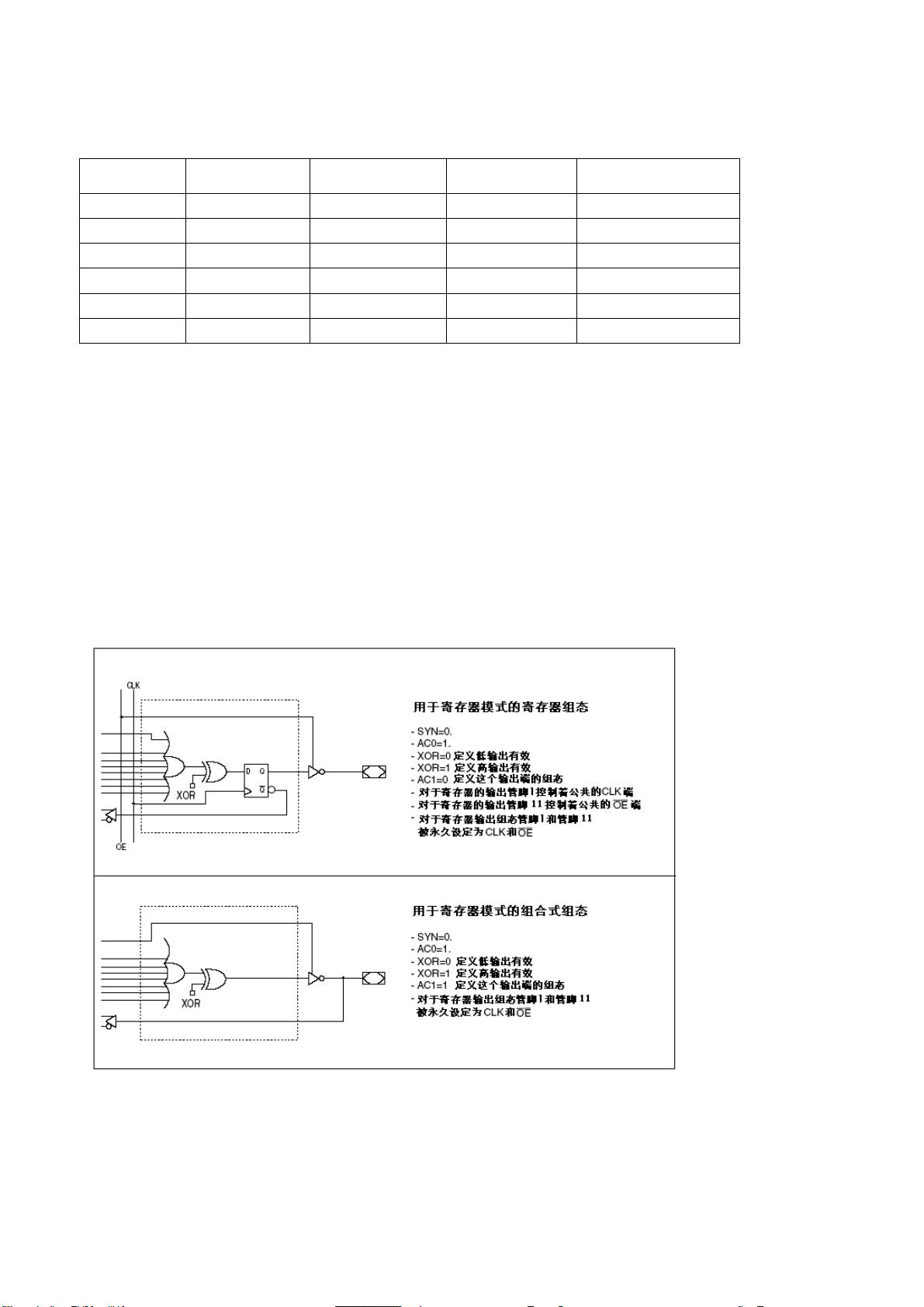

依靠输出逻辑宏单元(OLMC)允许用户来构建,

这种通用的结构提供了最大的设计灵活性。作为

GAL16V8的许多可能结构形式中最重要的一个子

集,PAL结构被列在宏单元描述部分的表里面。

GAL16V8借助于全部功能/ 熔丝图/参数的兼容性

能够仿真任何一种PAL结构。

独特的测试电路和可重复编程的单元使我们

能够在制造期间完成AC、DC和功能测试。

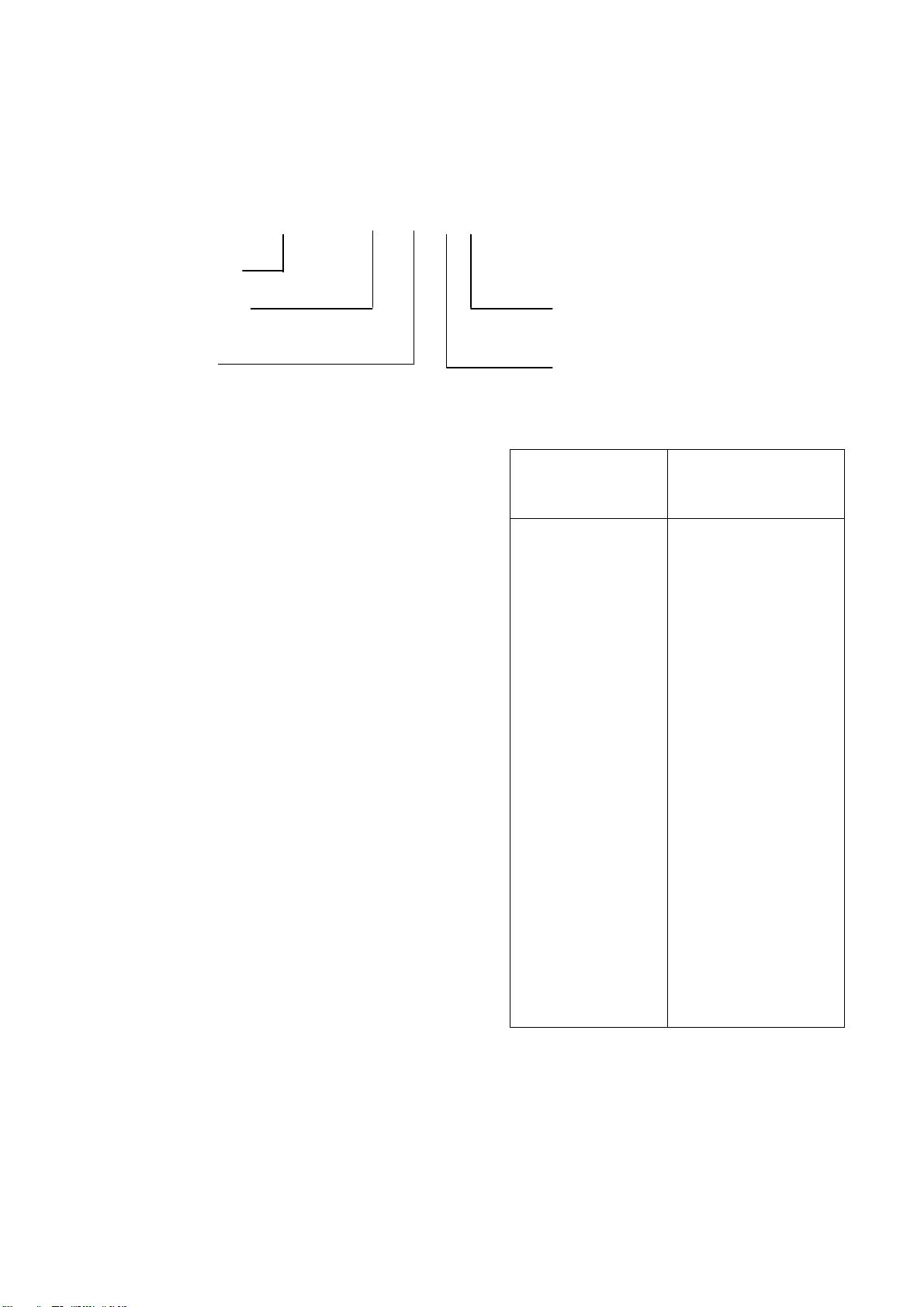

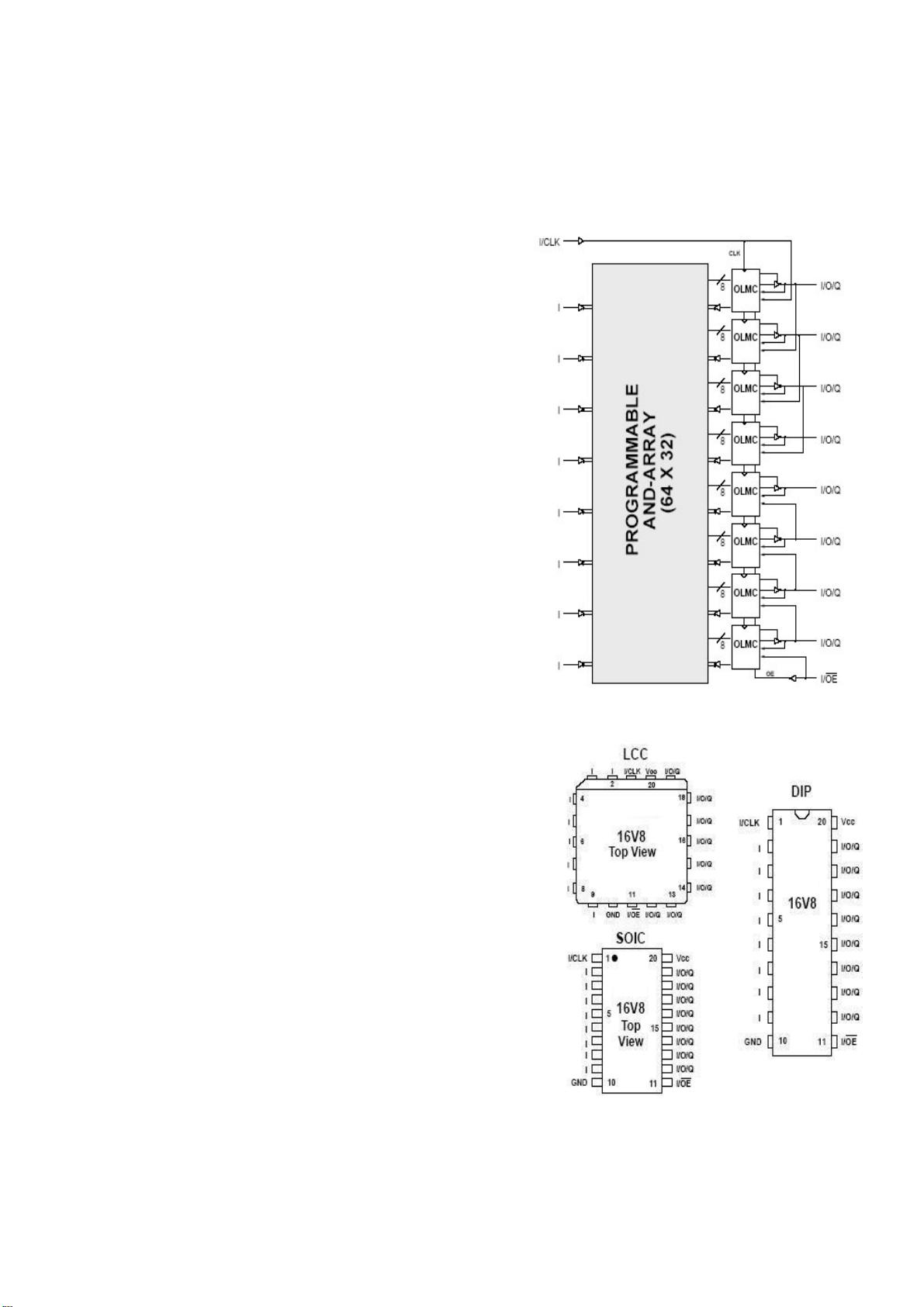

功能方框图

管脚结构