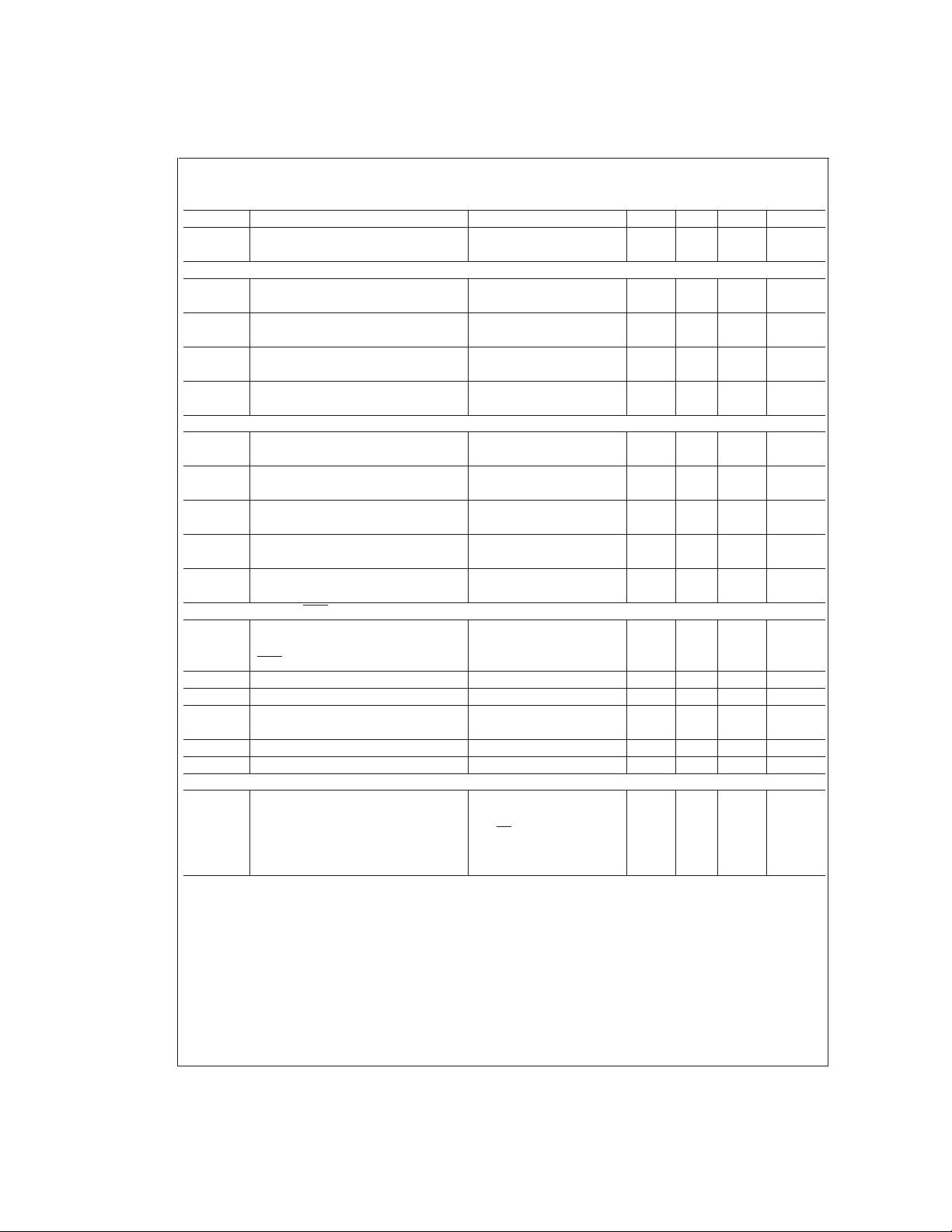

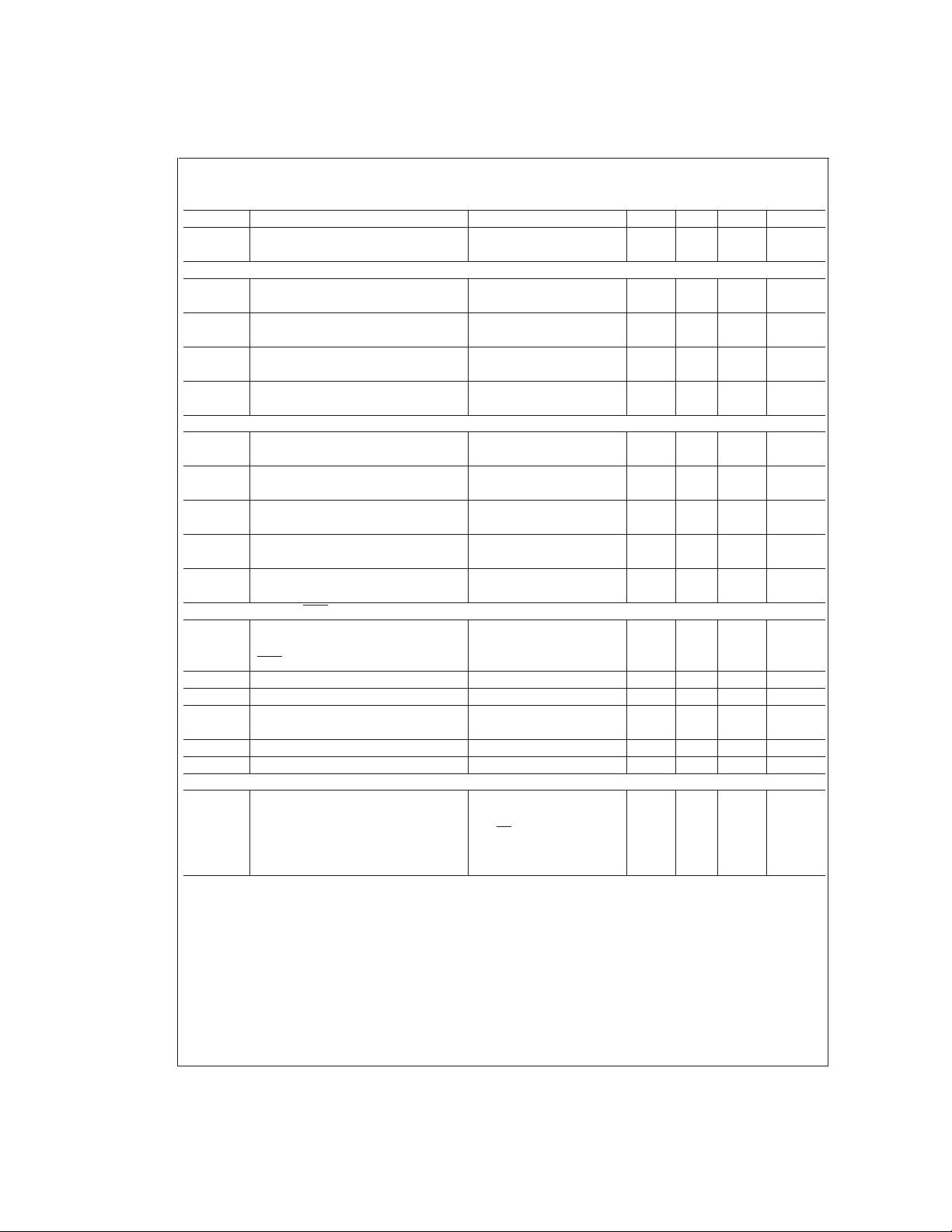

AC Electrical Characteristics (Continued)

The following specifications apply for V

CC

=

5V

DC

and T

MIN

≤T

A

≤T

MAX

unless otherwise specified.

Symbol Parameter Conditions Min Typ Max Units

C

OUT

TRI-STATE Output 5 7.5 pF

Capacitance (Data Buffers)

CONTROL INPUTS [Note: CLK IN (Pin 4) is the input of a Schmitt trigger circuit and is therefore specified separately]

V

IN

(1) Logical “1” Input Voltage V

CC

=

5.25 V

DC

2.0 15 V

DC

(Except Pin 4 CLK IN)

V

IN

(0) Logical “0” Input Voltage V

CC

=

4.75 V

DC

0.8 V

DC

(Except Pin 4 CLK IN)

I

IN

(1) Logical “1” Input Current V

IN

=

5V

DC

0.005 1 µA

DC

(All Inputs)

I

IN

(0) Logical “0” Input Current V

IN

=

0V

DC

−1 −0.005 µA

DC

(All Inputs)

CLOCK IN AND CLOCK R

V

T

+ CLK IN (Pin 4) Positive Going 2.7 3.1 3.5 V

DC

Threshold Voltage

V

T

− CLK IN (Pin 4) Negative 1.5 1.8 2.1 V

DC

Going Threshold Voltage

V

H

CLK IN (Pin 4) Hysteresis 0.6 1.3 2.0 V

DC

(V

T

+)−(V

T

−)

V

OUT

(0) Logical “0” CLK R Output I

O

=

360 µA 0.4 V

DC

Voltage V

CC

=

4.75 V

DC

V

OUT

(1) Logical “1” CLK R Output I

O

=

−360 µA 2.4 V

DC

Voltage V

CC

=

4.75 V

DC

DATA OUTPUTS AND INTR

V

OUT

(0) Logical “0” Output Voltage

Data Outputs I

OUT

=

1.6 mA, V

CC

=

4.75 V

DC

0.4 V

DC

INTR Output I

OUT

=

1.0 mA, V

CC

=

4.75 V

DC

0.4 V

DC

V

OUT

(1) Logical “1” Output Voltage I

O

=

−360 µA, V

CC

=

4.75 V

DC

2.4 V

DC

V

OUT

(1) Logical “1” Output Voltage I

O

=

−10 µA, V

CC

=

4.75 V

DC

4.5 V

DC

I

OUT

TRI-STATE Disabled Output V

OUT

=

0V

DC

−3 µA

DC

Leakage (All Data Buffers) V

OUT

=

5V

DC

3µA

DC

I

SOURCE

V

OUT

Short to Gnd, T

A

=

25˚C 4.5 6 mA

DC

I

SINK

V

OUT

Short to V

CC

,T

A

=

25˚C 9.0 16 mA

DC

POWER SUPPLY

I

CC

Supply Current (Includes f

CLK

=

640 kHz,

Ladder Current) V

REF

/2

=

NC, T

A

=

25˚C

and CS

=

5V

ADC0801/02/03/04LCJ/05 1.1 1.8 mA

ADC0804LCN/LCWM 1.9 2.5 mA

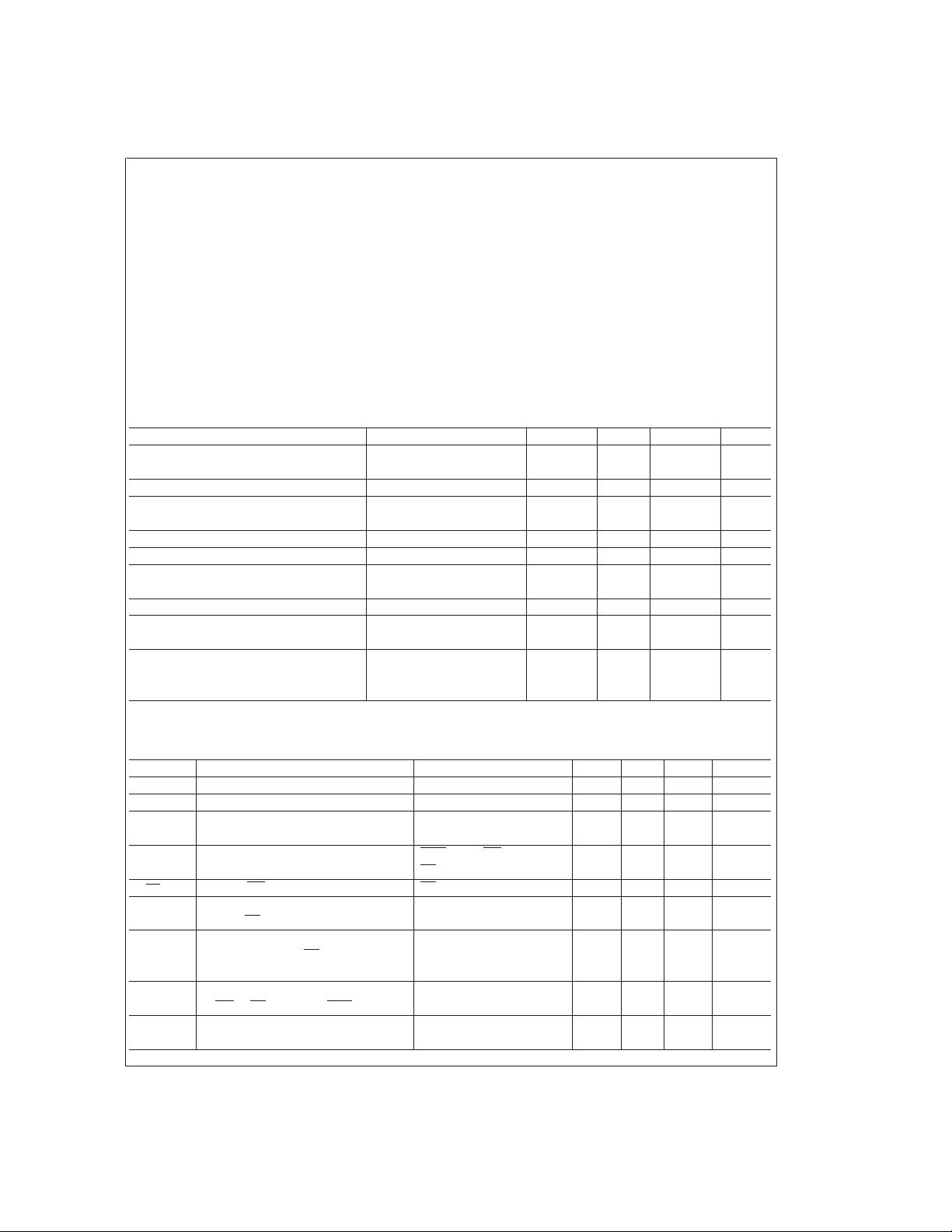

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to Gnd, unless otherwise specified. The separate A Gnd point should always be wired to the D Gnd.

Note 3: A zener diode exists, internally, from V

CC

to Gnd and has a typical breakdown voltage of 7 V

DC

.

Note 4: For V

IN

(−)≥ V

IN

(+) the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input (see block diagram) which will forward conduct

for analog input voltages one diode drop below ground or one diode drop greater than the V

CC

supply. Be careful, during testing at low V

CC

levels (4.5V), as high

level analog inputs (5V) can cause this input diode to conduct–especially at elevated temperatures, and cause errors for analog inputs near full-scale. The spec allows

50 mV forward bias of either diode. This means that as long as the analog V

IN

does not exceed the supply voltage by more than 50 mV, the output code will be correct.

To achieve an absolute 0 V

DC

to5V

DC

input voltage range will therefore require a minimum supply voltage of 4.950 V

DC

over temperature variations, initial tolerance

and loading.

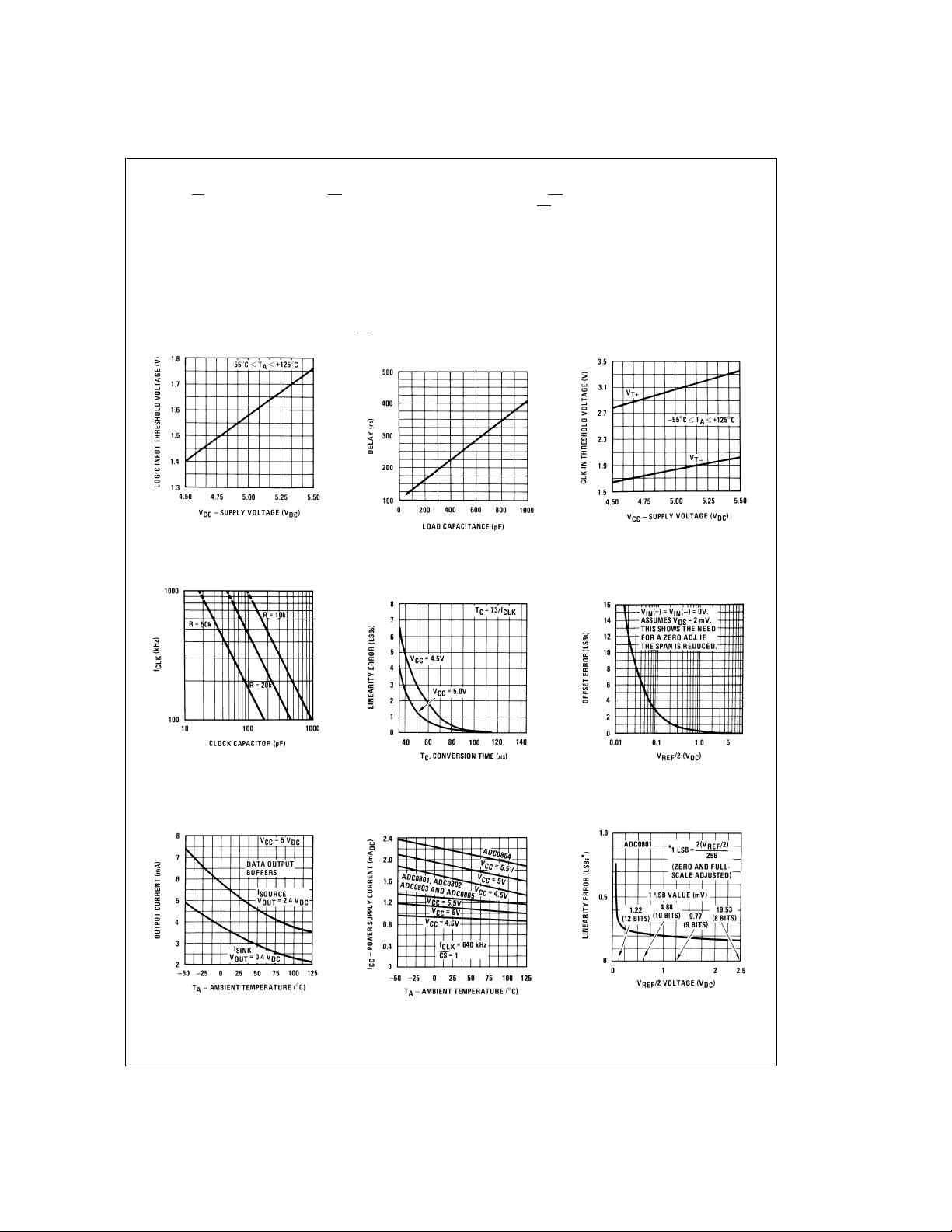

Note 5: Accuracy is guaranteed at f

CLK

=

640 kHz. At higher clock frequencies accuracy can degrade. For lower clock frequencies, the duty cycle limits can be ex-

tended so long as the minimum clock high time interval or minimum clock low time interval is no less than 275 ns.

Note 6: With an asynchronous start pulse, up to 8 clock periods may be required before the internal clock phases are proper to start the conversion process. The

start request is internally latched, see

Figure 4

and section 2.0.

ADC0801/ADC0802/ADC0803/ADC0804/ADC0805

www.national.com 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功