I2C 总线控制器及读写 EEPROM实验内容,适合FPGA初学者

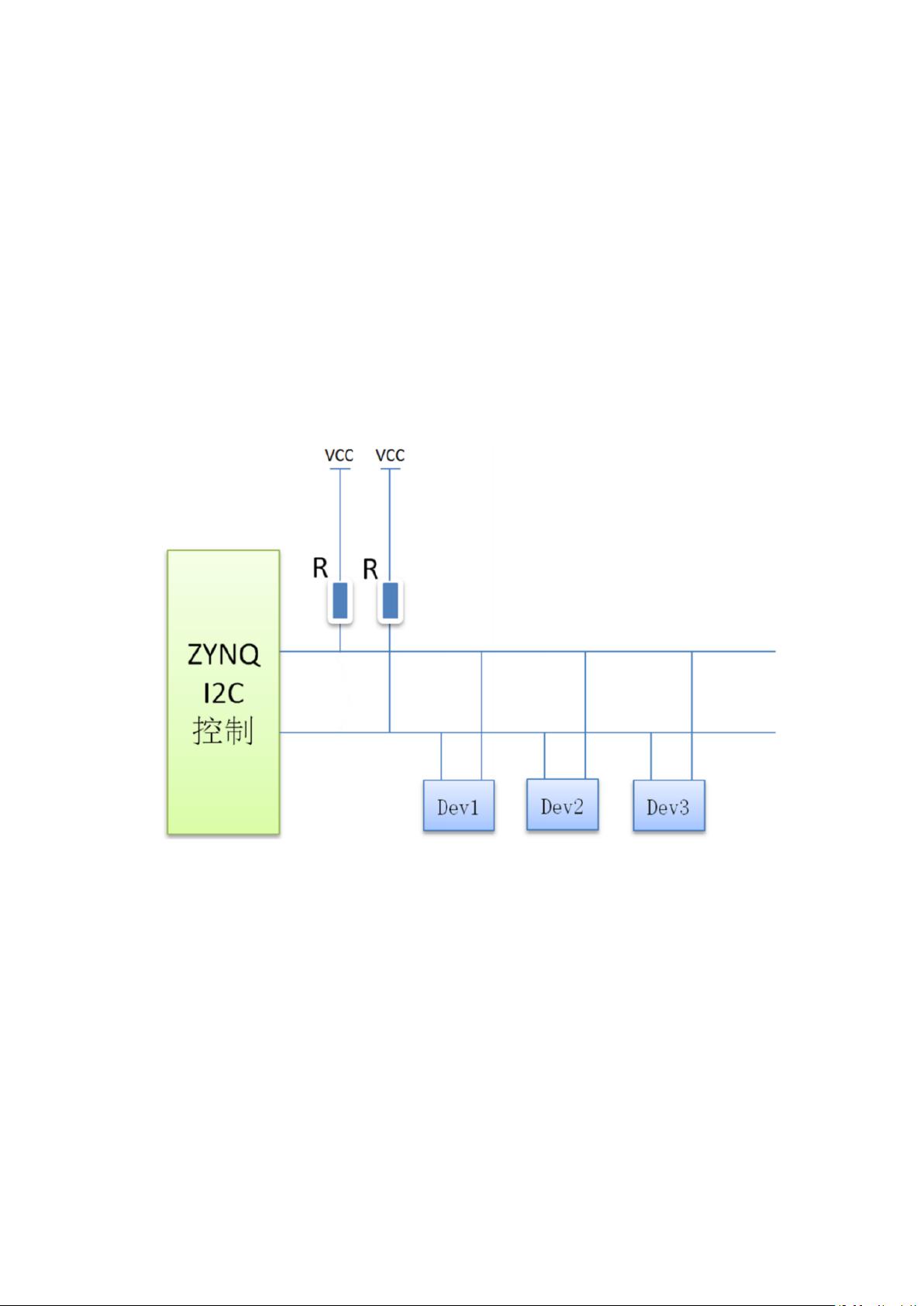

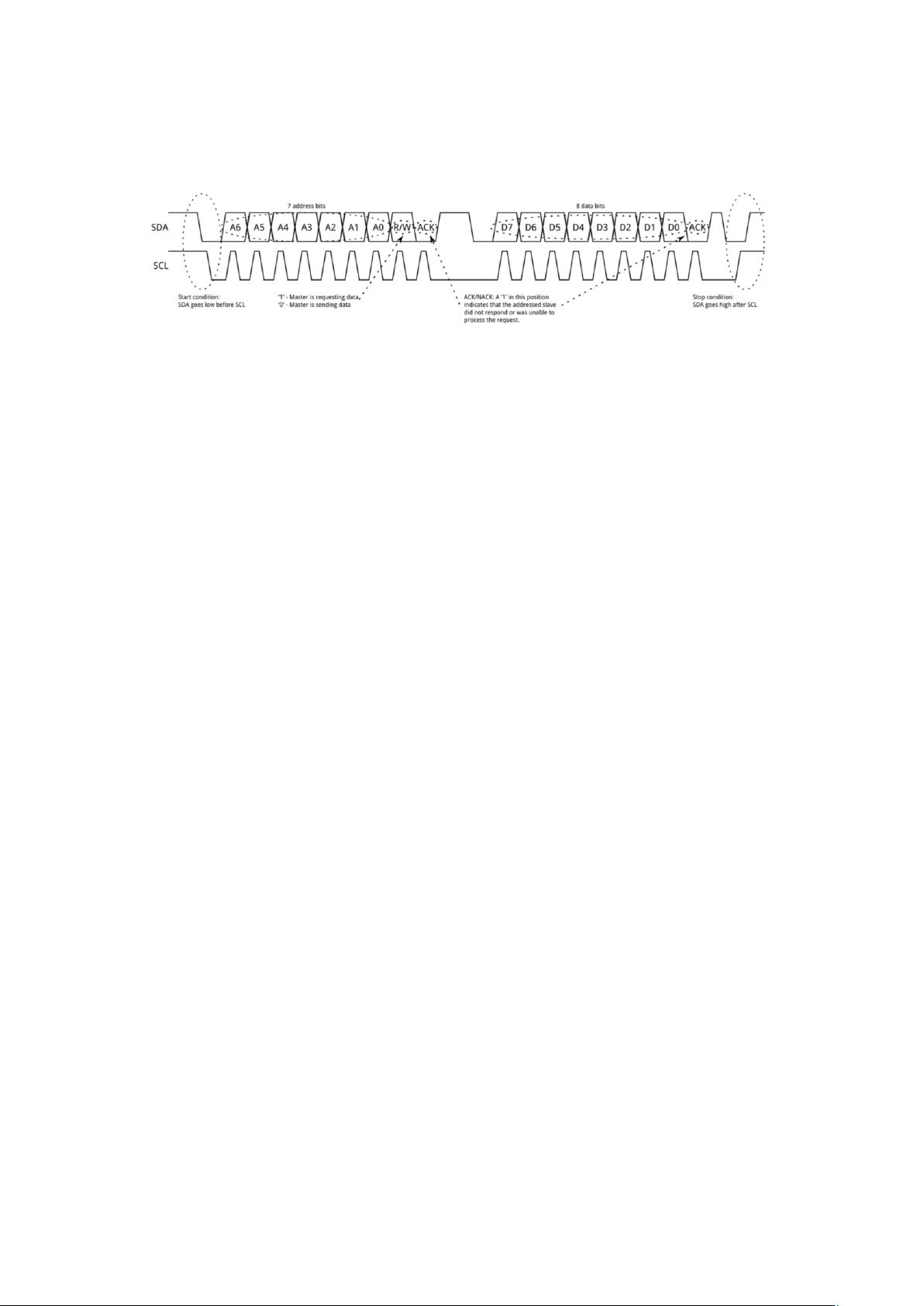

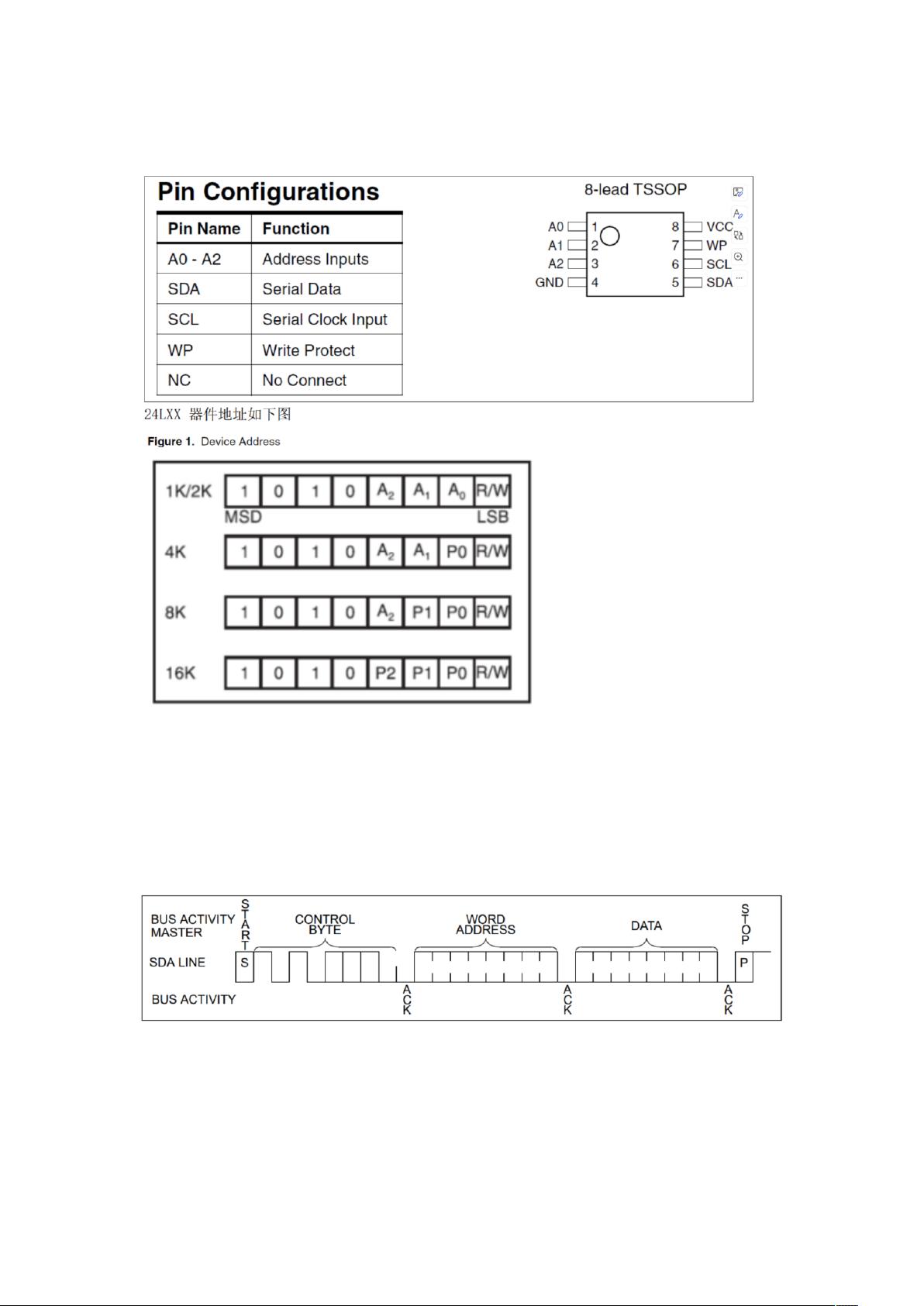

I2C(Inter-Integrated Circuit)总线是由Philips公司开发的一种简单、双向二线制同步串行总线,它只需要两根线(SDA数据线和SCL时钟线)即可在连接于总线上的器件之间传送信息。EEPROM(Electrically Erasable Programmable Read-Only Memory)是一种常见的非易失性存储器,它可以通过I2C总线进行读写操作。 II2C 总线具备广泛的用途,比如寄存器的配置,EEPROM 的使用,更重要的是 I2C 总线上可以挂载非常多的外设。 对于一些低速器件的访问非常节省 IO 资源,由于是标准的总线接口,使用起来非常方便。 ### I2C总线控制器及读写EEPROM详解 #### 一、概述 I2C(Inter-Integrated Circuit)总线是由Philips公司开发的一种简单、双向二线制同步串行总线技术,广泛应用于电子设备间的数据通信。该总线仅需两根线——SDA(数据线)和SCL(时钟线)即可实现器件间的通信。由于其简洁的设计,I2C总线特别适用于FPGA等资源有限的应用场景。 EEPROM(Electrically Erasable Programmable Read-Only Memory)是一种非易失性存储器,常用于保存需要频繁更新的小型数据。通过I2C总线,可以方便地对EEPROM进行读写操作。这种特性使得I2C成为许多嵌入式系统的首选通信协议之一。 #### 二、I2C总线原理 **1. 物理层** - **SDA和SCL**: I2C总线采用开漏输出结构,这意味着SDA和SCL引脚在没有被驱动的情况下呈现高阻态。因此,通常会在总线上添加上拉电阻,确保总线在空闲时保持高电平。 - **上拉电阻**: 上拉电阻的选择对于信号完整性至关重要。一般推荐值为4.7kΩ至10kΩ之间。 **2. 通信协议** - **开始条件**:为了启动一次通信,主控器(Master)会在SCL保持高电平的同时将SDA从高电平拉低。这是所有通信序列的开始标志。 - **地址帧**:每个通信序列的第一个帧为地址帧,其中包含7位的设备地址以及1位读写指示符(R/W)。读写指示符为1时表示读操作,为0时表示写操作。 - **数据帧**:数据帧为8位,每个数据帧传输后都需要一个应答位(ACK/NACK)。 - **应答位**:当数据帧传输完成后,接收方需要返回一个ACK或NACK。ACK(应答确认)表示数据正确接收,NACK(不应答)表示接收失败或其他错误情况。 - **停止条件**:通信结束时,主控器会发出停止条件,即在SCL为高电平时将SDA从低电平拉高。 **3. 数据传输** - **数据格式**:数据传输遵循先高位后低位的原则。每个字节传输完成后,接收方需要发送一个ACK或NACK。 - **时序要求**:数据应在SCL处于低电平时放置到SDA上,并在SCL变为高电平时被采样。 **4. 重复开始条件** - **应用场景**:当主控器需要与同一总线上的不同从机进行连续通信时,可以使用重复开始条件来避免释放总线控制权。 - **操作步骤**:在SCL为低电平时将SDA从低电平拉高,接着将SCL拉高,之后再执行开始条件。 #### 三、读写EEPROM操作 **1. 初始化EEPROM** - **设置地址**:需要通过I2C总线设置EEPROM的地址,以便后续的读写操作能正确定位。 - **配置模式**:某些EEPROM允许配置不同的工作模式,如页模式或字节模式等,这一步骤同样通过I2C总线完成。 **2. 写操作** - **启动条件**:启动I2C总线,发送EEPROM的地址和写指示符。 - **数据帧**:依次发送需要写入EEPROM的数据字节。 - **结束条件**:发送停止条件结束写操作。 **3. 读操作** - **启动条件**:启动I2C总线,发送EEPROM的地址和读指示符。 - **数据帧**:从EEPROM读取数据字节。 - **结束条件**:发送停止条件结束读操作。 #### 四、FPGA设计实现 - **选择合适的库函数**:使用VIVADO2019.2软件,根据Xilinx A7/K7/Z7/ZU/KU系列FPGA的硬件特性,选择合适的库函数。 - **模块化设计**:将I2C总线控制器和EEPROM读写功能设计成独立的模块,便于复用和测试。 - **状态机实现**:利用有限状态机(FSM)来实现I2C通信流程中的各个状态,确保数据的准确传输。 I2C总线因其简单高效的特性而在FPGA项目中有着广泛的应用。通过对I2C总线的工作原理及其与EEPROM的交互方式的理解,可以更好地设计出高效稳定的FPGA系统。

剩余22页未读,继续阅读

- 粉丝: 4632

- 资源: 743

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功