没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

82页

基于FPGA深度学习的Block 模块方案实战,FPGA(中的Block模块是构成FPGA内部结构和功能的基本单元之一。这些Block模块在FPGA中执行各种逻辑、存储和连接功能,使得FPGA能够实现复杂的硬件功能。本文中的包含的实例有ADC/DAC 模块中应用block,CY7C68013A USB2.0 高速采集模块中应用block、视频图像卡图像采集输出中应用block。 本文中包含有详细的verilog代码可供大家参考。

资源推荐

资源详情

资源评论

Block 模块方案实战

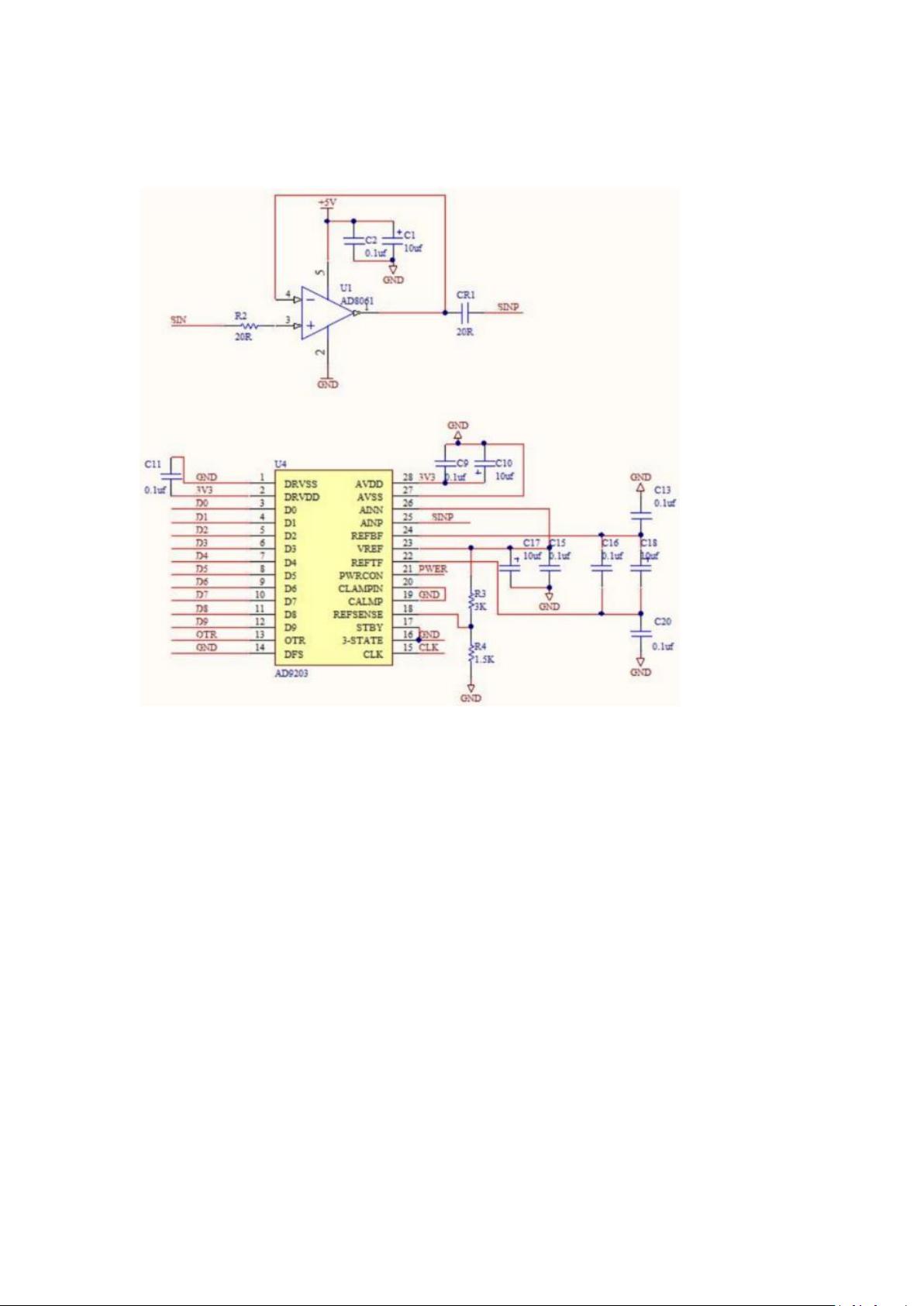

1 ADC/DAC 模块使用实验

1.1 主要硬件参数

(1) -ADC

-AD9203

- 40MHZ 采样速度

-10bit 采样精度

-输入范围 0~3V

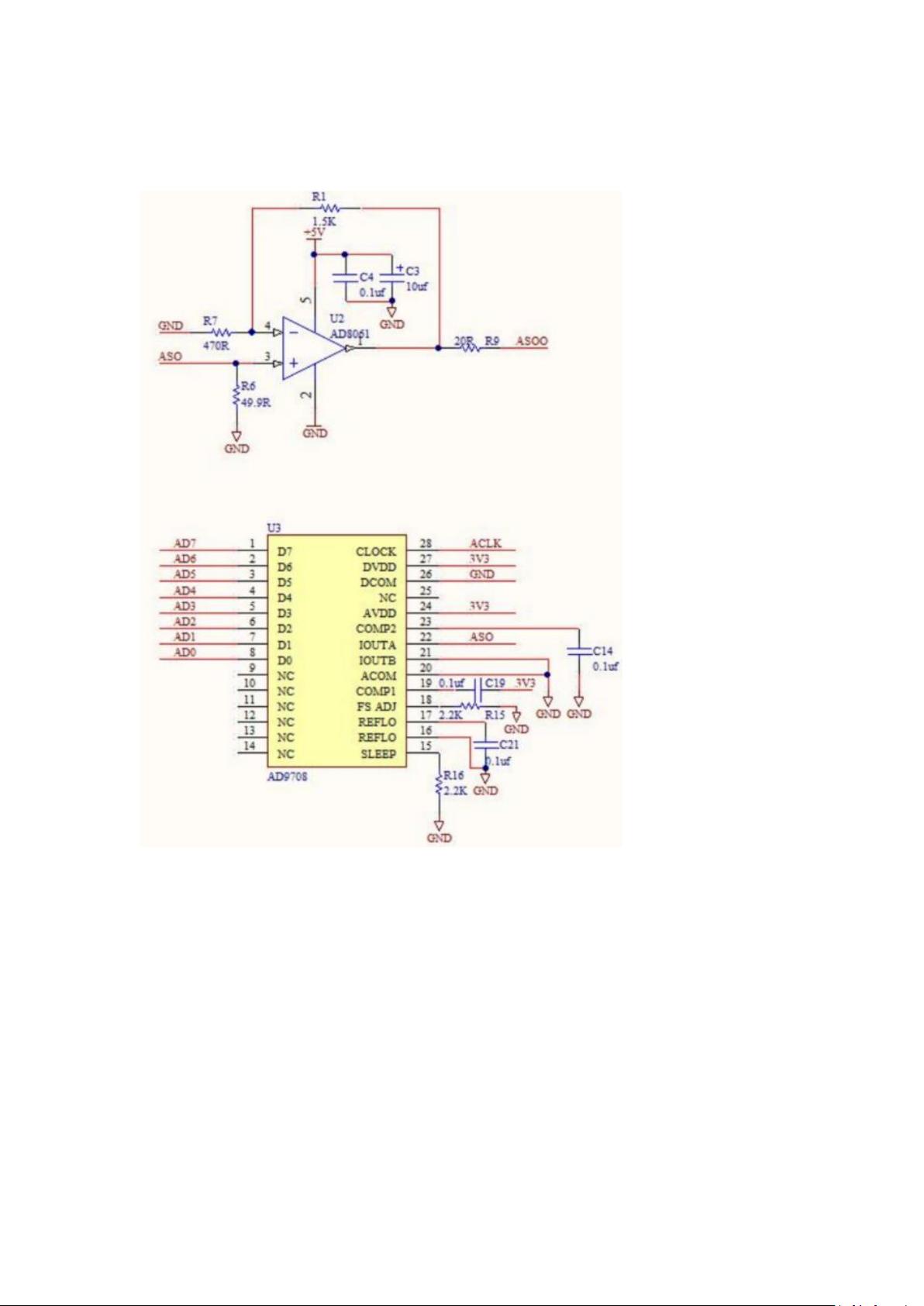

(2) -DAC

- AD9708

-100MHZ 输出

-8bit 输出精度

-输出电压范围 0~3.65V

(3)-电源

-输入 5V

1.2 ADC 部分原理图

1.3 DAC 部分原理图

1.4 基于 FPGA 的高速 ADC DAC 驱动程序设计

DAC AD9708 驱动程序

module AD9708(Clk,AOData,AOClk,AODSet);

input Clk;

output [7:0]AOData;

output AOClk;

input

[7:0]AODSet;

assign AOClk = Clk;

assign AOData = AODSet;

endmodule

ADC AD9203 驱动程序

module AD9203(Clk,ADClk,ADataIn,ADataOut);

input Clk;//系统输入时钟

output ADClk;//ADC 时钟

input [9:0] ADataIn;//ADC 输入数据总线

output [9:0] ADataOut;//ADC 采样数据输出

reg [9:0] ADataOut=0;

reg ADClk = 0;

always @(posedge Clk) ADClk <= ~ADClk;

always @(posedge Clk) begin

if(ADClk) ADataOut <= ADataIn;

end

endmodule

顶层模块中调用了数码管驱动 IP,数码管驱动 IP 请看编程宝典前面讲述。

module main(Clk,Rst,SftClk,LchClk,SDout,SRst,ADClk,ADataIn,AOData,AOClk);

input Clk;

output SftClk;

output LchClk;

output SDout;

output SRst;

input Rst;

output ADClk;//ADC 时钟

input [9:0] ADataIn;//ADC 输入数据总线

output [7:0]AOData;

output AOClk;

reg [3:0] Led4;

reg [3:0] Led3;

reg [3:0] Led2;

reg [3:0] Led1;

reg [6 :0] C2;

reg [9 :0] C3;

reg [13:0] C4;

reg [22:0] C5;

reg [3:0] i ,j , k;

always @(posedge Clk )begin

if(!Rst) begin i <= 4'd0; j <= 4'd0; k <= 4'd0; end

else begin

if( C4 > 14'd999

)begin // 计算 最高位数码管值

if( 1000 *(k + 1 ) <= C4 ) k <= k + 1'b1; else begin Led4 <= k; C3 <= ( C4- 1000*k );

k <= 4'd0; end

end else begin C3 <= C4; Led4 <= 4'd0; end

if( C3 > 10'd99 )begin // 计算 次高位数码管值

if( 100 *(i + 1 ) <= C3 ) i <= i + 1'b1; else begin Led3 <= i; C2 <= ( C3 -100*i );

i <= 4'd0; end

end else begin C2 <= C3; Led3 <= 4'd0; end

if( C2 > 7'd9 )begin

// 计算 次低位数码管值

if( 10 *( j + 1) <= C2 ) j <= j + 1'b1 ;else begin Led2 <= j; Led1<= (C2 - 10*j );

j <= 4'd0;end //计算百位

end else begin Led1 <= C2; Led2 <= 4'd0; end // 计算 最低位数码管值

end

end

wire [9:0] ADataOut;

always @(posedge Clk)

if(!Rst) begin

C4 <= 10'd0;

end

else begin

C4<=ADataOut;

end

reg [7:0]cnt;

reg s =0;

always @(posedge Clk) begin

case (s)

0:begin

if(cnt<254) cnt <= cnt+1; else s <=1;

end

1:begin

if(cnt > 0)cnt <=cnt-1; else s<=0;

end

endcase

end

wire [7 : 0]AODSet;

assign AODSet = cnt;

AD9708 u0(

.Clk(Clk),

.AOData(AOData),

.AOClk(AOClk),

.AODSet(AODSet)

);

AD9203 u1(

.Clk(Clk),

.ADClk(ADClk),

.ADataIn(ADataIn),

.ADataOut(ADataOut)

);

Dpy4 u2(

剩余81页未读,继续阅读

资源评论

icysmile131

- 粉丝: 2632

- 资源: 64

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- TG-2024-05-23-204718255.mp4

- 候志强@181 5428 8938_20240420112107.amr

- spispispispispi

- 实验二:IP协议分析.zip

- 驱动代码驱动代码驱动代码驱动代码

- SVID_20240523_141155_1.mp4

- Code for the complete guide to tkinter tutorial

- 关于百货中心供应链管理系统.zip

- SimpleFolderIcon-master 修改Unity的Project下的文件夹图标

- A python Tkinter widget to display tile based maps

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功