没有合适的资源?快使用搜索试试~ 我知道了~

基于FPGA的1_100s计时器,本计时器包括5个模块:键输入模块、时钟分频模块、开关及控制模块、时钟定时模块、 显示模块,以完成1/100s计时器所界定的功能。

资源推荐

资源详情

资源评论

摘 要

高精度计时器常用于体育竞赛及各种要求有较精确定时的技术领域。通常,采用中

规模集成电路即可实现高精度计时器的设计。

本项研究将基于新一代硬件描述语言(HDL)、采取 ASIC(专用集成电路)设计方法,

实现 1/100s 计时器的前端设计。本计时器包括 6 个模块:消抖模块、时钟分频模块、

控制模块、时钟定时模块、译码模块 、显示模块,以完成 1/100s 计时器所界定的功能。

在键输入模块中,将产生消除抖动后的 reset0(复位脉冲输出)和 on_o0(启/停脉

冲输出)。时钟分频子模块。clk_div 实际上是一个用计数器进行分频的分频电路,得到

用于计时的 100Hz 脉冲信号和消除抖动的 25Hz 脉冲信号。控制子模块是根据计时器

的工作状态,控制是否输出计数允许信号 enable,它用于控制计数子模块的计数工作。

计时子模块是一个定时计数器,用来产生要显示的 5 位计时信息,当使能信号 enable

有效时计数器开始有效计数。计时器显示模块的输入信号为计时模块输出的计时信息;

它的输出信号是 choose 和 segment,驱动用于计时显示的 5 个 LED 七段显示数码管。

在输出信号中,由于五进制计数器循环计数,LED 七段显示数码管循环点亮来显示计时

器的计时输出。

对各个功能模块进行硬件描述以后,然后采用新一代可编程逻辑器件开发软件平台

Quartus II,进行逻辑功能仿真与时序验证,并在 FPGA 开发板上进行了综合和适配。

关键词:计数器;硬件描述;电子设计自动化;集成电路设计;仿真

I

目 录

1.方案比较与选择...............................................................................................................................................1

方案一; 基于 51 单片机设计的数字秒表..........................................................................................................1

方案二: 基于 FPGA 的数字秒表的设计............................................................................................................3

2.底层文件仿真与分析................................................................................................................................ ..............7

2.1 消抖模块...........................................................................................................................................................7

2.2 时钟分频模块...................................................................................................................................................8

2.3 控制模块的时序仿真.......................................................................................................................................8

3.顶层文件仿真与分析........................................................................................................................... ..............12

4.硬件验证分析.......................................................................................................................................... ..............13

5.课程设计心得.......................................................................................................................................... ..............15

ABSTRACT............................................................................................................................................ .................16

参考文献..................................................................................................................................................... ..............17

附录(源代码):..................................................................................................................................... ..............18

顶层文件:..............................................................................................................................................................18

分频模块:...........................................................................................................................................................20

消抖顶层模块:...................................................................................................................................................21

消抖:

...............................................................................................................................................................22

控制模块:...........................................................................................................................................................23

计时顶层模块:...................................................................................................................................................24

计小秒:

...........................................................................................................................................................26

计秒:

...............................................................................................................................................................27

计分:

...............................................................................................................................................................28

译码顶层模块:...................................................................................................................................................29

译码:

...............................................................................................................................................................30

显示模块:...........................................................................................................................................................31

II

1.方案比较与选择

方案一; 基于 51 单片机设计的数字秒表

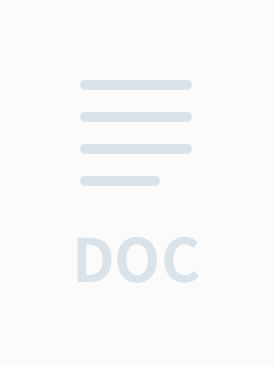

用 AT89C51 设计一个 6 位的数码管显示作为“秒表”,计时精度达到 0.01 秒。利用

其定时器的原理,数码管以及定时器中断来设计计时器。将软硬件结合起来,使得系统

能实现 0 分 00 秒~1 分 59 秒的计时。另外,通过独立按键的设计来对秒表进行控制。

key1 键控制计时的开始与暂停、key2 键控制计时时的保存数据然后可以通过 key4 键

控制数据的输出(可以保存十个,保存十个时秒表可以停止,该功能可用于赛跑中的计

时)、key3 键控制“清零”和保存按下清零键前的最后一次所计时间。每次处于“暂停状

态”的时间都可以在此基础之上进行计时。

硬件部分:

DB2

DB3

DB4

DB5

DB6

DB7

DB1

DB8

CSDA

INT1

D0

D1

D2

D3

D4

D5

D6

D7

SDA

SCL

18B20

CSUSB

DIOLA

DULA

WELA

ALE

LCDEN

LCDEN

RS

RS

RW

WR

RD

RD

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

DIOLA

D1

D2

D3

D4

D5

D6

D7

D0 a

b

c

d

e

f

g

h

DULA

D1

D2

D3

D4

D5

D6

D7

WE2

WE3

WE4

WE5

WE6

CSAD

WELA

a

b

c

d

e

f

g

h

WE1

WE2

WE3

WE4

WE5

WE6

P3.0

P3.1

XTAL2

18

XTAL1

19

ALE

30

EA

31

PSEN

29

RST

9

P0.0/AD0

39

P0.1/AD1

38

P0.2/AD2

37

P0.3/AD3

36

P0.4/AD4

35

P0.5/AD5

34

P0.6/AD6

33

P0.7/AD7

32

P1.0/T2

1

P1.1/T2EX

2

P1.2

3

P1.3

4

P1.4

5

P1.5

6

P1.6

7

P1.7

8

P3.0/RXD

10

P3.1/TXD

11

P3.2/INT0

12

P3.3/INT1

13

P3.4/T0

14

P3.7/RD

17

P3.6/WR

16

P3.5/T1

15

P2.7/A15

28

P2.0/A8

21

P2.1/A9

22

P2.2/A10

23

P2.3/A11

24

P2.4/A12

25

P2.5/A13

26

P2.6/A14

27

U1

AT89C52

X1

CRYSTAL

C1

30pF

C2

30pF

2

3

4

5

6

7

8

9

1

RP1

10K

D0

2

D1

3

D2

4

D3

5

D4

6

D5

7

D6

8

D7

9

Q0

19

Q1

18

Q2

17

Q3

16

Q4

15

Q5

14

Q6

13

Q7

12

LE

11

OE

1

U2

74HC573

D1

LED-RED

D2

LED-RED

D3

LED-RED

D4

LED-RED

D5

LED-RED

D6

LED-RED

D7

LED-RED

D8

LED-RED

2

3

4

5

6

7

8

9

1

RP2

1K

D0

2

D1

3

D2

4

D3

5

D4

6

D5

7

D6

8

D7

9

Q0

19

Q1

18

Q2

17

Q3

16

Q4

15

Q5

14

Q6

13

Q7

12

LE

11

OE

1

U3

74HC573

D0

2

D1

3

D2

4

D3

5

D4

6

D5

7

D6

8

D7

9

Q0

19

Q1

18

Q2

17

Q3

16

Q4

15

Q5

14

Q6

13

Q7

12

LE

11

OE

1

U4

74HC573

C4

1uF

R7

10k

共阴极数码管

图 1.1.1 硬件图

1

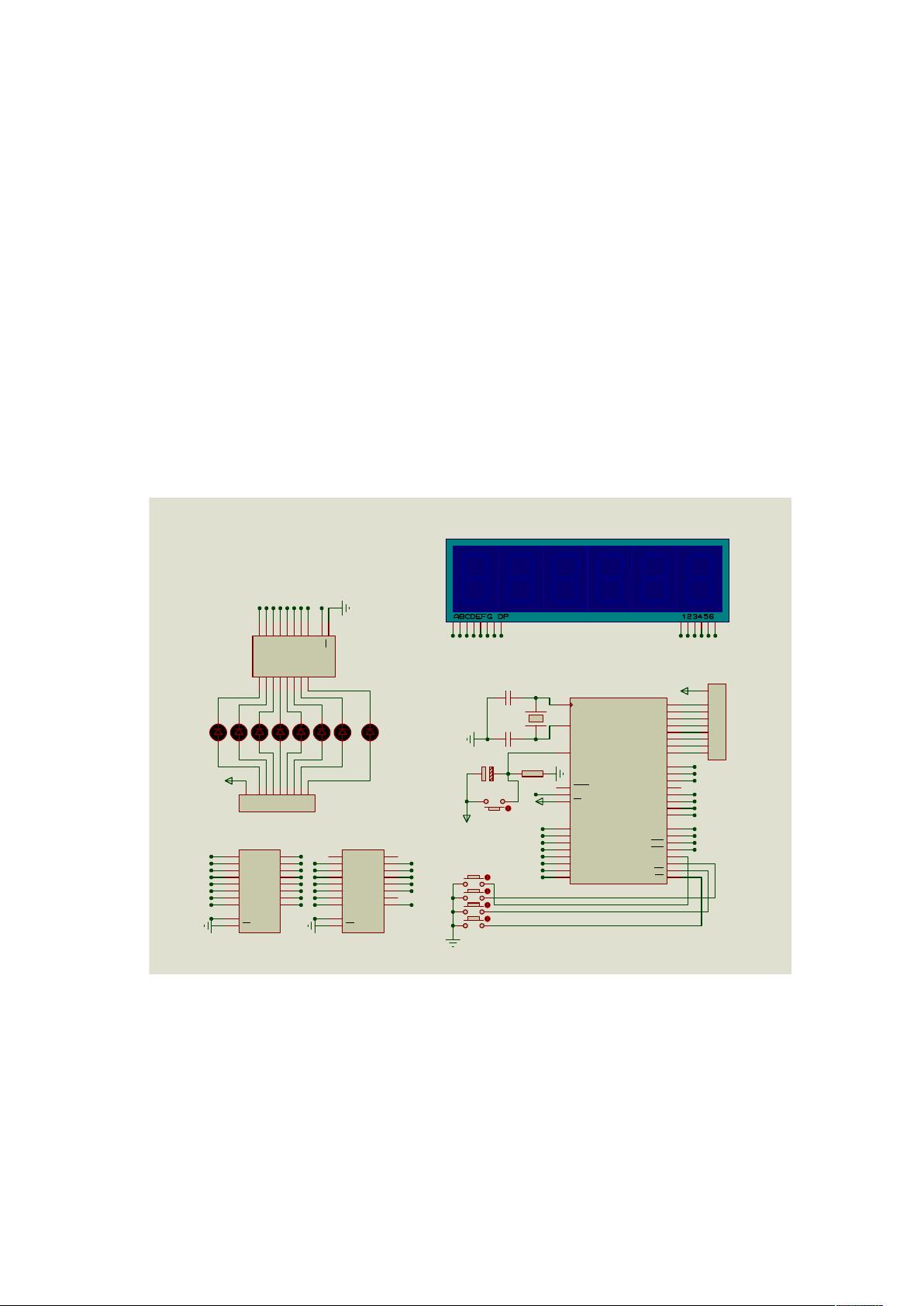

按键 key1 按键 key3 按键 key4

按键 key2

计时开始与暂停

显示 key2 保存的时间清零并保留清零时的时间

按一次保存一个时间

单片机实现流程图:

图 1.1.2 单片机实现流程图

优点:1、C 语言程序的编写比较简单、易懂

2、整个平台的开发、设计成本较低

3、易于排查设计中存在的相关问题

缺点:1、单片机的晶振频率不高,采用延时函数计时误差较大

2、用单片机制作的主控板受制版工艺、布局结构、器件质量等因素的影响

导致抗干扰能力差

3、对环境依赖性强,开发周期长。一个采用单片机制作的主控板不经过很长

时间的实际验证很难形成一个真正的产品。

初始化函数

程序开始

选择按键

上电

2

方案二: 基于 FPGA 的数字秒表的设计

通过分频器将晶振所提供的信号分频成 0.01S 脉冲作为计时信号,经计数器累加计

数,形成一百进制的计数器,六十进制的计数器。经译码器译码后,分位输出给五个 7

段 LED 数码管显示。 设计采用五位 LED 数码管显示 min、10s、1s,0.1s,0.01s 计

时方式。使用按键开关可实现开始/结束计时操作,及复位清零操作和计时长度模式选

择。

采用自顶向下的设计思路,本计时器包括 6 个模块:消抖模块、时钟分频模块、开

关及控制模块、时钟定时模块、译码模块、 显示模块,以完成 1/100s 计时器所界定的

功能。

各模块详细说明:

(1)消抖模块(xiaodou):该子模块的输入信号是 reset、on_o 和 clk1。输出信

号是 reset0(复位脉冲输出)和 on_o0(启/停脉冲输出)。每按一下 reset 开关的按钮,

reset0 输出端将输出一个脉冲宽度为一个时钟周期(lms)的复位脉冲。每按一下 on_o

开关的按钮,on_o0 输出端将输出一个脉冲宽度为 1ms 的启/停控制脉冲。这两种脉

冲产生电路的结构是完全一致的,唯一应注意的是两种电路都应采取防抖动措施。

(2)时钟分频模块(div):时钟分频模块分为两部分,第一部分使用 clk_div50 子模

块将外部 3MHz 的时信号分频为 1000Hz 并且占空比为 50 的时钟信号。第二部将

clk_div50 所产生的 1000Hz 的时钟信号经过分频得到用于消除抖动 250Hz 的脉冲信

号 clkl 和用于定时计数的 100Hz 的脉冲信号 clk0。1000Hz 时钟信号经 10 次分频后

得到作为计数脉冲 clk0 输出的 100Hz 时钟脉冲信号. 1kHz 的 clk 经 4 次分频在即可得

到 250Hz 的 clkl 输出。由此可知,clk_div 子模块实际上是一个用计数器进行分频的

分频电路,其结构和输入输出信号关系如图 2-4 所示。为实现严格的同步,该模块采用

同步计数电路。

3

剩余33页未读,继续阅读

资源评论

u011032299

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 仙岭小学结构建模revit

- 第6章习题参考答案.zip

- BeautifyAPP的产品设计(论文+源码)_kaic.zip

- 俄罗斯方块游戏系统的设计与实现(源码+论文)_kaic.zip

- 仓库管理系统的设计与实现(论文+源码)_kaic.zip

- 基于BC模式的电商平台的设计与实现(论文+源码)_kaic.zip

- 基于C#的超市收银管理系统设计与实现(论文+源码)_kaic.zip

- 妇幼保健信息管理系统设计(论文+源码)_kaic.zip

- 基于Java技术的养生知识管理系统设计与实现(论文+源码)_kaic.zip

- 基于springboot框架的高校就业管理系统设计与实现(论文+源码)_kaic.zip

- 基于web的电影购票管理系统的设计与实现(论文+源码)_kaic.zip

- ssm149学生成绩管理系统+vue.rar

- 深度报告:CPU研究框架.pdf

- Freertos-freertos

- BootstrapAdmin-c#

- XTools-idea

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功